CN100539039C - 集成工艺调制一种利用hdp-cvd间隙填充的新型方法 - Google Patents

集成工艺调制一种利用hdp-cvd间隙填充的新型方法 Download PDFInfo

- Publication number

- CN100539039C CN100539039C CNB2007100902636A CN200710090263A CN100539039C CN 100539039 C CN100539039 C CN 100539039C CN B2007100902636 A CNB2007100902636 A CN B2007100902636A CN 200710090263 A CN200710090263 A CN 200710090263A CN 100539039 C CN100539039 C CN 100539039C

- Authority

- CN

- China

- Prior art keywords

- deposition

- etching

- substrate

- chamber

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/04—Coating on selected surface areas, e.g. using masks

- C23C16/045—Coating cavities or hollow spaces, e.g. interior of tubes; Infiltration of porous substrates

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/30—Deposition of compounds, mixtures or solid solutions, e.g. borides, carbides, nitrides

- C23C16/40—Oxides

- C23C16/401—Oxides containing silicon

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/50—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating using electric discharges

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/56—After-treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32431—Constructional details of the reactor

- H01J37/32458—Vessel

- H01J37/32477—Vessel characterised by the means for protecting vessels or internal parts, e.g. coatings

- H01J37/32495—Means for protecting the vessel against plasma

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02164—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon oxide, e.g. SiO2

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/02274—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition in the presence of a plasma [PECVD]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

- H01L21/31116—Etching inorganic layers by chemical means by dry-etching

Abstract

本发明公开了一种用于在设置于工艺腔室内的衬底上沉积氧化硅薄膜的工艺。将包括卤素源、流动气体、硅源和氧化气体的工艺气体流入工艺腔室中。具有离子密度至少为1011离子/厘米3的等离子体由上述工艺气体形成。在衬底上形成具有卤素浓度低于1.0%的氧化硅薄膜。利用同时具有沉积和溅射成分的工艺的等离子体沉积氧化硅薄膜。进入腔室的卤素源的流速和进入腔室的硅源流速之比基本为0.5和3.0之间。

Description

相关申请的交叉引用

本发明要求享有在2006年4月17日提交的发明名称为“INTEGRATEDPROCESS MODULSTION(IPM)A NOVEL SOLUTION FOR FILLINGNARROW GAPS(<90NM)WITHHDP-CVD-S(集成工艺调制一种利用高密度等离子体化学汽相沉积填充窄间隙(<90nm)的新型方法)”的美国临时专利申请No.60/792,743的优先权,在此引入其全部内容作为参考。

技术领域

本发明公开了一种用于在设置于工艺腔室内的衬底上沉积氧化硅薄膜的工艺。

背景技术

现代半导体器件制造中的基本步骤之一为在半导体衬底上形成诸如氧化硅的薄膜。氧化硅作为绝缘层广泛应用于半导体器件的制造中。公知可利用热化学气相沉积(CVD)或等离子体化学气相沉积及其他方法沉积氧化硅薄膜。在传统的热CVD工艺中,将反应性气体提供给进行热诱导化学反应(均匀或不均匀)的衬底表面上以形成所需薄膜。在传统的等离子体工艺中,形成受控的等离子体以分解和/或激活反应物以形成所需薄膜。

从几十年以前首次出现半导体器件以来,半导体器件的几何尺寸已显著减小。在某些应用中,例如,在相邻的导线或蚀刻的沟槽之间,较小特征尺寸的器件已导致出现增加的孔径比的间隙。间隙的孔径比定义为间隙高度或深度与其宽度之比。利用传统的CVD方法难以填充这些空隙。薄膜完全填充这些间隙的能力被称之为薄膜“间隙填充(gapfilling)”能力。氧化硅为通用于填充金属间介电层(IMD)应用、金属前介电层(PMD)应用和浅沟槽隔离(STT)等应用中的间隙的其中一种类型的绝缘膜。所述氧化硅薄膜常被称之为间隙填充薄膜或间隙填充层。

一些集成电路制造商已转向利用高密度等离子体化学汽相沉积(HDP-CVD)系统以沉积氧化硅间隙填充层。HDP-CVD系统形成大约为标准电容性耦合等离子体CVD系统的密度大小的两倍或以上的等离子体。HDP-CVD系统的实施例包括电感耦合等离子体系统和电子回旋共振(ECR)等离子体系统等。HDP-CVD系统通常在比低密度等离子体系统更低的压力范围操作。HDP-CVD系统中采用的低腔室压力提供具有长平均自由程和减小的角分布的激活物质。这些因素结合等离子体密度有助于来自等离子体的大量成分均匀到达紧密分隔的间隙的最深部分,与在低密度等离子体系统中沉积的薄膜相比,其提供具有改善的间隙填充能力的薄膜。

与用其他CVD技术沉积的薄膜相比,利用HDP-CVD技术沉积的薄膜允许具有改善的间隙填充特性的另一因素在于由等离子体的高密度促进的溅射与薄膜沉积同时进行。HDP沉积的溅射元素减慢在某些形貌诸如突起表面的角落上沉积,从而有利于HDP沉积膜的改善的间隙填充能力。一些HDP-CVD系统导入氩气或类似重惰性气体以进一步促进溅射效果。这些HDP-CVD系统通常利用衬底支架基座内的电极,其能产生使等离子体偏向衬底的电场。所述电场可应用于整个HDP沉积工艺期间以产生溅射并为给定薄膜提供更好的间隙填充特性。通常用于沉积氧化硅的一种HDP-CVD工艺由包括硅烷(SiH4)、氧分子(O2)和氩(Ar)的工艺气体形成等离子体。

然而,与溅射相关的局限在于溅射材料的角重新分布(angularredistribution)。例如,在STI间隙填充中,溅射的SiO2可从沟槽上方溅射并在沟槽的侧面上沉积,这将导致过量聚积并限制实现自下至上的间隙填充所经过的开口。如果有太多的再沉积,在底部被填充之前该沟槽可能关闭,并在沟槽内留下内埋孔。

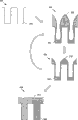

图1A示出了在具有由衬底上形成的两个相邻形貌122、124限定的间隙120的衬底(未示出)上薄膜沉积的起始阶段。如图1A所示,传统的HDP-CVD氧化硅沉积工艺导致在间隙120内的水平表面126上和形貌122、124上的水平表面128上直接氧化硅沉积。由于随着氧化硅薄膜生长,从氧化硅薄膜溅射的物质的再结合,该工艺还导致侧壁130上的间接沉积(称之为再沉积)。在某些小宽度、高孔径比的应用中,氧化硅薄膜的继续生长导致在上部分间隙侧壁上的形成结构132,其以超过薄膜在侧壁的下部分134上横向生长的速率彼此相对生长(也可参见图1B)。该工艺的最终结果为形成如图1C中所示的孔136。

随着沟槽越来越密集,即使采用更轻的原子,在完成自底向上填充之前关闭沟槽的可能性也会越来越大。He工艺已能提供小至110nm的间隙填充方法,而H2工艺已推广HDP-CVD降低至小于65nm。旋涂介电薄膜和ALD(原子层沉积)薄膜已具有达到比HDP-CVD已能填充的更紧密结构的间隙填充能力。但是,由于诸如薄膜收缩和可靠性等其他原因,用户不是很愿意进行所述转换。

在美国专利No.6,908,862中描述了保持沟槽顶部张开并允许完成自底向上填充的另一方法为在沟槽将要关闭的工艺点利用NF3基团的等离子体干法蚀刻,在此引入其全部内容作为参考。NF3在等离子体中分解,形成反应性的氟自由基。这些自由基能破坏沉积薄膜中的Si-O键,形成一种挥发性物质SiF4,根据:

4F·+SiO2(s)→SiF4(g)↑+O2(g).

SiF4与过量的O2一起排出,从而去除沉积的薄膜并打开沟槽。这种沉积-蚀刻-沉积(“DED”)工艺给原来间隙填充的工艺提供小但是意义重大的容限。

一般地,在传统的DED工艺中,在沉积步骤之前,每个沉积步骤采用对于衬底特征优化的不同工艺条件。例如,起始沉积步骤“dep1”可沉积相对薄的层,意在保护沟槽的侧壁不受以后的蚀刻步骤“etch1”影响。第二沉积步骤“dep2”一般包括相对厚的层的沉积。

如果DED包括进一步沉积和蚀刻步骤,则通常通过具体用于该步骤的优化条件设计各个沉积步骤(dep1、dep2、第三沉积步骤“dep3”等)以及各个蚀刻步骤(etch1、第二蚀刻“etch2”等)。例如,通常基于ech1完成时层的形貌优化dep2,基于完成ech2时层的形貌优化dep3,等。

具有对每个沉积和每个蚀刻步骤独立调制的工艺的传统DED工艺的缺点在于在制造中每个步骤通常需要独立限定条件。也就是说,在生产制造线中安装DED工艺之前,通常根据dep1运行许多衬底以满足dep1的条件,并通常根据ech1运行许多衬底以满足ech1的条件,等等。

发明内容

本发明的实施方式关于一种用于沉积具有改善的间隙填充能力的氧化硅薄膜的方法和设备。本发明方法的实施方式利用HDP-CVD沉积技术沉积所述薄膜并尤其有益于在具有0.10微米或更小的特征尺寸的集成电路制造中的金属前介电层和浅沟槽隔离的应用。如本文所采用,高密度等离子体为具有至少1×1011离子/厘米3的离子密度。

本文公开的工艺包括低温(低于400℃)沉积后蚀刻依次交替执行的步骤。每个低温沉积跟随一个蚀刻工艺,从而对于STI应用,例如,沟槽的开口保持张开并且可在基本没有孔洞的情况下完成自底向上的间隙填充。与利用温度高于400℃的沉积以改善底部填充的传统DED工艺相比,本文所述的工艺进一步包括温度低于400℃,以及甚至与室温一样低的温度的沉积。该工艺包括,在软件控制下,重复预设次数循环的基本上相同的沉积和蚀刻工艺。

因此,一方面,一种用于填充在衬底上形成的金属沉积前的沟槽的方法包括执行一循环,该循环包括在高密度CVD腔室中在衬底上沉积层,将衬底冷却至低于400℃,并在腔室中蚀刻位于衬底上一部分沉积层的过程。该方法还包括以预设次数循环重复沉积该层和蚀刻一部分该层的循环。在某些实施方式中,循环的预设次数为至少四次。

在不同的可选实施方式中,该方法可包括流入背侧制冷气体以冷却热耦合到衬底上的平台。沉积所述层可包括产生包含沉积气体和溅射气体的等离子体,其中沉积与溅射之比为10:1到60:1的范围。在某些实施方式中,蚀刻可包括允许衬底加热至高于沉积温度的温度,以及可包括各向异性蚀刻和各向同性蚀刻的多步骤蚀刻。在某些实施方式中,可通过终点技术终止在起始循环中蚀刻部分沉积层,并在后续循环中可计时终止蚀刻部分沉积层的过程。

该方法可可选地包括利用将衬底冷却至低于400℃沉积该层,以及在重复沉积-蚀刻循环预定次数的循环之后,加热衬底以减少所述层中的水分。在某些实施方式中,该方法可包括,在开始沉积-蚀刻循环之前,利用富硅沉积时效处理(seasoning)腔室以避免用于蚀刻所述部分层的蚀刻气体损坏腔室(例如,在腔室中时效处理的沉积物为单层沉积厚度的4到20倍)。

附图说明

图1A-图1C为在高孔径比的间隙填充应用中在不同沉积阶段的HDP-CVD氧化硅薄膜的截面简化图;

图2A为可结合本发明的实施方式采用的示例性衬底处理系统的截面简化图;

图2B为可与图2A的示例性CVD处理腔室结合使用的气环的截面简化图;

图3为描述利用本发明实施方式的工艺可如何填充高孔径比特征的截面示意图;以及

图4为根据本发明一实施方式的重复的低温沉积和蚀刻氧化硅薄膜循环相关的多个步骤的流程图。

具体实施方式

本发明实施方式涉及一种高密度等离子体化学气相沉积(“HDP-CVD”)方法,其可适用于例如,在浅沟槽隔离(“STI”)应用中沉积层。本发明的实施方式允许对具有小特征尺寸(90nm或更小)的集成电路以基本100%的间隙填充沉积材料。可在具有高孔径比极深沟槽内实现自底向上的间隙填充。

可采用多种高密度等离子体CVD衬底处理腔室实施本发明的实施方式,该高密度等离子体CVD衬底处理腔室包括通过将射频能施加给至少部分地围绕一部分腔室的线圈形成等离子体的腔室和利用ECR(电子回旋共振)等离子体形成技术的腔室。以下将描述可实践本发明方法的实施方式的电感耦合HDP-CVD腔室的实施例。

示例性衬底处理系统

图2A示出了可沉积根据本发明所述介电层的高密度等离子体化学气相沉积(HDP-CVD)系统10的一实施方式。系统10包括腔室13、衬底支架18、输气系统33、远程等离子体清洗系统50、真空系统70、源等离子体系统80A、偏压等离子体系统80B。

腔室13的上部分包括顶14,其由诸如氧化铝或氮化铝的陶瓷介电材料组成。顶14限定等离子体处理区16的上边缘。等离子体处理区16由衬底17的上表面和也由氧化铝或铝陶瓷材料组成的衬底支架18限定在底部。

加热台23和冷却台24在顶14之上与其热连接。加热台23和冷却台24允许顶温度控制在约100℃到200℃的范围偏离±10℃内。一般地,暴露于等离子体中加热设置于衬底支架18上的衬底。衬底支架18包括内管和外管(未示出),其能输送加热的传送气体(有时称之为背侧冷却气体)至衬底的背侧。如以下将进一步描述,背侧冷却气体能将衬底冷却至明显低于400℃的温度。

腔室13的下部分包括主体构件22,其将腔室联接至真空系统。衬底支架18的基座部分21设置于主体构件22上,并与主体构件22形成连续的内表面。利用机械手(未示出)通过腔室13的侧面中的入口/移出口(未示出)传送衬底进出腔室13。在电机的控制下(也未示出)提升并接着降低升降杆(未示出)将衬底从在上部加载位置57的机械手移动至下部处理位置56,这里衬底放置在衬底支架18的衬底接收部分19。衬底接收部分19包括静电卡盘20,其可用于在衬底处理期间将衬底固定于衬底支架18上。

真空系统70包括节气门25,其包含双叶片节流阀26并连接至闸阀27和分子涡轮泵28。闸阀27可使泵28与节气门25分隔,并还可当节流阀26全部打开时通过限制排出流量来控制腔室压力。节流阀、闸阀和分子涡轮泵的设置方式允许将腔室气压精确并稳定的控制在约1m Torr那么低。

源等离子体系统80A耦合至设置于顶14上的顶线圈29和侧线圈30。对称的接地护罩(未示出)减少线圈之间的电耦合。顶线圈29由顶源RF(SRF)发生器31A提供能量,而侧线圈30由侧SRF发生器31B提供能量,从而允许每个线圈具有独立的功率级别和工作频率。在具体实施方式中顶源RF发生器31A在2MHZ的额定频率下最高提供10,000瓦的RF功率以及侧源RF发生器31B在2MHZ的额定频率下下提供最高10,000瓦的RF功率。顶和侧RF发生器的工作频率可以和额定工作频率(例如分别到1.7-1.9MHz和1.9-2.1MHz)存在一定偏差以提高等离子体产生效率。

偏压等离子体系统80B包括偏压RF(BRF)发生器31C和偏压匹配网络32C。偏压等离子体系统80B将衬底部分17电容耦合至用作互补电极的主体构件22。该偏压等离子体系统80B用于改善由源等离子体系统80A产生的等离子体物质至衬底表面的输送。在具体实施方式中,偏压RF发生器在13.56MHz的频率下提供最高10,000瓦的RF功率。

RF发生器31A和31B包括数字控制的合成器并在大于约1.8到约2.1MHz之间的频率范围工作。每个发生器包括如本领域普通技术人员熟知的测量从腔室和线圈反射回到发生器的功率的RF控制电路(未示出)并且调节工作频率以获得最低的反射功率。匹配网络32A和32B将发生器31A和31B的输出阻抗与它们各自的线圈29和30匹配。RF控制电路可通过改变匹配网络内的电容值调制所有匹配网络以使发生器随着负载改变而与负载匹配。当从负载反射到发生器的功率超过一定限度时,功率RF控制电路可以调节匹配网络。一种提供恒定匹配并有效地使RF控制电路调节匹配网络失效的方法在于设置反射功率的限度大于反射功率的任意期望值。可通过在最新条件下保持匹配网络恒定帮助在某些条件下稳定等离子体。

输气系统33经由输气管38(仅示出了其中几个)提供来自几个气源34(a)...34(n)的气体。在以下描述的具体实施例中气源34(a)...34(n)包括SiH4、O2、Ar和NF3的独立气源,以及用于补充的清洗工艺的一个或多个气源。如将由本领域普通技术人员所熟知,根据腔室13内执行的沉积和清洗工艺,改变气源34(a)...34(n)的实际气源和输气管38至腔室13的实际连接。通过如本领域普通技术人员熟知的一个或多个流量控制器(未示出)控制来自各气源34(a)...34(n)的气流。

气体通过气环37和/或顶喷嘴45导入腔室13中。图2B为腔室13的部分截面简化图,其示出了气环37的附加具体结构。在某些实施方式中,一个或多个气源经由输气管38(仅示出其中几个)将气体提供给气环37中的气环气室36中。气环37具有多个在整个衬底上提供均匀气流的喷气嘴39(为描述目的仅示出其中之一)。可改变喷嘴长度和喷嘴角度以对于独立腔室内的具体工艺可以调整均匀形状和气体利用效率。在一具体实施方式中,气环37具有24个由氧化铝陶瓷组成的喷气嘴39。

气环37还具有多个喷气嘴40(仅示出其中之一),在具体实施方式中,喷气嘴40与气源喷嘴39共平面并比该气源喷嘴短,以及在一实施方式中接收来自主体气室41的气体。在将气体注入腔室13之前,不期望混合通过气环37导入的气体(例如,SiH4和O2)的某些实施方式中,喷气嘴39和40不为流体耦接的。在其他实施方式中,将气体注入腔室13之前通过在主体气室41和气环气室36之间设置的间隙(未示出)可将气体混合。诸如43B(未示出其他阀)的附加阀可切断从流量控制器至腔室的气体。

在使用可燃性、毒性或腐蚀性的气体的实施方式中,在沉积或清洗工艺后可能希望去除残留在输气管中的气体。这可利用诸如阀43B的3通阀使腔室13与输气管38隔离同时吹扫输气管38到真空前管44之间的管路实现。如图2A所示,在其他气体输气管上可结合诸如43A和43C的其他类似阀。这种3通阀在应用中可靠近腔室13和远程等离子体源50设置,以最小化未受到吹扫的输气管(3通阀和腔室之间)的量。另外,可在流量控制器(“MFC”)和腔室之间或气源和MFC之前设置两通(开-关)阀(未示出)。

再参照图2A,腔室13还具有顶喷嘴45和顶出口46。顶喷嘴45和顶出口46允许独立的控制顶气流和侧气流,其将改善薄膜均匀性并允许薄膜沉积和掺杂参数的精确调节。顶出口46为围绕顶喷嘴45的环形开口。在一实施方式中,一气源,例如SiH4,通过独立的MFC(未示出)提供给气源喷嘴39和顶喷嘴45。类似地,独立的MFC可用于控制来自单个氧气源的氧气流入至顶出口46和喷气嘴40。在气体流入腔室13前可以保持顶喷嘴45和顶出口46分离,或者该气体可以在流入腔室13前在顶气室48混和。在其他实施方式中,相同气体的独立气源可用于提供给腔室的不同部分。

提供产生远程微波的等离子体清洗系统50以在干洗操作中周期性地清洗来自腔室部件的沉积残留物。该清洗系统包括远程微波发生器51,其在反应腔53中产生由来自气源34(a)...34(n)(例如,氟分子、三氟化氮、其他碳氟化合物、单独或与诸如氩的另一气体结合的等同物)的一个或多个清洗气源形成的等离子体。该等离子体生成的反应物经由给料管55通过清洗气体送气口54输送给腔室13。用于容纳清洗等离子体的材料(例如腔53和给料管55)必须抗等离子体的破坏。在实际中反应腔室53和送气孔54之间的距离应当保持尽可能短,原因在于优选的等离子体物质的浓度可随着离反应腔53的距离而下降。在远程腔室内产生清洗等离子体允许使用高效率的微波发生器,并且使腔室部件不必经受可能出现在原位形成的等离子体中的辉光放电的温度、辐射或轰击。因此,诸如静电卡盘20的相对敏感的部件,不需要用如采用原位等离子体清洗工艺可能所需的虚拟的晶圆覆盖或保护。

系统控制器60控制系统10的操作。例如控制器60可包括存储器62,诸如硬盘驱动器和/或软盘驱动器和耦接至处理器61的插件架(card rack)。插件架可包含单板计算机(SBC)、模拟和数字输入/输出板、接口板和步进电机控制板。系统控制器60在存储在硬盘驱动器上的计算机程序或通过诸如存储在可移动式磁盘上的程序的其他计算机程序的控制下操作。计算机程序指示例如具体工艺的时间、气体混合、RF功率级别和其他参数。

根据本发明的具体实施方式沉积氧化硅薄膜

如本文进一步描述,可沉积氧化硅薄膜用于极深的间隙填充应用中。例如在某些实施方式中,在沟槽顶部小于65nm的间隙中可沉积用于STI应用(在衬底上形成金属信号线之前)的氧化硅薄膜。

如以上所述,可在诸如上述示例性腔室13的HDP-CVD腔室中实践本发明的实施方式。为简单起见,参照图3示出了根据本发明的沉积和蚀刻的概略图。

衬底上的沟槽300的截面301示出了起始条件。虽然针对一个或多个“间隙”或“沟槽”上沉积进行描述,但本发明不限于浅沟槽隔离,而可应用于衬底上几乎任何结构上的沉积。相邻的特征限定要填充介电材料的沟槽300,所述特征的表面限定沟槽300的侧壁。例如,衬底中的沟槽300可包括例如硅、或具有氮化物阻挡层的硅。

如截面302所示,随着沉积的进行,介电材料聚集在沟槽300的最上表面的尖点308处(通俗地称之为在沟槽300上形成的“帽子”)以及沟槽300的底部。由于从尖点308溅射材料的再沉积,介电材料还可在沟槽300的角落处形成悬垂。

如以下进一步描述,与一般优选较高温度以改善自底向上的间隙填充的传统DED工艺不同,根据本发明的沉积在低温下进行,其能带来多个优点。例如,较低的沉积温度可提供改善的侧壁覆盖,其防止后续的蚀刻损坏下层结构。另外,利用在低温下沉积可改善薄膜应力。传统的高温沉积通常在薄膜中产生压力并超过IC工艺的应力极限(通常250MPa)。另一方面,低温沉积可得到具有相对低应力(例如150-200MPa)的良好间隙填充。

截面303示出了用于降低沉积材料的孔径比的蚀刻。在蚀刻步骤期间减小的尖点310为保护性的,其将生成截面303。各向异性地进行蚀刻,诸如在反应性蚀刻期间通过施加偏压,有助于定型沉积层从而保留原始沟槽300的基本形状,而同时具有较低的孔径比,并且下层沟槽300的角落仍未暴露。

如向上的弧形箭头所示,以预设次数循环以上所述的沉积和蚀刻步骤填充沟槽300。基于以上所述的各个沉积和蚀刻步骤对沟槽300的总深度的分析可确定循环次数。例如,在每个循环中沉积750和蚀刻250的情况下,在每个循环中提供500的沉积量,则大约7个重复的循环将填充大约4000衬底的沟槽。当完成预设次数的循环时,沟槽300可在没有明显孔洞的情况下,部分地或全部地用介电材料312填充,诸如用截面304示意性示出。

图4为根据本发明的一实施方式描述的氧化硅薄膜的低温沉积和蚀刻重复循环的方法400的流程图。尽可能在以下描述中的附图标记用于指代图2A-图2B的示例性腔室13的对应部件。在该实施方式中利用存储在系统控制器60的存储器62的计算机程序实施并控制所述工艺。

利用图4所示的流程图概述用于一实施方式的方法400。该方法仅用于示例性目的并不意在限定本发明的权利要求书范围。在步骤405,执行一个或多个准备性步骤以准备后续沉积和蚀刻工艺循环。例如,步骤405包括将在其上待沉积氧化硅层的衬底传送至沉积腔室13中,以及可包括诸如稳定腔室压力等工艺。

一旦衬底和腔室13稳定,则开始初始沉积407。在步骤410,通过将衬底冷却至低于400℃的沉积温度稳定衬底温度。较低温度沉积通常改善侧壁覆盖(与较高温度沉积相比)并防止后续蚀刻步骤435损坏下层结构。在某些实施方式中,在衬底冷却至低于400℃,并甚至明显低于290℃或甚至接近室温的温度下沉积薄膜。如以下所述,一种用于冷却衬底的方法为通过经由衬底支架18流入He背部冷却气体和/或冷却水。另外,如以下进一步描述,一般认为低于室温或室温以下沉积可能有益于应变工程应用中。

在步骤415,包括作为硅源的SiH4与H2、He和O2沉积工艺气体一起流入工艺腔室13中。根据如本文进一步描述的具体应用、衬底上具体结构、执行沉积的腔室的设计,以及其他考虑,可改变对于不同前驱气体的适用速率。在硅源包括SiH4以及氧化气体反应物包括O2的实施方式中,合适的流速Φ在如下范围内:对于SiH4,用于参照图2所述的腔室设计的流速Φ(SiH4)可在约15和100sccm之间;对于O2,流速Φ(O2)可在约25和500sccm之间;对于He,流速Φ(He)可在约200和400sccm之间;以及对于H2,流速Φ(H2)可在约100和200sccm之间。虽然该流速范围提出了较宽的流速参数,但具体的流速可以根据具体的腔室结构决定,以下进一步描述对此进行描述。

在某些实施方式中,不是采用H2和He,而仅采用H2与SiH4和O2。在某些实施方式中,所述沉积可包括Ar、Xe或其他惰性气体,但通常所述惰性气体提供相对高的溅射成分,其可能需要用低偏压功率补偿,产生相对差的薄膜质量。

在沉积气体中提供H2和He两种气体提供用于控制沉积/溅射(D/S)比的调节“按钮”。D/S比取决于偏压功率,并优选地为10:1到60:1的范围内,例如,可通过测量由所有沉积气体产生的沉积速与由较少的SiH4的沉积气体产生的溅射速率相比确定所述D/S速率为30:1。一般地,高D/S速率不利于薄膜质量,并且非偏压工艺趋向于产生富硅多孔薄膜。可调节沉积步骤407的D/S速率以在沟槽300的侧壁(图3)上获得充分覆盖,例如,其保护氮化物衬垫同时利用连续的沉积和蚀刻循环降低沟槽300的孔径比。

在步骤420,利用工艺气体在腔室13中形成高密度等离子体。在某些实施方式中,高RF功率(例如,等于30kW的顶、侧和偏压RF功率总和)可用于改善自底向上的覆盖。然而,高的总RF功率趋向于提高衬底的温度并趋向薄膜中产生压力。因此,在优选的实施方式中,对于300mm衬底施加约17.5kW的总RF功率。

在步骤425,在衬底上进行薄膜沉积。沟槽300的侧壁上的覆盖量相对底部覆盖量为沉积条件的一个考虑因素。一般地,由于来自尖点308的材料可能导致悬垂的凹角生长,因此选择最小化尖点308(图3)沉积量的沉积条件。还可选择沉积条件以在侧壁上提供充分的薄膜,例如,以保护沟槽300中的氮化物衬垫。

在一实验中,采用蚀刻至约90nm间隔并具有深度600nm的沟槽的STI测试图案晶圆。通过增加ISSG(原位蒸气生成)氧化衬垫和LPCVD(低压化学气相沉积)氮化物衬垫进一步让间隔变窄。在所述测试图案晶圆上,在步骤407中沉积的介电材料为约为在沟槽侧壁上沉积的介电材料量的30%。该沉积厚度在最小化尖点308上的沉积和利用侧壁上的沉积保护氮化物衬垫之间提供可接受的平衡。在该实验中,腔室中的衬底温度监控设备不能测量低于290℃的温度。在这种情况下,可以知道衬底冷却到了290℃以下,但不能确定衬底的实际温度。

沉积步骤407之后,可选地包括过渡步骤430以平稳地过渡到接下来的蚀刻步骤435。在一实施方式中,过渡步骤430逐渐降低O2流速并调节H2&He流速以与接下来的蚀刻步骤435采用的流速匹配。例如,过渡步骤430可在腔室没有SiH4的情况下,向腔室中导入NF3以避免在衬底上形成SiF4。

在步骤435,利用高密度等离子体蚀刻开始蚀刻。在蚀刻步骤435期间,移除大约5%到30%薄膜沉积厚度,虽然移除的量可根据薄膜的形状在不同点处而改变。在某些实施方式中,诸如NF3的含氟氮气体或诸如C2F6、C3F8或CF4的含氟碳气体流入工艺腔室中。CF类化学物质通常产生氮化硅对氧化硅的更大选择性蚀刻。

一般地,在蚀刻步骤435期间可加入H2和/He以减小蚀刻的溅射成分并提供用于整个工艺的另一调节按钮。与传统的Ar/NF3蚀刻或Ae/O2/NF3蚀刻相比,由于氟为具有较大溅射成分的相对大的原子,发明者已发现有控制的增加H2和/或He有利于减少蚀刻步骤435中溅射成分。减少氟浓度(利用相对高浓度的H2和N2)给蚀刻步骤435提供更多的溅射成分,而增加氟浓度给蚀刻步骤435提供更多的各向异性成分。在某些实施方式中,蚀刻步骤435采用相对多的H2,原因在于H2清除一些氟并提供更多的选择性蚀刻。

还可采用控制晶圆偏压功率、静电卡盘电压和RF功率的方式控制蚀刻步骤435是否为各向同性或各向异性。根据沟槽的深度和角度,可调节蚀刻工艺的特征以提供较多或较少溅射(定向的)蚀刻相对各向异性蚀刻(较少定向的)。基于沟槽深度、宽度和角度,可通过实验确定沉积和蚀刻成分的具体比值。

蚀刻步骤435可包括在后续沉积步骤(例如,dep2)中冷却以避免衬底受热的步骤。例如,利用氦背部冷却衬底等其他方法可执行所述冷却。在某些实施例中,通过冷却步骤降低衬底温度低于约250℃还可进行所述蚀刻,并因此提供更好的蚀刻控制。

在其他实施方式中,在蚀刻步骤435期间可以不采用衬底冷却从而在蚀刻步骤435期间允许衬底加热。由于在较低温度氟更容易进入薄膜中,因此在蚀刻步骤435期间允许衬底加热有助于从薄膜移除氟。也就是说,衬底的温度曲线可为在沉积步骤407期间主动冷却衬底,在蚀刻步骤435期间可主动或被动地加热衬底以移除氟,并接着在后续沉积步骤(例如,dep2)中可再次冷却衬底。

蚀刻步骤435可包括多步骤蚀刻工艺。一般地,在蚀刻步骤435期间同时进行两个工艺:各向同性(例如,基于氟)蚀刻成分和溅射蚀刻方案(例如,利用He)。取代同时进行工艺,蚀刻步骤435可分为两个独立的蚀刻步骤,起始采用相对高的氟浓度以减小尖点308(图3)的尺寸,接着用相对较多的各向同性蚀刻成分以提供蚀刻均匀性。

蚀刻步骤435的周期(蚀刻时间)通常取决于蚀刻速率、气体流速、顶/侧/底部功率等。蚀刻步骤435的周期还可取决于蚀刻是否提供各向异性蚀刻对各向同性蚀刻和/或衬底中心到边缘的蚀刻速率。

在某些实施方式中,利用终点技术执行起始循环的蚀刻步骤435的终止,以及根据时间执行后续循环的蚀刻步骤435的终止。例如,利用检测蚀刻步骤435何时蚀刻穿过沟槽300中的下部氮化物层的光线发射光谱仪(OES)可终止起始循环中的蚀刻步骤435。OES终点用于确定基准蚀刻时间。因此,在后续循环的沉积和蚀刻中,基于基准蚀刻时间函数终止蚀刻步骤435。

也就是说,在起始循环的蚀刻步骤435(etch1)中,OES数据可用于确定需要到达下部氮化层所需的基准蚀刻时间。每个后续循环的蚀刻步骤435(etch2、etch3等)的周期可为与基准蚀刻时间相同的时间,或者比基准蚀刻时间或多或少一定的预设量。例如,如果etch1需要10秒钟蚀刻至如由终点确定的氮化物层,则etch2、etch3等可能要9秒钟作为固定的蚀刻时间量。

在替代的实施方式中,后续蚀刻循环的周期可关于基准蚀刻时间成几何变化。例如,etch2可采用具有少于基准蚀刻时间20%的周期的定时蚀刻,etch3可采用少于第二蚀刻循环20%的周期的定时蚀刻,等等。提供关于基准蚀刻时间的几何变化可提供随着后续循环在沟槽300中递增地减小的孔径比。

在其他实施方式中,在每个晶圆后没有清洗腔室13的情况下,后续晶圆的蚀刻时间可根据清洗后处理的衬底数量而不同。例如,在清洗后第一衬底可能蚀刻10秒钟,在清洗后第二衬底可能蚀刻11秒钟,等等。因此,蚀刻步骤435中所用的蚀刻时间量可能取决于腔室13内沉积的富集情况。

蚀刻步骤435之后,过蚀刻处理步骤440为后续沉积步骤准备衬底。过蚀刻处理步骤440包括等离子体处理以减少或消除在蚀刻步骤435期间进入薄膜的氟。等离子体处理可包括利用O2、Ar、H2和He中的一种或多种气体的等离子体处理以降低薄膜中的氟。提供H2等离子体处理可包括溅射衬底以改变衬底上的形貌。

在步骤445,确定是否已完成预设次数的沉积和蚀刻循环。基于以上所述单独沉积和蚀刻步骤对沟槽的总深度的分析可确定循环次数。例如,在完成步骤410-445的每个循环中沉积750和蚀刻250,在每个循环中留下沉积500的情况下,将需要大约7个重复循环以填充深度约4000的沟槽。

在完成预设次数的沉积和蚀刻循环之后,完成步骤450可可选地包括为进一步处理准备衬底的步骤。例如,完成步骤450可包括传统的覆盖沉积工艺以得到所需的总薄膜厚度,或者用于诸如化学机械抛光(CMP)的平坦化工艺。

图4所示的方框的具体顺序希望是限定性的,以及在其他实施方式中,可以替代的顺序执行相应的步骤。例如,可在步骤415将气体流入工艺腔室13的同时或之后执行如在步骤410所述的将衬底温度冷却至低于400℃。另外,图4的具体方框中的内容不意在为限定性的,原因在于在替代的实施方式中可执行附加的步骤。

如上所述,虽然步骤410将衬底冷却至低于290℃的温度,但一般认为通过将衬底冷却至室温或以下可能具有优势。传统地,将衬底冷却至所述低温将趋向于产生拉伸薄膜和较差的薄膜质量。然而,本发明研究表面在经过预设次数的沉积和蚀刻步骤的循环之后,在完成步骤450时提供高功率等离子体可足以消除会导致拉伸薄膜的沉积膜中的水分。替代地,在完成预设次数循环之前,可执行高功率等离子体。例如,在7个沉积和蚀刻循环的情况下,在循环1、3、5和7之后可执行高功率等离子体。一般认为结合沉积后薄膜的后续修复的极低温度处理对于未来IC工艺应用可能是至关重要的。

诸如时效处理清洁状况的腔室13条件会影响到方法400的效果。在某些实施方式中,腔室13采用两步清洗进行清洗,其中设置程序低压清洗和相对较高压清洗以分别清洗腔室13的腔室盖和腔室壁或的其它部分。清洗后可接着SiH4沉积和清洗步骤以适当时效处理腔室13。清洗可结合加热腔室13以改善清洗效果。

在某些实施方式中,优选地在开始方法400之前,或者处理许多晶圆之后时效处理腔室13。在某些实施方式中,时效处理包括利用富硅沉积涂覆腔室以避免用于蚀刻部分层的蚀刻气体损坏腔室,以及腔室中的时效处理沉积厚度为单沉积-蚀刻循环的沉积厚度的4-20倍。由于蚀刻循环改变腔室13中的条件,因此腔室的时效处理可避免在方法400随着时间从晶圆到晶圆发生漂移。例如,蚀刻步骤435可导致腔室壁比腔室顶清洗得更多或更少。另外,方法400在沉积期间采用高RF源功率、O2和H2的高氧化等离子体,以及在蚀刻步骤435期间采用高还原氟。几乎没有商业实用材料能忍受这种极端条件。时效处理允许方法400在腔室13中于商业实用成分一起使用。

工艺优化

在方法400中,设计沉积步骤407和蚀刻步骤435以避免在蚀刻步骤435期间损坏下层结构。这可通过组合效果实现。设计沉积步骤407以确保沉积充足的材料保护下层结构。设计在蚀刻步骤435期间建立的条件从而不蚀刻掉太多材料以致暴露沟槽300(图3)的下层结构。

也就是说,利用方法400对衬底上给定结构在间隙填充方面优化性能的因素通常为沉积厚度和蚀刻去除量。在给定沉积量的情况,则优化蚀刻去除量。如果蚀刻不去除足够的沉积材料,则沟槽不张开并且后续沉积将不利地增加尖点效应并留下孔洞。如果蚀刻去除过多的沉积材料,则可能破坏衬底上的任意结构(如氮化物衬垫)并且可能损坏器件。对于每个蚀刻条件和每个沉积条件以及厚度,应当确定最适宜的蚀刻量。

例如在一实验中,在每个循环的蚀刻步骤435中去除提供完全填充沟槽300。然而,在每个蚀刻步骤435中仅去除的情况下,在衬底边缘的沟槽300内形成孔洞。因此,在蚀刻步骤435期间蚀刻的量将影响获得指定量沉积厚度所需循环的数量(更多的蚀刻方式减慢沉积物的生长以及增加循环数量),并且还影响在沟槽300中是否可能形成孔洞。一般地,相对少量的沉积(</循环)以及相应少量的蚀刻(优选地薄膜沉积厚度的约5-15%)得到更多的“自底向上”沉积并避免在狭窄或“紧密”的沟槽结构中形成孔洞。

为确定最优的工艺,工艺研发的方法可采取以下通用程序,参照图3和图4。首先,在测试图案的衬底上,采用步骤410-425,执行单循环沉积。对于沉积膜,测量底覆盖、侧壁覆盖和尖点308的高度。接着,执行单循环蚀刻步骤435,并测量以确定底部、侧壁和尖点308上的去除量。采用沉积测量和蚀刻测量,独立地优化用于衬底上最小结构或具有最高孔径比的结构的沉积步骤410-425和蚀刻步骤435。

方法400的优点在于易于使用。与在整个工艺中一般要求限定每个步骤的传统的DED工艺相比,本文所述方法400的某些实施方式具有在操作中易于使用以及容易限定。在方法400中,一旦对于衬底上的具体结构优化沉积和蚀刻步骤,操作者可能调节的参数仅为沉积时间和蚀刻时间。可编程HDP-CVD反应室的控制器以允许重复的、快速的和精确的沉积和蚀刻循环,便于工艺管理的。

方法400的另一优点在于相对低的沉积温度比传统DED工艺中采用的较高晶圆温度提供对下层沟槽特征(例如氮化物衬垫)的更大程度的保护。采用冷却沉积,改善侧壁覆盖,提供对有源区域更好的保护并允许在无损坏的情况下进行间隙填充。相反的,显然采用高温沉积侧壁将较少地得到保护并且边缘的剪切边(clipping)可能很明显。

本领域的普通技术人员将认识到对于不同的工艺腔室和不同的工艺条件工艺参数可发生改变,以及可在不偏离本发明精神范围内采用不同的前驱物。对于本领域的普通技术人员其他改变也是明显的。本发明的范围意欲包含这些等同物和替代物。因此,本发明的范围不应当限于以上所述的实施方式,而应当由以下的权利要求书所限定。

Claims (21)

1.一种用于填充在衬底上形成的金属沉积前的沟槽的方法,包括,

执行循环,该循环包括:

在高密度化学气相沉积腔室中在冷却至低于400℃的衬底上沉积层,以及

在所述腔室内蚀刻所述衬底上的部分所沉积的层;以及

以预设循环次数重复沉积所述层和蚀刻部分所述层的所述循环。

2.根据权利要求1所述的方法,其特征在于,重复沉积所述层和蚀刻部分所述层的所述循环包括建立与用于一个或多个起始循环中相同的工艺条件。

3.根据权利要求1所述的方法,其特征在于,还包括流入背部冷却气体以冷却与所述衬底热耦合的平台。

4.根据权利要求1所述的方法,其特征在于,沉积所述层包括产生包括沉积气体和溅射气体的等离子体,其中沉积与溅射之比为在10:1到60:1的范围内。

5.根据权利要求1所述的方法,其特征在于,每个连续的沉积和蚀刻循环包括降低由所述层填充的沟槽的孔径比。

6.根据权利要求1所述的方法,其特征在于,

沉积所述层包括在靠近所述沟槽的开口、所述沟槽的侧壁上、以及所述沟槽的底部上沉积材料;以及

蚀刻包括从靠近所述沟槽的开口处去除的沉积材料比从所述沟槽的底部去除的材料相对更多。

7.根据权利要求1所述的方法,其特征在于,所述蚀刻包括形成氢和氦中的一种或多种以及含氟气体构成的等离子体。

8.根据权利要求1所述的方法,其特征在于,蚀刻部分所沉积的层包括去除所述层的5-30%的沉积厚度。

9.根据权利要求1所述的方法,其特征在于,蚀刻包括允许所述衬底加热至温度高于沉积温度。

10.根据权利要求1所述的方法,其特征在于,蚀刻包括各向异性蚀刻和各向同性蚀刻的多步骤蚀刻。

11.根据权利要求1所述的方法,其特征在于,在第一蚀刻循环中蚀刻的部分所沉积的层大于后续蚀刻循环中蚀刻的部分所沉积的层。

12.根据权利要求1所述的方法,其特征在于,利用终点技术终止在第一沉积-蚀刻循环中蚀刻部分所沉积的层的过程,以及计时终止在后续沉积-蚀刻循环中蚀刻部分所沉积的层的过程。

13.根据权利要求1所述的方法,其特征在于,还包括,在重复所述沉积-蚀刻循环之前,形成氩、氢和氦的一种或多种以及氧构成的等离子体。

14.根据权利要求1所述的方法,其特征在于,还包括:在重复所述沉积-蚀刻循环之前,形成氢的溅射等离子体。

15.根据权利要求1所述的方法,其特征在于,沉积所述层包括将所述衬底冷却至低于300℃,进一步包括,在重复预设循环次数的所述沉积-蚀刻循环之后,加热所述衬底以减少所述层中的水分。

16.根据权利要求1所述的方法,其特征在于,进一步包括:在重复预设循环次数的所述沉积-蚀刻循环之后,沉积覆盖层。

17.根据权利要求15所述的方法,其特征在于,加热所述衬底包括在所述腔室中产生沉积气体或一种或多种惰性气体构成的高功率等离子体。

18.根据权利要求1所述的方法,其特征在于,进一步包括,在开始所述沉积-蚀刻循环之前,利用富硅沉积物时效处理所述腔室以避免用于蚀刻部分所述层的蚀刻气体损坏所述腔室。

19.根据权利要求18所述的方法,其特征在于,时效处理所述腔室包括在所述腔室内沉积所述层的沉积厚度的4-20倍厚度的沉积物。

21.根据权利要求1所述的方法,其特征在于,蚀刻部分所述层包括形成一种或多种含氟碳物质蚀刻气体构成的等离子体。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US79274306P | 2006-04-17 | 2006-04-17 | |

| US60/792,743 | 2006-04-17 | ||

| US11/553,772 | 2006-10-27 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101079379A CN101079379A (zh) | 2007-11-28 |

| CN100539039C true CN100539039C (zh) | 2009-09-09 |

Family

ID=38906757

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2007100902636A Expired - Fee Related CN100539039C (zh) | 2006-04-17 | 2007-04-17 | 集成工艺调制一种利用hdp-cvd间隙填充的新型方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7524750B2 (zh) |

| JP (1) | JP5405004B2 (zh) |

| KR (1) | KR100880967B1 (zh) |

| CN (1) | CN100539039C (zh) |

| SG (1) | SG136873A1 (zh) |

| TW (1) | TW200802605A (zh) |

Families Citing this family (90)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7825038B2 (en) * | 2006-05-30 | 2010-11-02 | Applied Materials, Inc. | Chemical vapor deposition of high quality flow-like silicon dioxide using a silicon containing precursor and atomic oxygen |

| US8232176B2 (en) * | 2006-06-22 | 2012-07-31 | Applied Materials, Inc. | Dielectric deposition and etch back processes for bottom up gapfill |

| WO2008020267A2 (en) * | 2006-08-16 | 2008-02-21 | Freescale Semiconductor, Inc. | Etch method in the manufacture of an integrated circuit |

| KR100818714B1 (ko) * | 2007-04-10 | 2008-04-02 | 주식회사 하이닉스반도체 | 반도체 소자의 소자분리막 형성방법 |

| US7867923B2 (en) * | 2007-10-22 | 2011-01-11 | Applied Materials, Inc. | High quality silicon oxide films by remote plasma CVD from disilane precursors |

| US7678715B2 (en) * | 2007-12-21 | 2010-03-16 | Applied Materials, Inc. | Low wet etch rate silicon nitride film |

| KR101002474B1 (ko) * | 2007-12-28 | 2010-12-17 | 주식회사 하이닉스반도체 | 반도체 메모리 소자의 소자 분리막 형성 방법 |

| US8357435B2 (en) | 2008-05-09 | 2013-01-22 | Applied Materials, Inc. | Flowable dielectric equipment and processes |

| US7972968B2 (en) * | 2008-08-18 | 2011-07-05 | Applied Materials, Inc. | High density plasma gapfill deposition-etch-deposition process etchant |

| JP5514420B2 (ja) * | 2008-09-17 | 2014-06-04 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置の製造方法 |

| CN101752292B (zh) * | 2008-12-19 | 2012-12-19 | 中芯国际集成电路制造(上海)有限公司 | 浅沟槽隔离结构的制造方法 |

| CN101752291B (zh) * | 2008-12-22 | 2013-10-09 | 中芯国际集成电路制造(上海)有限公司 | 浅沟槽隔离结构的制造方法 |

| CN102768933B (zh) * | 2009-01-31 | 2017-06-30 | 应用材料公司 | 用于蚀刻的方法 |

| JP5710591B2 (ja) * | 2009-04-20 | 2015-04-30 | アプライド マテリアルズ インコーポレイテッドApplied Materials,Incorporated | プロセスチャンバ壁上にシリコンコーティングを使用した残留フッ素ラジカルの除去の促進 |

| US8980382B2 (en) | 2009-12-02 | 2015-03-17 | Applied Materials, Inc. | Oxygen-doping for non-carbon radical-component CVD films |

| US8741788B2 (en) | 2009-08-06 | 2014-06-03 | Applied Materials, Inc. | Formation of silicon oxide using non-carbon flowable CVD processes |

| US7989365B2 (en) * | 2009-08-18 | 2011-08-02 | Applied Materials, Inc. | Remote plasma source seasoning |

| US20110136347A1 (en) * | 2009-10-21 | 2011-06-09 | Applied Materials, Inc. | Point-of-use silylamine generation |

| US8449942B2 (en) | 2009-11-12 | 2013-05-28 | Applied Materials, Inc. | Methods of curing non-carbon flowable CVD films |

| KR20120111738A (ko) * | 2009-12-30 | 2012-10-10 | 어플라이드 머티어리얼스, 인코포레이티드 | 융통성을 가진 질소/수소 비율을 이용하여 제조된 라디칼에 의한 유전체 필름의 성장 |

| US8329262B2 (en) * | 2010-01-05 | 2012-12-11 | Applied Materials, Inc. | Dielectric film formation using inert gas excitation |

| JP2013517616A (ja) * | 2010-01-06 | 2013-05-16 | アプライド マテリアルズ インコーポレイテッド | 酸化物ライナを使用する流動可能な誘電体 |

| SG182333A1 (en) | 2010-01-07 | 2012-08-30 | Applied Materials Inc | In-situ ozone cure for radical-component cvd |

| CN102844848A (zh) * | 2010-03-05 | 2012-12-26 | 应用材料公司 | 通过自由基成分化学气相沉积的共形层 |

| US8236708B2 (en) * | 2010-03-09 | 2012-08-07 | Applied Materials, Inc. | Reduced pattern loading using bis(diethylamino)silane (C8H22N2Si) as silicon precursor |

| US8574447B2 (en) * | 2010-03-31 | 2013-11-05 | Lam Research Corporation | Inorganic rapid alternating process for silicon etch |

| US7994019B1 (en) | 2010-04-01 | 2011-08-09 | Applied Materials, Inc. | Silicon-ozone CVD with reduced pattern loading using incubation period deposition |

| US8476142B2 (en) | 2010-04-12 | 2013-07-02 | Applied Materials, Inc. | Preferential dielectric gapfill |

| US9373500B2 (en) | 2014-02-21 | 2016-06-21 | Lam Research Corporation | Plasma assisted atomic layer deposition titanium oxide for conformal encapsulation and gapfill applications |

| US9997357B2 (en) | 2010-04-15 | 2018-06-12 | Lam Research Corporation | Capped ALD films for doping fin-shaped channel regions of 3-D IC transistors |

| US9257274B2 (en) | 2010-04-15 | 2016-02-09 | Lam Research Corporation | Gapfill of variable aspect ratio features with a composite PEALD and PECVD method |

| US8637411B2 (en) | 2010-04-15 | 2014-01-28 | Novellus Systems, Inc. | Plasma activated conformal dielectric film deposition |

| US8524004B2 (en) | 2010-06-16 | 2013-09-03 | Applied Materials, Inc. | Loadlock batch ozone cure |

| US8318584B2 (en) | 2010-07-30 | 2012-11-27 | Applied Materials, Inc. | Oxide-rich liner layer for flowable CVD gapfill |

| US9285168B2 (en) | 2010-10-05 | 2016-03-15 | Applied Materials, Inc. | Module for ozone cure and post-cure moisture treatment |

| US8664127B2 (en) | 2010-10-15 | 2014-03-04 | Applied Materials, Inc. | Two silicon-containing precursors for gapfill enhancing dielectric liner |

| US10283321B2 (en) | 2011-01-18 | 2019-05-07 | Applied Materials, Inc. | Semiconductor processing system and methods using capacitively coupled plasma |

| US8450191B2 (en) | 2011-01-24 | 2013-05-28 | Applied Materials, Inc. | Polysilicon films by HDP-CVD |

| US8716154B2 (en) | 2011-03-04 | 2014-05-06 | Applied Materials, Inc. | Reduced pattern loading using silicon oxide multi-layers |

| JP5661523B2 (ja) * | 2011-03-18 | 2015-01-28 | 東京エレクトロン株式会社 | 成膜方法及び成膜装置 |

| US8445078B2 (en) | 2011-04-20 | 2013-05-21 | Applied Materials, Inc. | Low temperature silicon oxide conversion |

| US8912096B2 (en) * | 2011-04-28 | 2014-12-16 | Applied Materials, Inc. | Methods for precleaning a substrate prior to metal silicide fabrication process |

| JP5870568B2 (ja) | 2011-05-12 | 2016-03-01 | 東京エレクトロン株式会社 | 成膜装置、プラズマ処理装置、成膜方法及び記憶媒体 |

| US8466073B2 (en) | 2011-06-03 | 2013-06-18 | Applied Materials, Inc. | Capping layer for reduced outgassing |

| US8497211B2 (en) | 2011-06-24 | 2013-07-30 | Applied Materials, Inc. | Integrated process modulation for PSG gapfill |

| US9404178B2 (en) | 2011-07-15 | 2016-08-02 | Applied Materials, Inc. | Surface treatment and deposition for reduced outgassing |

| JP5712874B2 (ja) * | 2011-09-05 | 2015-05-07 | 東京エレクトロン株式会社 | 成膜装置、成膜方法及び記憶媒体 |

| US8617989B2 (en) | 2011-09-26 | 2013-12-31 | Applied Materials, Inc. | Liner property improvement |

| US8551891B2 (en) | 2011-10-04 | 2013-10-08 | Applied Materials, Inc. | Remote plasma burn-in |

| US20130288485A1 (en) * | 2012-04-30 | 2013-10-31 | Applied Materials, Inc. | Densification for flowable films |

| SG195494A1 (en) * | 2012-05-18 | 2013-12-30 | Novellus Systems Inc | Carbon deposition-etch-ash gap fill process |

| US8889566B2 (en) | 2012-09-11 | 2014-11-18 | Applied Materials, Inc. | Low cost flowable dielectric films |

| SG2013083654A (en) | 2012-11-08 | 2014-06-27 | Novellus Systems Inc | Methods for depositing films on sensitive substrates |

| JP5939147B2 (ja) | 2012-12-14 | 2016-06-22 | 東京エレクトロン株式会社 | 成膜装置、基板処理装置及び成膜方法 |

| US9018108B2 (en) | 2013-01-25 | 2015-04-28 | Applied Materials, Inc. | Low shrinkage dielectric films |

| JP6267881B2 (ja) * | 2013-07-03 | 2018-01-24 | 東京エレクトロン株式会社 | 基板処理方法及び制御装置 |

| US9798317B2 (en) | 2013-07-03 | 2017-10-24 | Tokyo Electron Limited | Substrate processing method and control apparatus |

| US20150048477A1 (en) * | 2013-08-16 | 2015-02-19 | Taiwan Semiconductor Manufacturing Company Ltd. | Semiconductor structure and manufacturing method thereof |

| US20150206803A1 (en) * | 2014-01-19 | 2015-07-23 | United Microelectronics Corp. | Method of forming inter-level dielectric layer |

| JP2015179729A (ja) * | 2014-03-19 | 2015-10-08 | 東京エレクトロン株式会社 | シリコン酸化膜の形成方法およびその形成装置 |

| US9412581B2 (en) | 2014-07-16 | 2016-08-09 | Applied Materials, Inc. | Low-K dielectric gapfill by flowable deposition |

| US9368364B2 (en) | 2014-09-24 | 2016-06-14 | Applied Materials, Inc. | Silicon etch process with tunable selectivity to SiO2 and other materials |

| US10096464B2 (en) | 2014-10-04 | 2018-10-09 | Applied Materials, Inc. | Atomic layer deposition of high density silicon dioxide |

| US9564312B2 (en) | 2014-11-24 | 2017-02-07 | Lam Research Corporation | Selective inhibition in atomic layer deposition of silicon-containing films |

| US10566187B2 (en) | 2015-03-20 | 2020-02-18 | Lam Research Corporation | Ultrathin atomic layer deposition film accuracy thickness control |

| US20160314964A1 (en) | 2015-04-21 | 2016-10-27 | Lam Research Corporation | Gap fill using carbon-based films |

| US9627247B2 (en) * | 2015-06-03 | 2017-04-18 | Macronix International Co., Ltd. | Semiconductor device and method of fabricating the same |

| JP6584352B2 (ja) * | 2016-03-24 | 2019-10-02 | 東京エレクトロン株式会社 | 制御装置、基板処理システム、基板処理方法及びプログラム |

| KR101878665B1 (ko) * | 2016-05-26 | 2018-07-18 | 참엔지니어링(주) | 기판 처리 방법 |

| US9773643B1 (en) | 2016-06-30 | 2017-09-26 | Lam Research Corporation | Apparatus and method for deposition and etch in gap fill |

| US10062563B2 (en) | 2016-07-01 | 2018-08-28 | Lam Research Corporation | Selective atomic layer deposition with post-dose treatment |

| US10858727B2 (en) | 2016-08-19 | 2020-12-08 | Applied Materials, Inc. | High density, low stress amorphous carbon film, and process and equipment for its deposition |

| US10037884B2 (en) * | 2016-08-31 | 2018-07-31 | Lam Research Corporation | Selective atomic layer deposition for gapfill using sacrificial underlayer |

| JP6869024B2 (ja) * | 2016-12-20 | 2021-05-12 | 東京エレクトロン株式会社 | パーティクル除去方法及び基板処理方法 |

| JP6913569B2 (ja) * | 2017-08-25 | 2021-08-04 | 東京エレクトロン株式会社 | 被処理体を処理する方法 |

| US10269559B2 (en) | 2017-09-13 | 2019-04-23 | Lam Research Corporation | Dielectric gapfill of high aspect ratio features utilizing a sacrificial etch cap layer |

| US10727046B2 (en) * | 2018-07-06 | 2020-07-28 | Lam Research Corporation | Surface modified depth controlled deposition for plasma based deposition |

| US11293098B2 (en) * | 2018-07-11 | 2022-04-05 | Lam Research Corporation | Dielectric gapfill using atomic layer deposition (ALD), inhibitor plasma and etching |

| JP7018849B2 (ja) | 2018-08-17 | 2022-02-14 | 東京エレクトロン株式会社 | 成膜方法及び成膜装置 |

| TWI719361B (zh) * | 2018-11-20 | 2021-02-21 | 財團法人金屬工業研究發展中心 | 化學氣相沉積設備、用於化學氣相沉積設備之方法及非暫態電腦可讀取媒體 |

| CN111270224B (zh) * | 2018-12-04 | 2022-06-28 | 财团法人金属工业研究发展中心 | 化学气相沉积设备及用于该设备的方法和功率补偿模块 |

| US20200365596A1 (en) * | 2019-05-15 | 2020-11-19 | Micron Technology, Inc. | Semiconductor formation using hybrid oxidation |

| JP2021034515A (ja) * | 2019-08-22 | 2021-03-01 | 東京エレクトロン株式会社 | クリーニング方法及びマイクロ波プラズマ処理装置 |

| JP2021088731A (ja) * | 2019-12-02 | 2021-06-10 | キヤノントッキ株式会社 | 成膜方法及び成膜装置 |

| WO2021202808A1 (en) * | 2020-04-01 | 2021-10-07 | Lam Research Corporation | Seam mitigation and integrated liner for gap fill |

| CN111554590B (zh) * | 2020-04-16 | 2021-04-13 | 上海陛通半导体能源科技股份有限公司 | 半导体填孔真空系统及填孔方法 |

| US20220157602A1 (en) * | 2020-11-18 | 2022-05-19 | Applied Materials, Inc. | Silicon oxide gap fill using capacitively coupled plasmas |

| KR20220130026A (ko) * | 2021-03-17 | 2022-09-26 | 에이에스엠 아이피 홀딩 비.브이. | 기판 처리 방법 |

| US20230162947A1 (en) * | 2021-11-23 | 2023-05-25 | Applied Materials, Inc. | High density plasma enhanced process chamber |

| WO2024006211A1 (en) * | 2022-06-27 | 2024-01-04 | Lam Research Corporation | Deposition and etch of silicon-containing layer |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6258408B1 (en) * | 1999-07-06 | 2001-07-10 | Arun Madan | Semiconductor vacuum deposition system and method having a reel-to-reel substrate cassette |

| US6495208B1 (en) * | 1999-09-09 | 2002-12-17 | Virginia Tech Intellectual Properties, Inc. | Near-room temperature CVD synthesis of organic polymer/oxide dielectric nanocomposites |

| CN1638090A (zh) * | 2003-12-22 | 2005-07-13 | 海力士半导体有限公司 | 半导体装置的制造方法 |

Family Cites Families (105)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE3205345A1 (de) | 1982-02-15 | 1983-09-01 | Philips Patentverwaltung Gmbh, 2000 Hamburg | "verfahren zur herstellung von fluordotierten lichtleitfasern" |

| JPS61276977A (ja) | 1985-05-30 | 1986-12-06 | Canon Inc | 堆積膜形成法 |

| US4690746A (en) | 1986-02-24 | 1987-09-01 | Genus, Inc. | Interlayer dielectric process |

| US5000113A (en) | 1986-12-19 | 1991-03-19 | Applied Materials, Inc. | Thermal CVD/PECVD reactor and use for thermal chemical vapor deposition of silicon dioxide and in-situ multi-step planarized process |

| US4892753A (en) | 1986-12-19 | 1990-01-09 | Applied Materials, Inc. | Process for PECVD of silicon oxide using TEOS decomposition |

| US4872947A (en) | 1986-12-19 | 1989-10-10 | Applied Materials, Inc. | CVD of silicon oxide using TEOS decomposition and in-situ planarization process |

| US4960488A (en) | 1986-12-19 | 1990-10-02 | Applied Materials, Inc. | Reactor chamber self-cleaning process |

| KR910006164B1 (ko) | 1987-03-18 | 1991-08-16 | 가부시키가이샤 도시바 | 박막형성방법과 그 장치 |

| US4851370A (en) | 1987-12-28 | 1989-07-25 | American Telephone And Telegraph Company, At&T Bell Laboratories | Fabricating a semiconductor device with low defect density oxide |

| JPH0258836A (ja) | 1988-08-24 | 1990-02-28 | Matsushita Electric Ind Co Ltd | 半導体装置の製造方法 |

| US4894352A (en) | 1988-10-26 | 1990-01-16 | Texas Instruments Inc. | Deposition of silicon-containing films using organosilicon compounds and nitrogen trifluoride |

| US5061838A (en) | 1989-06-23 | 1991-10-29 | Massachusetts Institute Of Technology | Toroidal electron cyclotron resonance reactor |

| US5013691A (en) | 1989-07-31 | 1991-05-07 | At&T Bell Laboratories | Anisotropic deposition of silicon dioxide |

| JP2960466B2 (ja) | 1990-03-19 | 1999-10-06 | 株式会社日立製作所 | 半導体デバイスの配線絶縁膜の形成方法及びその装置 |

| US5089442A (en) | 1990-09-20 | 1992-02-18 | At&T Bell Laboratories | Silicon dioxide deposition method using a magnetic field and both sputter deposition and plasma-enhanced cvd |

| JP2640174B2 (ja) | 1990-10-30 | 1997-08-13 | 三菱電機株式会社 | 半導体装置およびその製造方法 |

| JP3206916B2 (ja) | 1990-11-28 | 2001-09-10 | 住友電気工業株式会社 | 欠陥濃度低減方法、紫外線透過用光学ガラスの製造方法及び紫外線透過用光学ガラス |

| EP0519079B1 (en) | 1991-01-08 | 1999-03-03 | Fujitsu Limited | Process for forming silicon oxide film |

| JP2697315B2 (ja) | 1991-01-23 | 1998-01-14 | 日本電気株式会社 | フッ素含有シリコン酸化膜の形成方法 |

| JPH04341568A (ja) | 1991-05-16 | 1992-11-27 | Toshiba Corp | 薄膜形成方法及び薄膜形成装置 |

| JP2699695B2 (ja) | 1991-06-07 | 1998-01-19 | 日本電気株式会社 | 化学気相成長法 |

| US5279865A (en) | 1991-06-28 | 1994-01-18 | Digital Equipment Corporation | High throughput interlevel dielectric gap filling process |

| JPH05226480A (ja) | 1991-12-04 | 1993-09-03 | Nec Corp | 半導体装置の製造方法 |

| US5290382A (en) | 1991-12-13 | 1994-03-01 | Hughes Aircraft Company | Methods and apparatus for generating a plasma for "downstream" rapid shaping of surfaces of substrates and films |

| JP2773530B2 (ja) | 1992-04-15 | 1998-07-09 | 日本電気株式会社 | 半導体装置の製造方法 |

| JP2792335B2 (ja) | 1992-05-27 | 1998-09-03 | 日本電気株式会社 | 半導体装置の製造方法 |

| US5252178A (en) | 1992-06-24 | 1993-10-12 | Texas Instruments Incorporated | Multi-zone plasma processing method and apparatus |

| JP3688726B2 (ja) | 1992-07-17 | 2005-08-31 | 株式会社東芝 | 半導体装置の製造方法 |

| US5271972A (en) | 1992-08-17 | 1993-12-21 | Applied Materials, Inc. | Method for depositing ozone/TEOS silicon oxide films of reduced surface sensitivity |

| US5756402A (en) | 1992-12-28 | 1998-05-26 | Kabushiki Kaisha Toshiba | Method of etching silicon nitride film |

| US5624582A (en) | 1993-01-21 | 1997-04-29 | Vlsi Technology, Inc. | Optimization of dry etching through the control of helium backside pressure |

| US5302233A (en) | 1993-03-19 | 1994-04-12 | Micron Semiconductor, Inc. | Method for shaping features of a semiconductor structure using chemical mechanical planarization (CMP) |

| US5416048A (en) | 1993-04-16 | 1995-05-16 | Micron Semiconductor, Inc. | Method to slope conductor profile prior to dielectric deposition to improve dielectric step-coverage |

| JPH07161703A (ja) | 1993-12-03 | 1995-06-23 | Ricoh Co Ltd | 半導体装置の製造方法 |

| US5468342A (en) | 1994-04-28 | 1995-11-21 | Cypress Semiconductor Corp. | Method of etching an oxide layer |

| US5563105A (en) | 1994-09-30 | 1996-10-08 | International Business Machines Corporation | PECVD method of depositing fluorine doped oxide using a fluorine precursor containing a glass-forming element |

| US5571576A (en) | 1995-02-10 | 1996-11-05 | Watkins-Johnson | Method of forming a fluorinated silicon oxide layer using plasma chemical vapor deposition |

| US6039851A (en) | 1995-03-22 | 2000-03-21 | Micron Technology, Inc. | Reactive sputter faceting of silicon dioxide to enhance gap fill of spaces between metal lines |

| US5571577A (en) | 1995-04-07 | 1996-11-05 | Board Of Trustees Operating Michigan State University | Method and apparatus for plasma treatment of a surface |

| US20010028922A1 (en) | 1995-06-07 | 2001-10-11 | Sandhu Gurtej S. | High throughput ILD fill process for high aspect ratio gap fill |

| US6228751B1 (en) | 1995-09-08 | 2001-05-08 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing a semiconductor device |

| US5719085A (en) | 1995-09-29 | 1998-02-17 | Intel Corporation | Shallow trench isolation technique |

| JPH09106899A (ja) | 1995-10-11 | 1997-04-22 | Anelva Corp | プラズマcvd装置及び方法並びにドライエッチング装置及び方法 |

| US5599740A (en) | 1995-11-16 | 1997-02-04 | Taiwan Semiconductor Manufacturing Company, Ltd. | Deposit-etch-deposit ozone/teos insulator layer method |

| US5679606A (en) * | 1995-12-27 | 1997-10-21 | Taiwan Semiconductor Manufacturing Company, Ltd. | method of forming inter-metal-dielectric structure |

| DE69623651T2 (de) | 1995-12-27 | 2003-04-24 | Lam Res Corp | Verfahren zur füllung von gräben auf einer halbleiterscheibe |

| US6191026B1 (en) | 1996-01-09 | 2001-02-20 | Applied Materials, Inc. | Method for submicron gap filling on a semiconductor substrate |

| US5872052A (en) | 1996-02-12 | 1999-02-16 | Micron Technology, Inc. | Planarization using plasma oxidized amorphous silicon |

| US5648175A (en) | 1996-02-14 | 1997-07-15 | Applied Materials, Inc. | Chemical vapor deposition reactor system and integrated circuit |

| US5858876A (en) | 1996-04-01 | 1999-01-12 | Chartered Semiconductor Manufacturing, Ltd. | Simultaneous deposit and etch method for forming a void-free and gap-filling insulator layer upon a patterned substrate layer |

| US5712185A (en) | 1996-04-23 | 1998-01-27 | United Microelectronics | Method for forming shallow trench isolation |

| US6170428B1 (en) | 1996-07-15 | 2001-01-09 | Applied Materials, Inc. | Symmetric tunable inductively coupled HDP-CVD reactor |

| US5661093A (en) | 1996-09-12 | 1997-08-26 | Applied Materials, Inc. | Method for the stabilization of halogen-doped films through the use of multiple sealing layers |

| US5804259A (en) | 1996-11-07 | 1998-09-08 | Applied Materials, Inc. | Method and apparatus for depositing a multilayered low dielectric constant film |

| US5939831A (en) | 1996-11-13 | 1999-08-17 | Applied Materials, Inc. | Methods and apparatus for pre-stabilized plasma generation for microwave clean applications |

| FR2756663B1 (fr) | 1996-12-04 | 1999-02-26 | Berenguer Marc | Procede de traitement d'un substrat semi-conducteur comprenant une etape de traitement de surface |

| US5953635A (en) | 1996-12-19 | 1999-09-14 | Intel Corporation | Interlayer dielectric with a composite dielectric stack |

| US5913140A (en) | 1996-12-23 | 1999-06-15 | Lam Research Corporation | Method for reduction of plasma charging damage during chemical vapor deposition |

| US5800621A (en) | 1997-02-10 | 1998-09-01 | Applied Materials, Inc. | Plasma source for HDP-CVD chamber |

| US6013584A (en) | 1997-02-19 | 2000-01-11 | Applied Materials, Inc. | Methods and apparatus for forming HDP-CVD PSG film used for advanced pre-metal dielectric layer applications |

| US5990000A (en) | 1997-02-20 | 1999-11-23 | Applied Materials, Inc. | Method and apparatus for improving gap-fill capability using chemical and physical etchbacks |

| US6190233B1 (en) | 1997-02-20 | 2001-02-20 | Applied Materials, Inc. | Method and apparatus for improving gap-fill capability using chemical and physical etchbacks |

| US6059643A (en) | 1997-02-21 | 2000-05-09 | Aplex, Inc. | Apparatus and method for polishing a flat surface using a belted polishing pad |

| US5850105A (en) | 1997-03-21 | 1998-12-15 | Advanced Micro Devices, Inc. | Substantially planar semiconductor topography using dielectrics and chemical mechanical polish |

| US6030666A (en) | 1997-03-31 | 2000-02-29 | Lam Research Corporation | Method for microwave plasma substrate heating |

| US5968610A (en) | 1997-04-02 | 1999-10-19 | United Microelectronics Corp. | Multi-step high density plasma chemical vapor deposition process |

| US6077764A (en) * | 1997-04-21 | 2000-06-20 | Applied Materials, Inc. | Process for depositing high deposition rate halogen-doped silicon oxide layer |

| US6204200B1 (en) | 1997-05-05 | 2001-03-20 | Texas Instruments Incorporated | Process scheme to form controlled airgaps between interconnect lines to reduce capacitance |

| US6189483B1 (en) | 1997-05-29 | 2001-02-20 | Applied Materials, Inc. | Process kit |

| US6136685A (en) | 1997-06-03 | 2000-10-24 | Applied Materials, Inc. | High deposition rate recipe for low dielectric constant films |

| US5937323A (en) * | 1997-06-03 | 1999-08-10 | Applied Materials, Inc. | Sequencing of the recipe steps for the optimal low-k HDP-CVD processing |

| US5872058A (en) | 1997-06-17 | 1999-02-16 | Novellus Systems, Inc. | High aspect ratio gapfill process by using HDP |

| US6150628A (en) | 1997-06-26 | 2000-11-21 | Applied Science And Technology, Inc. | Toroidal low-field reactive gas source |

| US6013191A (en) | 1997-10-27 | 2000-01-11 | Advanced Refractory Technologies, Inc. | Method of polishing CVD diamond films by oxygen plasma |

| US5976327A (en) | 1997-12-12 | 1999-11-02 | Applied Materials, Inc. | Step coverage and overhang improvement by pedestal bias voltage modulation |

| US6413583B1 (en) * | 1998-02-11 | 2002-07-02 | Applied Materials, Inc. | Formation of a liquid-like silica layer by reaction of an organosilicon compound and a hydroxyl forming compound |

| US5920792A (en) | 1998-03-19 | 1999-07-06 | Winbond Electronics Corp | High density plasma enhanced chemical vapor deposition process in combination with chemical mechanical polishing process for preparation and planarization of intemetal dielectric layers |

| US6194038B1 (en) * | 1998-03-20 | 2001-02-27 | Applied Materials, Inc. | Method for deposition of a conformal layer on a substrate |

| US6602434B1 (en) | 1998-03-27 | 2003-08-05 | Applied Materials, Inc. | Process for etching oxide using hexafluorobutadiene or related fluorocarbons and manifesting a wide process window |

| US6395150B1 (en) | 1998-04-01 | 2002-05-28 | Novellus Systems, Inc. | Very high aspect ratio gapfill using HDP |

| US6200911B1 (en) * | 1998-04-21 | 2001-03-13 | Applied Materials, Inc. | Method and apparatus for modifying the profile of narrow, high-aspect-ratio gaps using differential plasma power |

| US6030881A (en) | 1998-05-05 | 2000-02-29 | Novellus Systems, Inc. | High throughput chemical vapor deposition process capable of filling high aspect ratio structures |

| KR100296137B1 (ko) | 1998-06-16 | 2001-08-07 | 박종섭 | 보호막으로서고밀도플라즈마화학기상증착에의한절연막을갖는반도체소자제조방법 |

| US6037018A (en) | 1998-07-01 | 2000-03-14 | Taiwan Semiconductor Maufacturing Company | Shallow trench isolation filled by high density plasma chemical vapor deposition |

| US6203863B1 (en) | 1998-11-27 | 2001-03-20 | United Microelectronics Corp. | Method of gap filling |

| US6197705B1 (en) | 1999-03-18 | 2001-03-06 | Chartered Semiconductor Manufacturing Ltd. | Method of silicon oxide and silicon glass films deposition |

| US6099697A (en) | 1999-04-13 | 2000-08-08 | Applied Materials, Inc. | Method of and apparatus for restoring a support surface in a semiconductor wafer processing system |

| US6503843B1 (en) | 1999-09-21 | 2003-01-07 | Applied Materials, Inc. | Multistep chamber cleaning and film deposition process using a remote plasma that also enhances film gap fill |

| US6197691B1 (en) | 1999-11-15 | 2001-03-06 | Chartered Semiconductor Manufacturing Ltd. | Shallow trench isolation process |

| US6461980B1 (en) * | 2000-01-28 | 2002-10-08 | Applied Materials, Inc. | Apparatus and process for controlling the temperature of a substrate in a plasma reactor chamber |

| US6335288B1 (en) * | 2000-08-24 | 2002-01-01 | Applied Materials, Inc. | Gas chemistry cycling to achieve high aspect ratio gapfill with HDP-CVD |

| JP2002208629A (ja) * | 2000-11-09 | 2002-07-26 | Toshiba Corp | 半導体装置、及び、半導体装置の製造方法 |

| US6797646B2 (en) * | 2001-01-12 | 2004-09-28 | Applied Materials Inc. | Method of nitrogen doping of fluorinated silicate glass (FSG) while removing the photoresist layer |

| US6740601B2 (en) | 2001-05-11 | 2004-05-25 | Applied Materials Inc. | HDP-CVD deposition process for filling high aspect ratio gaps |

| US6846745B1 (en) | 2001-08-03 | 2005-01-25 | Novellus Systems, Inc. | High-density plasma process for filling high aspect ratio structures |

| US6596654B1 (en) | 2001-08-24 | 2003-07-22 | Novellus Systems, Inc. | Gap fill for high aspect ratio structures |

| US6794290B1 (en) | 2001-12-03 | 2004-09-21 | Novellus Systems, Inc. | Method of chemical modification of structure topography |

| US6677247B2 (en) * | 2002-01-07 | 2004-01-13 | Applied Materials Inc. | Method of increasing the etch selectivity of a contact sidewall to a preclean etchant |

| US6869880B2 (en) | 2002-01-24 | 2005-03-22 | Applied Materials, Inc. | In situ application of etch back for improved deposition into high-aspect-ratio features |

| US6908862B2 (en) | 2002-05-03 | 2005-06-21 | Applied Materials, Inc. | HDP-CVD dep/etch/dep process for improved deposition into high aspect ratio features |

| US6802944B2 (en) * | 2002-10-23 | 2004-10-12 | Applied Materials, Inc. | High density plasma CVD process for gapfill into high aspect ratio features |

| US6808748B2 (en) | 2003-01-23 | 2004-10-26 | Applied Materials, Inc. | Hydrogen assisted HDP-CVD deposition process for aggressive gap-fill technology |

| US6903031B2 (en) * | 2003-09-03 | 2005-06-07 | Applied Materials, Inc. | In-situ-etch-assisted HDP deposition using SiF4 and hydrogen |

| CN1954430B (zh) * | 2004-07-27 | 2010-12-01 | 富士通半导体股份有限公司 | 半导体装置及其制造方法 |

| JP4984558B2 (ja) * | 2006-02-08 | 2012-07-25 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法 |

-

2006

- 2006-10-27 US US11/553,772 patent/US7524750B2/en not_active Expired - Fee Related

-

2007

- 2007-04-02 SG SG200702447-4A patent/SG136873A1/en unknown

- 2007-04-03 TW TW096111859A patent/TW200802605A/zh unknown

- 2007-04-17 JP JP2007108385A patent/JP5405004B2/ja not_active Expired - Fee Related

- 2007-04-17 KR KR1020070037320A patent/KR100880967B1/ko not_active IP Right Cessation

- 2007-04-17 CN CNB2007100902636A patent/CN100539039C/zh not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6258408B1 (en) * | 1999-07-06 | 2001-07-10 | Arun Madan | Semiconductor vacuum deposition system and method having a reel-to-reel substrate cassette |

| US6495208B1 (en) * | 1999-09-09 | 2002-12-17 | Virginia Tech Intellectual Properties, Inc. | Near-room temperature CVD synthesis of organic polymer/oxide dielectric nanocomposites |

| CN1638090A (zh) * | 2003-12-22 | 2005-07-13 | 海力士半导体有限公司 | 半导体装置的制造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR100880967B1 (ko) | 2009-02-03 |

| TW200802605A (en) | 2008-01-01 |

| KR20070102960A (ko) | 2007-10-22 |

| JP2007305981A (ja) | 2007-11-22 |

| US20070243693A1 (en) | 2007-10-18 |

| US7524750B2 (en) | 2009-04-28 |

| JP5405004B2 (ja) | 2014-02-05 |

| SG136873A1 (en) | 2007-11-29 |

| CN101079379A (zh) | 2007-11-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100539039C (zh) | 集成工艺调制一种利用hdp-cvd间隙填充的新型方法 | |

| US6908862B2 (en) | HDP-CVD dep/etch/dep process for improved deposition into high aspect ratio features | |

| US7972968B2 (en) | High density plasma gapfill deposition-etch-deposition process etchant | |

| US7097886B2 (en) | Deposition process for high aspect ratio trenches | |

| JP4790170B2 (ja) | Hdp−cvdを用いて高いアスペクト比のギャップ充填を達成するためのガス化学サイクリング | |

| US6802944B2 (en) | High density plasma CVD process for gapfill into high aspect ratio features | |

| KR101027265B1 (ko) | Hdp-cvd 다단계 갭충진 프로세스 | |

| US6559026B1 (en) | Trench fill with HDP-CVD process including coupled high power density plasma deposition | |

| US7628897B2 (en) | Reactive ion etching for semiconductor device feature topography modification | |

| KR101289795B1 (ko) | 개선된 갭필 애플리케이션들을 위한 고-수율 hdp-cvd 프로세스들 | |

| US7329586B2 (en) | Gapfill using deposition-etch sequence | |

| US20070232071A1 (en) | Method to improve the step coverage and pattern loading for dielectric films | |

| JP2016503966A (ja) | 高密度プラズマを実施する窒化ケイ素間隙充填 | |

| TWI397960B (zh) | 用於減少高密度電漿製程中之蝕刻速率漂移的方法 | |

| TWI747899B (zh) | 使用感應耦合高密度電漿之介電膜的緻密化 | |

| CN101388341B (zh) | 在hdp-cvd沉积/蚀刻/沉积工艺中的杂质控制 | |

| TW201308431A (zh) | Psg間隙填充所用之整合製程調整 | |

| WO2008150900A1 (en) | Gapfill extension of hdp-cvd integrated process modulation sio2 process | |

| US20040161536A1 (en) | Method for depositing a low-k material having a controlled thickness range |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C56 | Change in the name or address of the patentee | ||

| CP01 | Change in the name or title of a patent holder |

Address after: American California Patentee after: Applied Materials Inc. Address before: American California Patentee before: Applied Materials Inc. |

|

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20090909 Termination date: 20140417 |