CN101038531A - 用于嵌入式系统中部件的共用接口 - Google Patents

用于嵌入式系统中部件的共用接口 Download PDFInfo

- Publication number

- CN101038531A CN101038531A CNA2007101035012A CN200710103501A CN101038531A CN 101038531 A CN101038531 A CN 101038531A CN A2007101035012 A CNA2007101035012 A CN A2007101035012A CN 200710103501 A CN200710103501 A CN 200710103501A CN 101038531 A CN101038531 A CN 101038531A

- Authority

- CN

- China

- Prior art keywords

- nonvolatile memory

- volatile memory

- shared

- interface

- memory controller

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

- G06F13/1694—Configuration of memory controller to different memory types

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Abstract

本发明的实施例提供了一种用于通过共用接口访问非易失性存储器控制器和易失性存储器的方法和设备。在一个实施例中,该方法包括通过共用接口的共用控制信号选定非易失性存储器控制器和易失性存储器中的一个,其中共用控制信号发布到非易失性存储器控制器和易失性存储器。该方法还包括通过共用控制信号发出指令到选定的非易失性存储器控制器和易失性存储器中的一个。

Description

技术领域

本发明一般涉及一种计算机系统。特别地,本发明涉及一种用于计算机系统中接口部件的改进后的系统和方法。

背景技术

许多现代电子设备例如蜂窝电话、PDA、便携式音乐播放器、应用设备等典型地结合了嵌入式计算机系统。嵌入式计算机系统典型地包括计算机处理器(称为主机)、非易失性存储器(例如NAND闪存和/或ROM存储器)、和例如动态随机存取存储器(DRAM)的易失性存储器。主机可以包括中央处理器(CPU)、数字信号处理器(DSP)、微控制器单元(MCU)或直接存储器存取(DMA)数据传输装置。

在一些情况下,可以提供非易失性存储器控制器(例如,NAND闪存控制器)用于访问非易失性存储器。通过提供非易失性存储器控制器,非易失性存储器的控制和管理任务从主机卸载到非易失性存储器控制器,因此简化了主机的设计并且允许主机处理嵌入式系统的其他处理需求。

其中主机、非易失性存储器控制器、非易失性存储器和易失性存储器均在嵌入式计算机系统中提供,每个部件都可以具有一个或多个用于连接到系统中其他部件的接口。为减小设计成本并实现这样一种嵌入式系统,并且为了减少这样一种嵌入式系统的能耗,就需要在保持高水平的性能的同时减少接口的引线数。

因此,就需要一种用于接口在嵌入式计算机系统中的主机、非易失性存储器和易失性存储器的改进系统和方法。

发明内容

本发明的实施例提供了一种通过共用接口访问非易失性存储器控制器和易失性存储器的方法和设备。在一个实施例中,此方法包括通过共用接口的共用控制信号来选择非易失性存储器控制器和易失性存储器中的一个,其中共用控制信号发布到非易失性存储器控制器和易失性存储器。该方法还包括通过共用控制信号发布指令到选定的非易失性存储器控制器和易失性存储器中的一个。

附图说明

因此在本发明的上述特征能够具体理解的方式下,通过参考实施例简要总结上述特征,就可以得到本发明的更加详细的描述,其中一些描述在附图中示出。然而,需要注意的是,这些附图仅仅示出了此发明的典型实施例,因此这些附图不能认为是本发明范围的限制,本发明可以允许其他等效实施例。

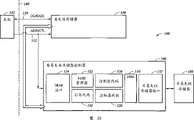

图1示出了根据本发明的一个实施例的示范性系统的框图。

图2A-C示出了根据本发明的一个实施例的系统的操作模式。

图3示出了根据本发明的一个实施例的用于嵌入式系统的共用接口。

图4示出了根据本发明的一个实施例通过共用接口使用主机访问存储器的方法的流程图。

图5示出了根据本发明的一个实施例通过共用接口使用非易失性存储器控制器访问易失性存储器的方法的流程图。

图6示出了根据本发明的一个实施例通过共用接口对易失性存储器执行同时访问的硬件的框图。

具体实施方式

本发明的实施例一般提供了一种通过共用接口访问非易失性存储器控制器和易失性存储器的方法和设备。在一个实施例中,该方法包括通过共用接口的共用控制信号来选择非易失性存储器控制器和易失性存储器中的一个,其中共用控制信号发布到非易失性存储器控制器和易失性存储器。该方法还包括通过共用控制信号发布指令到选定的非易失性存储器控制器和易失性存储器中的一个。在某些情况下,通过共用发布到非易失性存储器控制器和易失性存储器的控制信号,可以减少与非易失性存储器控制器和易失性存储器相接口的引线的数量,因此减小系统的复杂性和能耗。

下面描述关于包括主机处理器、易失性存储器和非易失性存储器的嵌入式系统的本发明的实施例。然而,在某些情况下,该嵌入式系统可以包括多个主机处理器、多个易失性存储器和/或多个非易失性存储器。易失性存储器可以包括任何类型的DRAM、SRAM或任何其他类型的易失性存储器,非易失性存储器可以包括NAND闪存、NOR闪存、可编程只读存储器(PROM)、电可擦除可编程只读存储器(EE-PROM)、只读存储器(ROM)或任何其他类型的非易失性存储器。主机处理器可以包括任何类型的处理器,包括中央处理单元(CPU)、数字信号处理器(DSP)、微控制器单元(MCU)或直接存储器存取(DMA)数据传输装置。并且,在某些情况下,系统中的每个芯片包含多个类型的处理器和/或存储器。例如,主机可以包括CPU、DSP和SRAM。在某些情况下,非易失性存储器可以包括ROM和闪存。结合本发明的实施例可以使用的其他示范性组合对于本领域普通技术人员是显而易见的。

示范性的嵌入式系统

图1示出了根据本发明的一个实施例的示范性系统100的框图。如上所述,该系统100可以包括主机102、易失性存储器104(例如,DRAM、SDRAM、DDR-SDRAM、LP-SDRAM和/或任何其他类型的易失性存储器)、非易失性存储器控制器106、和非易失性存储器108(例如,ROM、PROM、EE-PROM、NAND闪存、NOR闪存和/或任何其他类型的非易失性存储器)。在某些情况下,非易失性存储器控制器可以包含引导代码缓冲器120、NAND管理器电路122、DRAM接口124、控制器代码126、控制器内核128、DMA电路130和非易失性存储器接口132。

在一个实施例中,非易失性存储器控制器106可以使用非易失性存储器接口132访问存储于非易失性存储器108中的信息,这些信息包括引导代码、控制器代码、操系统代码、应用程序代码、数据和任何其他信息。类似地,非易失性存储器控制器106可以使用DRAM接口124访问易失性存储器104。如下所述,非易失性存储器108中的信息可以加载到引导代码缓冲器120、控制器代码缓冲器126和/或易失性存储器104并且用于系统100的初始化。例如,通过运行存储在控制器代码缓冲器126中的控制器代码,控制器内核128可以用于执行控制器操作。并且,如下所述,DMA电路130可以用于从非易失性存储器108自动传输信息到易失性存储器104。

在本发明的一个实施例中,主机102可以使用共用接口140来访问非易失性存储器108(例如,通过非易失性存储器控制器106)和易失性存储器104。如所述,共用接口140的一部分可以包括到易失性存储器104的同步串行连接(例如,快速连接、DQ/DQS 110)。共用接口140也可以包括用于提供控制信号和地址位给易失性存储器104和/或非易失性存储器控制器106的共用地址和控制线(ADR/CTL 112)。并且,也可以提供在下面更加详细描述的其他接口连接。在某些情况下,通过提供用于访问非易失性存储器控制器106和易失性存储器104的共用接口140,不需要额外的引线将主机102连接到非易失性存储器控制器106。例如,连接到非易失性存储器控制器106的地址和控制引线的每一个也可以连接到易失性存储器104。

使用共用接口的操作模式

在本发明的一个实施例中,共用接口140可以用于在多个模式中的一个中执行存储器访问。图2A-C描述了根据本发明的一个实施例的系统100的操作模式。

图2A示出了根据本发明的一个实施例,主机102访问易失性存储器104的操作的第一模式的框图。如所述,主机102可以通过共用接口140从易失性存储器读取或者写入到易失性存储器中。在主机102访问易失性存储器104的情况下,主机102可以确认指示主机102在共用接口140上作为管理者(例如,接口140启动和控制给定通信的一侧)的信号。通过确认指示主机102在接口140上作为管理者的信号,其他连接到共用接口140上的部件(例如,非易失性存储器控制器106)不可以试图同时控制接口140。例如,主机102可以利用共用地址和控制信号112来选择易失性存储器104,发布指令到易失性存储器104,并且选择易失性存储器104中的地址。在一个实施例中,主机102可以利用同步串行端口(或快速端口)传输数据到易失性存储器104并且从易失性存储器104中读取数据。在第一模式中使用的示范性信号将在下面更加具体地说明。

图2B示出了根据本发明的一个实施例,主机102访问非易失性存储器108的操作的第二模式的框图。在主机102访问非易失性存储器108的情况下,主机102可以确认指示主机102在共用接口140上作为管理者的信号。并且,主机102可以利用共用地址和控制信号112来选择非易失性存储器控制器106,发布指令到非易失性存储器控制器106,并且选择非易失性存储器108中的地址。响应于主机102通过共用接口140提供的指令和域地址,非易失性存储器控制器106可以访问非易失性存储器108中的地址,例如,通过非易失性存储器接口132。在一个实施例中,主机102可以利用异步并行端口在主机102和非易失性存储器控制器106之间传递数据,包括由非易失性存储器控制器106写入到非易失性存储器108中的数据或从非易失性存储器108读出的数据。在第二模式中使用的示范性信号将在下面更加具体地说明。

图2C示出了根据本发明的一个实施例,非易失性存储器控制器106访问易失性存储器104的操作的第三模式的框图。在非易失性存储器控制器106访问易失性存储器104的情况下,非易失性存储器控制器106可以在共用接口140上确认指示非易失性存储器控制器106作为共用接口140的管理者的信号(例如,从而防止主机102同时使用接口140)。非易失性存储器控制器106然后可以利用共用地址和控制信号112来选择易失性存储器104,发布指令到易失性存储器104,并且选择易失性存储器104中的地址。在一个实施例中,非易失性存储器控制器106可以利用异步并行端口在非易失性存储器控制器106和易失性存储器104之间传递数据。

在一个实施例中,非易失性存储器控制器可以在非易失性存储器108和易失性存储器104之间传输数据。例如,当数据从非易失性存储器108传输到易失性存储器104的情况下,非易失性存储器控制器106可以利用非易失性存储器接口132从非易失性存储器108读取数据。从非易失性存储器108读取的数据然后可以通过共用接口140从非易失性存储器控制器106写入到易失性存储器104。可以简单地通过共用接口140和非易失性存储器控制器106从易失性存储器104读取数据并且写入到非易失性存储器106。在某些情况下,非易失性存储器控制器106可以用于在非易失性存储器108和易失性存储器104之间执行直接存储器存取(DMA)传输。在第三模式中使用的示范性信号也将在下面更加具体地说明。

示范性共用接口

图3示出了根据本发明的一个实施例用于嵌入式系统100的共用接口140。如所述,接口140可以包括共用地址和控制112以及用于同步串行连接110的连接。如所述,可以将接口140连接到主机102或非易失性存储器控制器106。

在一个实施例中,用于同步串行连接110的信号可以包括芯片选择信号(CS#,“#”表示信号可以为低有效)、时钟信号(CLK)、反向时钟信号(CLK#)、时钟使能信号(CKE)、数据掩码信号(DM)、串行数据信号(DQ)、和串行数据选通信号(DQS)。

通过非易失性存储器控制器106,共用地址和控制信号112可以包括用于访问易失性存储器104的易失性存储器连接320和用于访问非易失性存储器108的非易失性存储器控制器连接322。在一个实施例中,易失性存储器连接320可以包括写使能信号(WE#)、列地址选通信号(CAS#)、行地址选通信号(RAS#)、地址总线(A[15:0])、以及存储体(bank)地址位(BA[1],BA[0])。

如所述,易失性存储器连接320也可以连接到非易失性存储器连接322。分别地,WE#连接可以在非易失性存储器连接320和易失性存储器控制器连接322之间共用,CAS#连接可以与用于非易失性存储器控制器连接322的地址锁存信号(ALE)共用,RAS#信号可以与用于非易失性存储器控制器连接322的读使能信号(RE#)共用,地址位A[15:0]可以与用于非易失性存储器控制器连接322的多路复用输入/输出引线IO[15:0]共用,BA[1]可以与用于非易失性存储器控制器连接322的芯片使能信号CE#共用,并且BA[0]可以与用于非易失性存储器控制器连接322的管理器访问信号(MA#)共用。相应的共用连接(具有示范性的主机引线编号)也在下面表1中示出。

表1:共用接口连接

| 主机引线 | 易失性存储器 | 非易失性存储器控制器 |

| 0 | WE# | WE# |

| 1 | CAS# | ALE |

| 2 | RAS# | RE# |

| 3:19 | A[15:0] | IO[15:0] |

| 20 | BA[1] | CE# |

| 21 | BA[0] | MA# |

在本发明的一个实施例中,用于非易失性存储器控制器106的芯片使能信号(CE#)306可以逻辑地从共用接口140的芯片使能信号CE#和芯片选择信号CS#导出。通过从CE#和CS#信号导出芯片使能信号CE#306,非易失性存储器控制器106可以确定主机102是否选择非易失性存储器控制器106或易失性存储器104。在某些情况下,如果CE#306信号不能从CE#和CS#信号导出,即使当非易失性存储器控制器106没有被选定,非易失性存储器控制器106也可能对共用地址和控制信号112起反应。例如,当芯片使能信号CE#降低到低逻辑电平并且当芯片选择信号CS#上升到高逻辑电平(从而取消对易失性存储器104的选定),那么就可以选定非易失性存储器控制器104(例如,芯片使能信号CE#306可以降低)。

选择电路可以包括反相CS#信号的NOT门302和将CE#信号和反相CS#信号进行逻辑或运算的OR门304。OR门304的输出可以连接到CE#信号306。在一个实施例中,该电路可以以相对主机102、易失性存储器104或非易失性存储器控制器106的分离电路的形式提供。可选地,主机102或非易失性存储器控制器106可以产生CE#信号306,利用在产生信号306的芯片的额外引线上输入或输出的必需信号。用于共用接口的传输模式的选择将参考图4-5在下面更加具体地说明。

在共用接口中选择操作模式

在本发明的一个实施例中,主机102和非易失性存储器控制器106可以使用共用接口140的CS#、CE#和MA#信号来选择接口140的管理者以及选择通过共用接口140控制哪个芯片。

图4示出了根据本发明的一个实施例通过共用接口140使用主机102访问存储器的过程400的流程图。如所述,过程400可以在步骤402开始并且接下来到请求访问存储器(例如,易失性存储器104或非易失性存储器108)的步骤404。例如,可以从额外的设备或作为主机102执行指令的结果接收这样一个请求。

当接收到请求,在步骤406做出主机102是否为共用接口140的管理者的决定。例如,通过检查由非易失性存储器控制器106输出的MA#位来做出决定。如果MA#位降低,那么非易失性存储器控制器106可以是共用接口140的管理者并且主机102可以等待直到在步骤408由非易失性存储器控制器106将MA#位升高,从而指示非易失性存储器控制器106不再是共用接口140的管理者。

一旦主机102变为共用接口140的管理者,在步骤410做出访问是否指向易失性存储器104的决定。如果做出了访问请求指向易失性存储器104的决定,那么主机可以确认CE#并且在步骤420降低CS#。通过确认CE#,可以由主机102取消对非易失性存储器控制器106的选定。通过降低CS#,可以由主机102选定易失性存储器104。那么,在步骤422,主机102可以发布访问指令到易失性存储器104,例如,通过共用接口140的共用地址和控制信号112。那么,在步骤424,可以通过易失性存储器104的一个端口(例如,使用用于同步串行端口的连接110)来执行数据存取。

如果做出了访问请求指向非易失性存储器108的决定,那么主机可以在步骤412降低CE#和确认CS#。通过降低CE#,可以由主机102选定非易失性存储器控制器106。通过确认CS#,可以由主机102取消对易失性存储器104的选定。那么,在步骤414,主机102可以发布访问指令到非易失性存储器控制器106,例如,通过共用接口140的共用地址和控制信号112。那么,在步骤416,通过非易失性存储器控制器106的一个端口(例如,使用用于异步并行端口的非易失性存储器控制器连接322)可以执行数据存取。然后,过程400在步骤430结束。

在某些情况下,非易失性存储器控制器106可以变为共用接口140的管理者并且在非易失性存储器108和易失性存储器104之间执行数据存取。例如,非易失性存储器控制器106可以使用共用接口140从易失性存储器104读取数据并且然后使用非易失性存储器接口132将这些数据写入到非易失性存储器108。非易失性存储器控制器106也可以使用非易失性存储器接口132从非易失性存储器108读取数据并且然后通过共用接口140将这些数据写入到易失性存储器104中。在某些情况下,非易失性存储器控制器106可以在非易失性存储器108和易失性存储器104之间执行DMA传输。

图5示出了根据本发明的一个实施例通过共用接口140使用非易失性存储器控制器106访问易失性存储器104的过程500的流程图。过程在步骤502开始并且接着到接收执行传输(例如,在非易失性存储器108和易失性存储器104之间的数据)的请求的步骤504。在步骤506,非易失性存储器控制器106可以检查CS#并且如果CS#为高逻辑电平则降低MA#信号(例如,意味着主机102没有使用共用总线),从而指示非易失性存储器控制器106变为共用接口140的管理者。在非易失性存储器控制器106变为共用接口140的管理者之后,非易失性存储器控制器106可以使用共用接口140执行从非易失性存储器108(例如,使用非易失性存储器接口132)到易失性存储器104的传输。例如,非易失性存储器控制器106可以从非易失性存储器控制器106的异步并行端口传输数据到易失性存储器104的异步并行端口。异步端口也可以称为慢速端口,例如,由于来自异步端口的数据是例如通过确认并且降低传输信号异步传输到端口以及从端口传输,所以它可能比利用时钟信号来传输数据的同步端口慢。

在非易失性存储器控制器106完成传输之后,非易失性存储器控制器106可以上升MA#信号,从而指示非易失性存储器控制器106不再是共用接口140的管理者。然后过程500在步骤512结束。

由于非易失性存储器控制器106在某些情况下既用于接收指令和数据(例如,来自主机102的访问指令)又用于发布指令和数据(例如,到易失性存储器104的访问指令),所以到共用接口140的一些非易失性存储器控制器106连接可以是输入输出连接(例如,双向连接可以作为输入或输出)。因此,例如,非易失性存储器控制器连接322的每一个均可以是输入输出连接。可选地,只有非易失性存储器控制器连接322的一部分可以是双向的(例如,控制访问易失性存储器104的异步端口所需的引线,例如WE#、ALE、RE#和IO[15:0]总线)。

执行与共用接口的DMA传输

根据本发明的一个实施例,共用接口140可以用于执行DMA传输,例如,从非易失性存储器106到易失性存储器104。并且,如下所述,在某些情况下,可以执行从易失性存储器108到非易失性存储器控制器106中的缓冲器的DMA传输。通过从易失性存储器108传输代码和/或数据到非易失性存储器104或缓冲器,由于易失性存储器104的访问时间典型地快于非易失性存储器108的访问时间,在某些情况下,这些代码和/或数据可以更加迅速地存取(例如,通过主机102)。在某些情况下,当从易失性存储器104存取时,由于在非易失性存储器108和易失性存储器104中都可能保留被传输的数据,所以这样的传输可以被称为代码屏蔽(code shadowing)。

作为使用共用接口执行DMA传输的一个实例,在一个实施例中,主机102可以使用共用接口140发布DMA指令到非易失性存储器控制器106请求DMA传输,例如,从非易失性存储器108中的一个位置到易失性存储器104中的一个位置。例如,每个DMA指令可以包括在非易失性存储器108中的源位置,在易失性存储器104中的目标位置以及将要传输的代码的大小。

当非易失性存储器控制器106接收DMA指令时,非易失性存储器控制器106可以承担共用接口140的控制(例如,通过降低MA#信号)。然后非易失性存储器控制器106可以执行DMA传输(例如,使用DMA电路130)从非易失性存储器108中的源位置到易失性存储器104中的目标位置。在DMA传输完成之后,非易失性存储器控制器106可以放弃共用接口140的控制(例如,通过升高MA#信号)并且允许主机102通过共用接口140从易失性存储器104存取所请求的数据。

在某些情况下,非易失性存储器控制器106可以执行从非易失性存储器108到非易失性存储器控制器106中的缓冲器的DMA传输。例如,如上面参考图1所述,非易失性存储器控制器106可以包括引导代码缓冲器120和控制器代码缓冲器126。在引导序列期间(例如,在系统100上电或重置后),非易失性存储器控制器106可以配置成自动从非易失性存储器108复制引导代码到引导代码缓冲器120。主机102然后可以通过共用接口140访问引导代码缓冲器120并且使用引导代码执行系统100的初始化操作。非易失性存储器控制器106也可以配置成自动从非易失性存储器108复制控制器代码到控制器代码缓冲器126。然后控制器代码可以由控制器内核128使用来执行控制器操作。

利用共用接口同时访问易失性存储器

在本发明的一个实施例中,共用接口140可以用于执行多个同时对易失性存储器104的访问。通过允许多个同时对易失性存储器104的访问,易失性存储器104的利用率以及存储器带宽的效率(例如,从易失性存储器104读取和写入数据的速度)可以得到提高。

例如,通过共用接口140的第一部分可以发布第一访问指令到易失性存储器中的第一存储体。当执行第一访问指令时,通过共用接口140的第二部分可以发布第二访问指令到易失性存储器中的第二存储体。在某些情况下,通过由共用接口140的各个部分发布各个指令并且通过发布使用各个控制硬件(例如,第一指令可以是读指令而第二指令可以是写指令,或者反过来)并且访问易失性存储器104的各个部分(例如,可以访问每个存储体)的指令,例如,可以成功地执行对易失性存储器104的同时访问,而没有争用共用接口的任何线和/或没有争用易失性存储器104的资源。

图6为根据本发明的一个实施例通过共用接口140对易失性存储器104执行同时访问的硬件的框图。如所述,易失性存储器104可以包括同步端口602(例如,快速端口)、阵列访问解码电路604、地址锁存电路606和异步端口608(例如,慢速端口)。如上所述,易失性存储器104的异步端口608可以连接到非易失性存储器控制器106的异步端口620。同步端口602可以连接到共用接口的同步串行连接110。阵列地址解码器电路604可以用于确定由给定的访问指令访问哪个存储器阵列616和存储体(例如,存储体0、存储体1、存储体2、存储体3等)。地址锁存电路606可以用于锁存要访问的地址(例如,通过共用接口140的共用地址和控制线112由主机102或非易失性存储器控制器106提供的地址)。

易失性存储器104还可以包括地址解码器610、同步存取电路612、和异步存取电路614。地址解码器610可以用于解码由地址锁存电路606锁存的地址。同步存取电路612可以用于通过同步端口602执行数据存取,并且异步存取电路614可以用于通过异步端口608执行数据存取。

如执行对易失性存储器104的同步存取的一个实例,易失性存储器104可以接收并锁存(例如,使用地址锁存电路606)通过共用接口140从主机102获得的第一读指令的地址。在接收到读指令之后,解码读指令(例如,使用阵列存取解码电路604和地址解码器610)。然后可以执行读指令,例如,使用同步存取电路612和同步端口602从存储器阵列616的存储体0传输要由主机102读取的数据。

当执行读指令时,可以通过共用接口140从非易失性存储器控制器106接收写指令(例如,将数据从非易失性存储器108写入到易失性存储器104的指令)。易失性存储器104可以接收并锁存(例如,使用地址锁存电路606)通过共用接口140从主机102获得的第一写指令的地址。在接收到写指令之后,解码写指令(例如,使用阵列存取解码电路604和地址解码器610)。然后可以执行写指令,例如,使用异步存取电路612和异步端口602从存储器阵列616传输要写入到易失性存储器104中的数据。因此,第一读指令和第一写指令可以同时执行。

在某些情况下,在主机102发布同时指令之前,非易失性存储器控制器106可以发布指令。并且,在某些情况下,在主机102执行写操作的同时非易失性存储器控制器106可以执行读操作。可选地,除了访问指令之外由易失性存储器104可以同时发布和执行其他指令,例如,刷新指令或更改易失性存储器104的方式寄存器的指令。

尽管前述关注于本发明的实施例,但是在不偏离其基本范围的情况下可以设计本发明的其他和进一步实施例,并且其范围由所附的权利要求所确定。

Claims (32)

1、一种用于通过共用接口访问非易失性存储器控制器和易失性存储器的方法,包括:

通过共用接口的共用控制信号选择非易失性存储器控制器和易失性存储器中的一个,其中共用控制信号发布到非易失性存储器控制器和易失性存储器;以及

通过共用控制信号发布指令到选定的非易失性存储器控制器和易失性存储器中的一个。

2、如权利要求1所述的方法,进一步包括:

从选定的非易失性存储器控制器和易失性存储器中的一个中接收数据。

3、如权利要求2所述的方法,其中选定非易失性存储器控制器,其中指令通过共用控制信号发布到非易失性存储器控制器,并且其中通过非易失性存储器控制器的异步端口接收数据。

4、如权利要求2所述的方法,其中选定易失性存储器,其中指令通过共用控制信号发布到易失性存储器,并且其中通过易失性存储器的同步端口接收数据。

5、如权利要求1所述的方法,进一步包括:

检测通过非易失性存储器控制器确认的管理者信号,其中当非易失性存储器控制器在非易失性存储器和易失性存储器之间传输数据时,管理者信号指示非易失性存储器控制器作为共用接口的管理者。

6、一种通过非易失性存储器控制器访问非易失性存储器的方法,该方法包括:

通过非易失性存储器接口发布访问指令给非易失性存储器;

通过非易失性存储器接口接收数据;以及

使用共用接口的共用控制信号传输接收的数据,其中共用控制信号发布到主机处理器和易失性存储器,并且其中接收的数据传输到主机处理器和易失性存储器中的一个。

7、如权利要求6所述的方法,进一步包括:

检测通过共用接口的共用控制信号接收的选择信号;以及

响应选择信号,通过共用接口的共用控制信号接收第一指令,其中响应第一指令发布访问指令。

8、如权利要求7所述的方法,其中通过主机处理器发布第一指令,并且其中响应第一指令将接收到的数据传输到主机处理器。

9、如权利要求6所述的方法,其中通过易失性存储器的异步端口将接收到的数据传输到易失性存储器。

10、如权利要求9所述的方法,进一步包括:

在传输接收到的数据之前,确认共用接口的共用控制信号上的管理者信号,其中管理者信号指示非易失性存储器控制器为共用接口的管理者。

11、如权利要求10所述的方法,其中所述传输为响应来自主机处理器的第一指令执行的直接存储器存取(DMA)传输。

12、一种系统,包括:

易失性存储器;

非易失性存储器;

配置为通过非易失性存储器接口访问非易失性存储器的非易失性存储器控制器;

包括共用控制信号的共用接口,其中通过共用接口由非易失性存储器控制器和易失性存储器接收共用控制信号;以及

主机处理器配置为:

选择非易失性存储器控制器和易失性存储器中的一个;以及

通过共用接口的共用控制信号发布访问指令给选定的非易失性存储器控制器和易失性存储器中的一个。

13、如权利要求12所述的系统,其中易失性存储器配置为:

确定易失性存储器是否被主机处理器选定;以及如果选定:

通过共用接口的共用控制信号接收访问指令;以及

通过同步端口传输数据到主机处理器。

14、如权利要求12所述的系统,其中非易失性存储器控制器进一步配置为:

确定非易失性存储器控制器是否被主机处理器所选定;以及如果选定:

通过共用接口的共用控制信号接收访问指令;

响应接收到访问指令对非易失性存储器中的数据进行访问。

15、如权利要求14所述的系统,其中非易失性存储器控制器进一步配置为通过主机处理器的异步端口将所访问的数据传输到主机处理器。

16、如权利要求14所述的系统,其中非易失性存储器控制器进一步配置为:

响应接收访问指令:

确认指示非易失性存储器控制器为共用接口的管理者的管理者信号;以及

通过易失性存储器的异步端口,执行从非易失性存储器到易失性存储器的所访问数据的DMA传输。

17、一种非易失性存储器控制器,包括:

非易失性存储器接口;

用于接收由主机处理器发出到非易失性存储器和易失性存储器的共用控制信号的共用接口;以及

电路配置为:

确定共用控制信号是否指示通过共用接口选定非易失性存储器控制器;

如果指示为是:

通过共用接口的共用控制信号接收访问指令;

响应接收访问指令,通过非易失性存储器接口发布访问指令到非易失性存储器;以及

通过非易失性存储器接口从非易失性存储器接收所请求的数据。

18、如权利要求17所述的非易失性存储器控制器,其中电路进一步配置为:

通过共用接口传输所请求的数据到主机处理器。

19、如权利要求18所述的非易失性存储器控制器,其中电路进一步配置为:

通过易失性存储器的异步端口将所请求的数据传输到易失性存储器。

20、如权利要求19所述的非易失性存储器控制器,其中电路进一步配置为:

在传输所请求的数据到易失性存储器之前,确认共用接口的共用控制信号上的管理者信号,其中管理者信号指示非易失性存储器控制器为共用接口的管理者。

21、一种易失性存储器,包括:

通过共用接口接收的共用控制信号;

同步端口;

异步端口;以及

电路配置为:

通过共用控制信号接收第一指令;

响应通过共用控制信号接收的第一指令,通过同步端口传输数据;

通过共用控制信号接收第二指令;以及

响应通过共用控制信号接收的第二指令,通过异步端口传输数据。

22、如权利要求21所述的易失性存储器,其中易失性存储器配置为当共用控制信号指示选定易失性存储器时,仅接收第一和第二指令。

23、如权利要求21所述的易失性存储器,其中易失性存储器配置为同时执行第一和第二指令的访问。

24、如权利要求23所述的易失性存储器,其中易失性存储器配置为当第一指令访问第一存储体并且第二指令访问第二存储体时,同时执行第一和第二指令的访问。

25、一种系统,包括:

用于存储的易失性装置;

用于存储的非易失性装置;

用于控制的装置,配置成通过用于存储接口的非易失性装置来访问用于存储的非易失性装置;

包括共用控制信号的用于接口的共用装置,其中由用于控制的装置和用于存储的易失性装置通过用于接口的共用装置来接收所述共用控制信号;

用于处理的装置,配置为:

选定用于控制的装置和用于存储的装置的其中一个;以及

通过用于接口的共用装置的共用控制信号发布访问指令给选定的用于控制的装置和用于存储的易失性装置中的一个。

26、如权利要求25所述的系统,其中用于存储的易失性装置配置为:

确定用于存储的易失性装置是否被用于处理的装置所选定;以及

如果选定:

通过用于接口的共用装置的共用控制信号接收访问指令;以及

通过用于传输的同步装置将数据传输到用于处理的装置。

27、如权利要求25所述的系统,其中用于控制的装置进一步配置为:

确定用于控制的装置是否被用于处理的装置所选定;以及

如果选定:

通过用于接口的共用装置的共用控制信号接收访问指令;以及

响应接收访问指令来访问用于存储的非易失性装置中的数据。

28、如权利要求27所述的系统,其中用于控制的装置进一步配置为:通过用于处理的装置的用于传输的异步装置,将访问的数据传输到用于处理的装置。

29、如权利要求27所述的系统,其中用于控制的装置进一步配置为:

响应接收访问指令:

确认管理者信号指示用于控制的装置为用于接口的共用装置的管理者;以及

通过用于存储的易失性装置的用于传输的异步装置,执行从用于存储的非易失性装置到用于存储的易失性装置的所访问数据的DMA传输。

30、一种用于通过共用接口访问非易失性存储器控制器和易失性存储器的方法,包括:

通过共用接口的共用控制信号选择非易失性存储器控制器和易失性存储器中的一个,其中共用控制信号发布到非易失性存储器控制器和易失性存储器;

通过共用控制信号发布指令到选定的非易失性存储器控制器和易失性存储器中的一个;以及

从选定的非易失性存储器控制器和易失性存储器中的一个接收数据,其中当选定非易失性存储器控制器时通过非易失性存储器控制器的第一端口接收数据,并且其中当选定易失性存储器时通过易失性存储器的第二端口接收数据。

31、如权利要求30所述的方法,其中第一端口为慢速端口并且其中第二端口为快速端口,其中相对于慢速端口,快速端口提供较快的数据传输速率。

32、如权利要求30所述的方法,其中第一端口为异步端口并且其中第二端口为同步端口。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/349631 | 2006-02-08 | ||

| US11/349,631 US7451263B2 (en) | 2006-02-08 | 2006-02-08 | Shared interface for components in an embedded system |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN101038531A true CN101038531A (zh) | 2007-09-19 |

Family

ID=38335344

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNA2007101035012A Pending CN101038531A (zh) | 2006-02-08 | 2007-02-08 | 用于嵌入式系统中部件的共用接口 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7451263B2 (zh) |

| JP (1) | JP4593575B2 (zh) |

| KR (1) | KR100868393B1 (zh) |

| CN (1) | CN101038531A (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104063338B (zh) * | 2013-03-18 | 2018-05-29 | 华邦电子股份有限公司 | 存取系统及存储装置 |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7490177B2 (en) * | 2006-01-23 | 2009-02-10 | Infineon Technologies Ag | System method for performing a direct memory access for automatically copying initialization boot code in a new memory architecture |

| US7441070B2 (en) * | 2006-07-06 | 2008-10-21 | Qimonda North America Corp. | Method for accessing a non-volatile memory via a volatile memory interface |

| US20080007569A1 (en) * | 2006-07-06 | 2008-01-10 | Rom-Shen Kao | Control protocol and signaling in a new memory architecture |

| US20080010420A1 (en) * | 2006-07-06 | 2008-01-10 | Rom-Shen Kao | Method for Accessing Control Registers via a Memory Device |

| US20080010419A1 (en) * | 2006-07-06 | 2008-01-10 | Rom-Shen Kao | System and Method for Issuing Commands |

| US20080147940A1 (en) * | 2006-12-18 | 2008-06-19 | Rom-Shen Kao | Method and apparatus for controlling a shared bus |

| US20090182977A1 (en) * | 2008-01-16 | 2009-07-16 | S. Aqua Semiconductor Llc | Cascaded memory arrangement |

| US8462891B2 (en) * | 2008-03-06 | 2013-06-11 | Rambus Inc. | Error detection and offset cancellation during multi-wire communication |

| US8683149B2 (en) | 2008-07-23 | 2014-03-25 | Rambus Inc. | Reconfigurable memory controller |

| US8566506B2 (en) * | 2009-08-07 | 2013-10-22 | Intel Corporation | Tracking a lifetime of write operations to a non-volatile memory storage |

| US8527664B2 (en) * | 2009-12-17 | 2013-09-03 | International Business Machines Corporation | Direct memory access with minimal host interruption |

| JP2012063874A (ja) * | 2010-09-14 | 2012-03-29 | Toshiba Corp | チップセレクト信号を切り替えるセレクタ、ストレージ装置、及び電子機器 |

| US8607089B2 (en) | 2011-05-19 | 2013-12-10 | Intel Corporation | Interface for storage device access over memory bus |

| KR101959853B1 (ko) * | 2012-04-09 | 2019-03-19 | 삼성전자주식회사 | 분할 어드레싱 방식 자기 랜덤 액세스 메모리 장치 |

| US20140164659A1 (en) * | 2012-12-06 | 2014-06-12 | Wasim Quddus | Regulating access to slave devices |

| US10338826B2 (en) * | 2013-10-15 | 2019-07-02 | Cypress Semiconductor Corporation | Managed-NAND with embedded random-access non-volatile memory |

| KR102094393B1 (ko) | 2013-11-18 | 2020-03-27 | 삼성전자주식회사 | 불휘발성 메모리 시스템 및 그것의 동작 방법 |

| KR102501753B1 (ko) * | 2015-10-30 | 2023-02-21 | 삼성전자주식회사 | 고속 부팅을 제공하는 비휘발성 메모리 장치 및 이를 포함하는 시스템 |

| US10331586B2 (en) * | 2015-10-30 | 2019-06-25 | Samsung Electronics Co., Ltd. | Nonvolatile memory device for providing fast booting and system including the same |

| US11301403B2 (en) | 2019-03-01 | 2022-04-12 | Micron Technology, Inc. | Command bus in memory |

Family Cites Families (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04311895A (ja) * | 1991-04-11 | 1992-11-04 | Hitachi Ltd | Icメモリ |

| US5359569A (en) * | 1991-10-29 | 1994-10-25 | Hitachi Ltd. | Semiconductor memory |

| JP3434106B2 (ja) * | 1995-12-01 | 2003-08-04 | シャープ株式会社 | 半導体記憶装置 |

| US6134631A (en) * | 1996-08-19 | 2000-10-17 | Hyundai Electronics America, Inc. | Non-volatile memory with embedded programmable controller |

| US6055609A (en) * | 1997-06-19 | 2000-04-25 | Chips & Technologies, Inc. | Apparatus and method for improving bus usage in a system having a shared memory |

| JP2001142712A (ja) * | 1999-11-12 | 2001-05-25 | Nec Ic Microcomput Syst Ltd | 起動制御装置 |

| DE19957181A1 (de) * | 1999-11-27 | 2001-05-31 | Bosch Gmbh Robert | Verfahren und Vorrichtung zur Ansteuerung wenigstens eines Verbrauchers |

| US6681310B1 (en) * | 1999-11-29 | 2004-01-20 | Microsoft Corporation | Storage management system having common volume manager |

| JP3871184B2 (ja) * | 2000-06-12 | 2007-01-24 | シャープ株式会社 | 半導体記憶装置 |

| JP2002312232A (ja) * | 2001-04-10 | 2002-10-25 | Mitsubishi Electric Corp | 半導体記憶装置 |

| TWI240864B (en) * | 2001-06-13 | 2005-10-01 | Hitachi Ltd | Memory device |

| US20030014687A1 (en) * | 2001-07-10 | 2003-01-16 | Grandex International Corporation | Nonvolatile memory unit comprising a control circuit and a plurality of partially defective flash memory devices |

| KR100393619B1 (ko) * | 2001-09-07 | 2003-08-02 | 삼성전자주식회사 | 휴대 단말기의 메모리 장치 및 그 제어방법 |

| JP3756818B2 (ja) * | 2002-01-09 | 2006-03-15 | 株式会社メガチップス | メモリ制御回路および制御システム |

| JP2004102508A (ja) * | 2002-09-06 | 2004-04-02 | Renesas Technology Corp | 半導体記憶装置 |

| JP4463503B2 (ja) * | 2003-07-15 | 2010-05-19 | 株式会社ルネサステクノロジ | メモリモジュール及びメモリシステム |

| US7752380B2 (en) * | 2003-07-31 | 2010-07-06 | Sandisk Il Ltd | SDRAM memory device with an embedded NAND flash controller |

| JP4197285B2 (ja) * | 2003-09-11 | 2008-12-17 | 株式会社デジタル | メモリコントローラ |

| US6828822B1 (en) * | 2003-10-03 | 2004-12-07 | Altera Corporation | Apparatus and methods for shared memory interfaces in programmable logic devices |

| US7242389B1 (en) * | 2003-10-07 | 2007-07-10 | Microsoft Corporation | System and method for a large format collaborative display for sharing information |

| US7139909B2 (en) * | 2003-10-16 | 2006-11-21 | International Business Machines Corporation | Technique for system initial program load or boot-up of electronic devices and systems |

| DE102004004796B4 (de) * | 2004-01-30 | 2007-11-29 | Infineon Technologies Ag | Vorrichtung zur Datenübertragung zwischen Speichern |

| US20060294295A1 (en) * | 2005-06-24 | 2006-12-28 | Yukio Fukuzo | DRAM chip device well-communicated with flash memory chip and multi-chip package comprising such a device |

| US7404136B2 (en) * | 2005-07-15 | 2008-07-22 | Infineon Technologies Ag | Semiconductor memory device including a signal control device and method of operating the same |

| US7426607B2 (en) * | 2005-08-05 | 2008-09-16 | Infineon Technologies Ag | Memory system and method of operating memory system |

| US7415581B2 (en) * | 2005-10-04 | 2008-08-19 | Infineon Technologies Ag | Semiconductor memory chip |

| US7221615B2 (en) * | 2005-10-04 | 2007-05-22 | Infineon Technologies Ag | Semiconductor memory chip |

| US7490177B2 (en) * | 2006-01-23 | 2009-02-10 | Infineon Technologies Ag | System method for performing a direct memory access for automatically copying initialization boot code in a new memory architecture |

| US20080010419A1 (en) * | 2006-07-06 | 2008-01-10 | Rom-Shen Kao | System and Method for Issuing Commands |

| US20080010420A1 (en) * | 2006-07-06 | 2008-01-10 | Rom-Shen Kao | Method for Accessing Control Registers via a Memory Device |

| US20080007569A1 (en) * | 2006-07-06 | 2008-01-10 | Rom-Shen Kao | Control protocol and signaling in a new memory architecture |

| US7441070B2 (en) * | 2006-07-06 | 2008-10-21 | Qimonda North America Corp. | Method for accessing a non-volatile memory via a volatile memory interface |

-

2006

- 2006-02-08 US US11/349,631 patent/US7451263B2/en not_active Expired - Fee Related

-

2007

- 2007-02-07 JP JP2007027987A patent/JP4593575B2/ja not_active Expired - Fee Related

- 2007-02-08 KR KR1020070013277A patent/KR100868393B1/ko not_active IP Right Cessation

- 2007-02-08 CN CNA2007101035012A patent/CN101038531A/zh active Pending

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104063338B (zh) * | 2013-03-18 | 2018-05-29 | 华邦电子股份有限公司 | 存取系统及存储装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4593575B2 (ja) | 2010-12-08 |

| KR20070080844A (ko) | 2007-08-13 |

| JP2007220110A (ja) | 2007-08-30 |

| US7451263B2 (en) | 2008-11-11 |

| KR100868393B1 (ko) | 2008-11-11 |

| US20070186061A1 (en) | 2007-08-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101038531A (zh) | 用于嵌入式系统中部件的共用接口 | |

| US8589639B2 (en) | Memory management unit and memory management method for controlling a nonvolatile memory and a volatile memory | |

| JP5043302B2 (ja) | 不揮発性メモリを制御するためのコントローラ | |

| US8504784B2 (en) | Scheduling methods of phased garbage collection and housekeeping operations in a flash memory system | |

| US7725609B2 (en) | System memory device having a dual port | |

| US9052835B1 (en) | Abort function for storage devices by using a poison bit flag wherein a command for indicating which command should be aborted | |

| US20090006720A1 (en) | Scheduling phased garbage collection and house keeping operations in a flash memory system | |

| KR102321221B1 (ko) | 버퍼 상에서 메모리 동작을 제어하기 위한 장치 및 방법 | |

| US9959205B2 (en) | Shared row buffer system for asymmetric memory | |

| EP2160686B1 (en) | Phased garbage collection and house keeping operations in a flash memory system | |

| US20220245066A1 (en) | Memory system including heterogeneous memories, computer system including the memory system, and data management method thereof | |

| US9766814B2 (en) | Method and apparatus for defect management in a non-volatile memory device | |

| US11853224B2 (en) | Cache filter | |

| CN108139994B (zh) | 内存访问方法及内存控制器 | |

| US20180188976A1 (en) | Increasing read pending queue capacity to increase memory bandwidth | |

| US11586566B2 (en) | Memory protocol with command priority | |

| US20170228175A1 (en) | Memory controller, memory system managing refresh operation and operating method of the memory controller | |

| US9496009B2 (en) | Memory with bank-conflict-resolution (BCR) module including cache | |

| US20150212759A1 (en) | Storage device with multiple processing units and data processing method | |

| US11403035B2 (en) | Memory module including a controller and interfaces for communicating with a host and another memory module | |

| US11687283B2 (en) | Memory module interfaces | |

| US20120117326A1 (en) | Apparatus and method for accessing cache memory | |

| US20190065373A1 (en) | Cache buffer | |

| JPH09101917A (ja) | キャッシュメモリ制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |