CN101266982B - 半导体器件、半导体显示器件 - Google Patents

半导体器件、半导体显示器件 Download PDFInfo

- Publication number

- CN101266982B CN101266982B CN200810085387XA CN200810085387A CN101266982B CN 101266982 B CN101266982 B CN 101266982B CN 200810085387X A CN200810085387X A CN 200810085387XA CN 200810085387 A CN200810085387 A CN 200810085387A CN 101266982 B CN101266982 B CN 101266982B

- Authority

- CN

- China

- Prior art keywords

- layer

- soi layer

- bonding pad

- execution mode

- crystal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 228

- 239000013078 crystal Substances 0.000 claims abstract description 199

- 239000000758 substrate Substances 0.000 claims description 163

- 239000012535 impurity Substances 0.000 claims description 37

- 230000005540 biological transmission Effects 0.000 claims description 21

- 238000000034 method Methods 0.000 abstract description 51

- 239000000969 carrier Substances 0.000 abstract 2

- 239000010410 layer Substances 0.000 description 366

- 239000010408 film Substances 0.000 description 157

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 72

- 229910052814 silicon oxide Inorganic materials 0.000 description 63

- 150000002500 ions Chemical class 0.000 description 49

- 238000004519 manufacturing process Methods 0.000 description 44

- 238000013459 approach Methods 0.000 description 32

- 230000017105 transposition Effects 0.000 description 32

- 229910052581 Si3N4 Inorganic materials 0.000 description 27

- 239000012790 adhesive layer Substances 0.000 description 25

- 229910052710 silicon Inorganic materials 0.000 description 24

- 239000010703 silicon Substances 0.000 description 24

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 23

- 239000012212 insulator Substances 0.000 description 22

- 230000004888 barrier function Effects 0.000 description 21

- 238000005530 etching Methods 0.000 description 21

- 229910052751 metal Inorganic materials 0.000 description 21

- 239000002184 metal Substances 0.000 description 21

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 20

- 230000015572 biosynthetic process Effects 0.000 description 20

- 238000005229 chemical vapour deposition Methods 0.000 description 19

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 19

- 241000894007 species Species 0.000 description 18

- 230000000694 effects Effects 0.000 description 17

- 229910052736 halogen Inorganic materials 0.000 description 17

- 239000001257 hydrogen Substances 0.000 description 17

- 229910052739 hydrogen Inorganic materials 0.000 description 17

- 239000011229 interlayer Substances 0.000 description 17

- 230000003647 oxidation Effects 0.000 description 17

- 238000007254 oxidation reaction Methods 0.000 description 17

- 239000002800 charge carrier Substances 0.000 description 16

- 239000011521 glass Substances 0.000 description 15

- 150000002367 halogens Chemical class 0.000 description 15

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 14

- 239000007789 gas Substances 0.000 description 14

- 239000000463 material Substances 0.000 description 14

- 125000004429 atom Chemical group 0.000 description 12

- 239000012467 final product Substances 0.000 description 12

- 229910021332 silicide Inorganic materials 0.000 description 12

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 12

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 11

- 239000010949 copper Substances 0.000 description 11

- 239000001301 oxygen Substances 0.000 description 11

- 229910052760 oxygen Inorganic materials 0.000 description 11

- 238000012545 processing Methods 0.000 description 11

- 239000012528 membrane Substances 0.000 description 10

- 229910052757 nitrogen Inorganic materials 0.000 description 10

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 9

- 229910052796 boron Inorganic materials 0.000 description 9

- 229910052802 copper Inorganic materials 0.000 description 9

- 230000006870 function Effects 0.000 description 9

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 9

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 8

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 8

- OBNDGIHQAIXEAO-UHFFFAOYSA-N [O].[Si] Chemical compound [O].[Si] OBNDGIHQAIXEAO-UHFFFAOYSA-N 0.000 description 8

- 238000005516 engineering process Methods 0.000 description 8

- 229910001385 heavy metal Inorganic materials 0.000 description 8

- GPRLSGONYQIRFK-UHFFFAOYSA-N hydron Chemical compound [H+] GPRLSGONYQIRFK-UHFFFAOYSA-N 0.000 description 8

- 238000005468 ion implantation Methods 0.000 description 8

- 239000000203 mixture Substances 0.000 description 8

- 238000000926 separation method Methods 0.000 description 8

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 7

- 150000001282 organosilanes Chemical class 0.000 description 7

- 238000011282 treatment Methods 0.000 description 7

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 7

- PNEYBMLMFCGWSK-UHFFFAOYSA-N Alumina Chemical compound [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 6

- 229910052782 aluminium Inorganic materials 0.000 description 6

- -1 chlorine Chemical class 0.000 description 6

- 230000005684 electric field Effects 0.000 description 6

- 150000004767 nitrides Chemical class 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 6

- 229910021342 tungsten silicide Inorganic materials 0.000 description 6

- 235000018734 Sambucus australis Nutrition 0.000 description 5

- 244000180577 Sambucus australis Species 0.000 description 5

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 5

- OGFXBIXJCWAUCH-UHFFFAOYSA-N meso-secoisolariciresinol Natural products C1=2C=C(O)C(OC)=CC=2CC(CO)C(CO)C1C1=CC=C(O)C(OC)=C1 OGFXBIXJCWAUCH-UHFFFAOYSA-N 0.000 description 5

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 4

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 4

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical class CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 4

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 4

- 229910052785 arsenic Inorganic materials 0.000 description 4

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 4

- 239000000460 chlorine Substances 0.000 description 4

- 238000013461 design Methods 0.000 description 4

- 238000009826 distribution Methods 0.000 description 4

- 238000001678 elastic recoil detection analysis Methods 0.000 description 4

- 230000005669 field effect Effects 0.000 description 4

- 238000005247 gettering Methods 0.000 description 4

- 229910000449 hafnium oxide Inorganic materials 0.000 description 4

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 4

- 238000002161 passivation Methods 0.000 description 4

- 239000000565 sealant Substances 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 3

- 239000004411 aluminium Substances 0.000 description 3

- 238000002048 anodisation reaction Methods 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- 229910052801 chlorine Inorganic materials 0.000 description 3

- 238000010276 construction Methods 0.000 description 3

- 238000002425 crystallisation Methods 0.000 description 3

- 230000008025 crystallization Effects 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 238000000227 grinding Methods 0.000 description 3

- 238000007747 plating Methods 0.000 description 3

- 239000010453 quartz Substances 0.000 description 3

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 3

- 239000011378 shotcrete Substances 0.000 description 3

- 239000000377 silicon dioxide Substances 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- RPAJSBKBKSSMLJ-DFWYDOINSA-N (2s)-2-aminopentanedioic acid;hydrochloride Chemical compound Cl.OC(=O)[C@@H](N)CCC(O)=O RPAJSBKBKSSMLJ-DFWYDOINSA-N 0.000 description 2

- 229910017083 AlN Inorganic materials 0.000 description 2

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 2

- 229910016909 AlxOy Inorganic materials 0.000 description 2

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- 102100040844 Dual specificity protein kinase CLK2 Human genes 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- 101000749291 Homo sapiens Dual specificity protein kinase CLK2 Proteins 0.000 description 2

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 2

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 2

- 239000004568 cement Substances 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 239000011651 chromium Substances 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 238000005520 cutting process Methods 0.000 description 2

- 230000003721 exogen phase Effects 0.000 description 2

- 238000011049 filling Methods 0.000 description 2

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 2

- 230000003760 hair shine Effects 0.000 description 2

- 229960002050 hydrofluoric acid Drugs 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 229910021334 nickel silicide Inorganic materials 0.000 description 2

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 2

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- 238000009832 plasma treatment Methods 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 229920003023 plastic Polymers 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 229920002620 polyvinyl fluoride Polymers 0.000 description 2

- 229910021426 porous silicon Inorganic materials 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 239000010980 sapphire Substances 0.000 description 2

- 229910052594 sapphire Inorganic materials 0.000 description 2

- 229910000077 silane Inorganic materials 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 238000013517 stratification Methods 0.000 description 2

- 229910001936 tantalum oxide Inorganic materials 0.000 description 2

- NXHILIPIEUBEPD-UHFFFAOYSA-H tungsten hexafluoride Chemical compound F[W](F)(F)(F)(F)F NXHILIPIEUBEPD-UHFFFAOYSA-H 0.000 description 2

- 229910017073 AlLi Inorganic materials 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 102100040862 Dual specificity protein kinase CLK1 Human genes 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- 229920002430 Fibre-reinforced plastic Polymers 0.000 description 1

- 101000749294 Homo sapiens Dual specificity protein kinase CLK1 Proteins 0.000 description 1

- 229910017911 MgIn Inorganic materials 0.000 description 1

- FKNQFGJONOIPTF-UHFFFAOYSA-N Sodium cation Chemical compound [Na+] FKNQFGJONOIPTF-UHFFFAOYSA-N 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 235000011114 ammonium hydroxide Nutrition 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 125000003700 epoxy group Chemical group 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 239000011151 fibre-reinforced plastic Substances 0.000 description 1

- 239000011152 fibreglass Substances 0.000 description 1

- 239000000945 filler Substances 0.000 description 1

- 229910000040 hydrogen fluoride Inorganic materials 0.000 description 1

- 230000008676 import Effects 0.000 description 1

- 229910003437 indium oxide Inorganic materials 0.000 description 1

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000009434 installation Methods 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- XEEYBQQBJWHFJM-UHFFFAOYSA-N iron Substances [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- PQXKHYXIUOZZFA-UHFFFAOYSA-M lithium fluoride Inorganic materials [Li+].[F-] PQXKHYXIUOZZFA-UHFFFAOYSA-M 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 229910021645 metal ion Inorganic materials 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000013508 migration Methods 0.000 description 1

- 230000005012 migration Effects 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 1

- AHLBNYSZXLDEJQ-FWEHEUNISA-N orlistat Chemical compound CCCCCCCCCCC[C@H](OC(=O)[C@H](CC(C)C)NC=O)C[C@@H]1OC(=O)[C@H]1CCCCCC AHLBNYSZXLDEJQ-FWEHEUNISA-N 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000001259 photo etching Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 239000002244 precipitate Substances 0.000 description 1

- QQONPFPTGQHPMA-UHFFFAOYSA-N propylene Natural products CC=C QQONPFPTGQHPMA-UHFFFAOYSA-N 0.000 description 1

- 125000004805 propylene group Chemical group [H]C([H])([H])C([H])([*:1])C([H])([H])[*:2] 0.000 description 1

- 230000027756 respiratory electron transport chain Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 150000003839 salts Chemical class 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 150000003376 silicon Chemical class 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 229910001415 sodium ion Inorganic materials 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 239000011701 zinc Substances 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1203—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/20—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/20—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy

- H01L21/2003—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy characterised by the substrate

- H01L21/2007—Bonding of semiconductor wafers to insulating substrates or to semiconducting substrates using an intermediate insulating layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/04—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes

- H01L29/045—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes by their particular orientation of crystalline planes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/785—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

Abstract

本发明的目的在于不只是依赖于微细加工技术地实现半导体集成电路的高性能化。此外,本发明的目的还在于实现半导体集成电路的低耗电化。本发明提供一种半导体器件,其中在第一导电型的MISFET和第二导电型的MISFET中,单晶半导体层的晶面及/或晶轴互相不同。使在各个MISFET中向沟道长方向流过的载流子的迁移度增加地设定该晶面及/或晶轴。因为采用这种结构,流过MISFET的沟道的载流子的迁移度增加,所以可以实现半导体集成电路的工作的高速化。此外,可以低电压驱动,因此可以实现低耗电化。

Description

技术领域

本发明涉及具有在绝缘表面上设置半导体层的所谓SOI(Siliconon Insulator:绝缘体上硅片)结构的半导体器件。此外,本发明涉及在如玻璃衬底等具有透光性的绝缘衬底上具有SOI结构的半导体显示器件及其制造方法。

背景技术

目前正在开发使用被称为绝缘体上硅片(下面也称为SOI)的半导体衬底的集成电路,该半导体衬底在绝缘表面上设置有较薄的单晶半导体层而代替将单晶半导体锭切成薄片来制造的硅片。使用SOI衬底的集成电路因为使晶体管的漏极和衬底之间的寄生电容降低而提高半导体集成电路的性能而引人注目。

虽然SOI衬底的制造方法各种各样,但是作为兼容SOI层的高质量和高生产率(throughput)的制造方法,已知利用被称为智能切割(Smart-Cut,注册商标)的方法而形成的SOI衬底。在该SOI衬底中,将氢离子添加到成为硅层的键合片(Bond Wafer),并且在室温下将该键合片与另外的薄片(Base Wafer:支撑片)贴合在一起。当贴合时在室温下利用凡得瓦力形成坚固的接合。然后,在将支撑片和键合片贴合在一起之后,以大约500℃的温度进行加热处理,以从添加了氢离子的层分离,而在支撑片上形成硅层。

作为这种使用SOI衬底的半导体器件的一例,已知由本申请的发明者之一申请的发明(参照专利文件1)。

此外,作为在高耐热性玻璃的晶化玻璃上形成利用智能切割法而获得的单晶硅薄膜的方法,已知由本申请的发明者之一申请的发明 (参照专利文件2)。

此外,对于在硅片上形成CMOSFET,为了使N沟道型MOSFET的电子迁移度和P沟道型MOSFET的空穴迁移度调和,已知具有在(110)面的硅片上形成的PMOS和在(100)面SOI层上形成的NMOS的半导体器件(参照专利文件3)。

[专利文件1]日本专利公开2000-012864号公报

[专利文件2]日本专利公开Hei11-163363号公报

[专利文件3]日本专利公开2006-229047号公报

在半导体集成电路的技术领域中,该技术开发是以微细化为指路图而进步发展过来的。到现在为止,伴随着半导体集成电路的微细化,已实现了高速工作和低耗电化。而且,近年来,以100nm以下的设计规则制造半导体集成电路的技术已逐渐进入到实用阶段。然而,一般而言通过微细化来提高半导体集成电路的性能是有限的。随着设计规则的微细化的提高,需要超高精度的制造装置,这使设备投资额越来越大,因此从经济观点来看也是有限的。

发明内容

本发明的目的在于不只是依赖于微细加工技术地提供实现了高性能化的半导体器件。本发明的目的还在于提供实现了低耗电化的半导体器件。

此外,在专利文件2提出的技术中,如其图1所示那样,对获得了的单晶硅膜进行构图,而形成CMOS电路的PTFT的激化层、NTFT的激化层、像素矩阵电路的激化层。因此,从一个单晶硅膜来获得上述所有的激化层。

此外,在专利文件3提出的技术中,在具有(110)面的硅片上具有在(100)面SOI层上形成的NMOS,因此平坦性欠佳,且有当构成CMOS结构时的接触连接发生不良的忧虑。此外,因为是形成在硅片上,其透光性低,因此不适合用作需要透光性的装置如使用半导体元件的显示器件(半导体显示器件)等。

因此,本发明的目的在于提供不但能够确保透光性,而且n型MISFET(Metal Insulator Semiconductor(金属绝缘体半导体)型场效应晶体管,下面也称为MISFET)和p型MISFET的迁移度被提高的CMOS电路(半导体元件)以及其制造方法,并且提供具有该CMOS电路的半导体显示器件及其制造方法。

本发明之一是一种半导体器件,其中构成第一导电型的MISFET和构成第二导电型的MISFET的单晶半导体层的晶面不同。该晶面被设为在各个MISFET中是使流向沟道长方向的载流子的迁移度增加的晶面。

本发明之一是一种半导体器件,其中在第一导电型的MISFET中和在第二导电型的MISFET中,构成MISFET的单晶半导体层的晶面和沟道长方向的晶轴不同。

本发明之一是一种半导体器件,其中构成MISFET的单晶半导体层的晶面相同,并且在第一导电型的MISFET中和在第二导电型的MISFET中,该单晶半导体层的沟道长方向的晶轴不同。

作为上述结构的优选方式是一种半导体器件,它具有所谓的SOI结构,该SOI结构是在同一个表面上形成的第一单晶半导体层及第二单晶半导体层分别由第一氧化硅膜和第二氧化硅膜的接合而固定。

本发明之一是一种半导体元件及包括该半导体元件的显示器件(半导体显示器件),其中在该半导体元件中,在玻璃衬底等具有透光性的绝缘衬底的同一个表面上设置多个单晶半导体,该单晶半导体包括:具有n型杂质区的第一SOI层;具有p型杂质区的第二SOI层,其中第一SOI层的晶面和第二SOI层的晶面不同。例如,将第一SOI层的晶面设为{100},并且将第二SOI层的晶面设为{110}。注意SOI层可以表示为单晶半导体层、激活层。

在本发明中离子注入层是指对单晶半导体衬底照射离子而由离子形成具有微小的空洞的脆弱化的区域。下面将“离子注入层”也称为“脆弱层”。通过之后的加热处理使该脆弱层产生裂缝等而将该脆弱层分开,来可以将单晶半导体层从单晶半导体衬底分离。

可以通过离子掺杂法或离子注入法照射离子来形成脆弱层。

离子掺杂法是指将不进行质量分离的离子化气体在电场中加速而照射到单晶半导体衬底的方式。利用离子掺杂装置进行离子掺杂法即可。

注意,离子注入法是指将离子化气体通过离子注入装置进行质量分离而照射到单晶半导体衬底的方式。利用离子注入法对离子化氢气体进行质量分离,并选择性地对其进行加速而照射。

本发明之一的半导体元件可以通过如下的第一工序和第二工序而形成,所述第一工序包括:将选自氢或卤素的离子种添加到第一单晶半导体衬底;在上述第一单晶半导体衬底的离其表面有预定的深度区域中形成第一脆弱层;在上述第一单晶半导体衬底上通过使用有机硅烷气体的化学气相成长法形成第一氧化硅膜;对于上述第一单晶半导体衬底及上述第一氧化硅膜进行使用掩模的蚀刻,来形成其表面形成有上述第一氧化硅膜的第一单晶半导体层;中间夹着上述第一氧化硅膜将上述第一单晶半导体层和具有透光性的绝缘衬底重合;在上述重合的状态下进行加热处理,而使上述第一脆弱层产生裂缝;在使上述第一单晶半导体层残留在上述绝缘衬底上的状态下分离上述第一单晶半导体衬底。所述第二工序包括:将选自氢或卤素的离子种添加到第二单晶半导体衬底;在上述第二单晶半导体衬底的离其表面有预定的深度区域中形成第二脆弱层;在上述第二单晶半导体衬底上通过使用有机硅烷气体的化学气相成长法形成第二氧化硅膜;对于上述第二单晶半导体衬底及上述第二氧化硅膜进行使用掩模的蚀刻,来形成其表面形成有上述第二氧化硅膜的第二单晶半导体层;中间夹着上述第二氧化硅膜将上述第二单晶半导体层和上述绝缘衬底重合;在上述重合的状态下进行加热处理,而使上述第二脆弱层产生裂缝;在使上述第二单晶半导体层残留在上述绝缘衬底上的状态下分离上述第二单晶半导体衬底。

这种在使单晶半导体层残留在绝缘衬底上的状态下分离单晶半导体衬底的方法被称为转置。注意,第一工序和第二工序无论首先进 行哪一个工序都可以。换言之,可以首先将n型单晶半导体器件转置到绝缘衬底,也可以首先将p型单晶半导体器件转置到绝缘衬底。

使用有机硅烷气体形成的氧化硅膜被形成在粘合层的最上层。由这种氧化硅膜可以使单晶半导体衬底和绝缘衬底坚固地附着。

在分离单晶半导体层之后,对于单晶半导体层的表面可以进行照射激光束、加热处理、以及CMP中的任何一种或组合上述多种的方法的平坦化处理。

此外,也可以通过CMP等将单晶半导体层研磨而使其薄膜化。此时的膜厚度优选设定为5nm至25nm即可。在单晶半导体层被薄膜化的情况下,可以提高迁移度、S值,并且抑制短沟道效应。通过实现薄膜化,可以使单晶半导体膜的S值接近,因此实现薄膜化是优选的。

当实行转置时,优选使先转置的单晶半导体层的膜厚度薄于后转置的单晶半导体层的膜厚度。因此,当中间夹着氧化硅膜进行重合时,可以防止在不必要的区域上附着。

然后,为了使两个单晶半导体层的表面的高度一致,可以进行照射激光束、加热处理、以及CMP研磨中的一种或组合上述的多种方法的平坦化处理。优选使用CMP研磨。

根据本发明,通过适用使流过MISFET的沟道的载流子的迁移度增加的晶面及/或晶轴,可以使载流子的有效质量成为最轻量,因此可以使载流子的实行迁移度成为最大。结果,可以实现半导体器件的工作的高速化,并且可以使半导体器件以低电压驱动,而可以实现低耗电化。

此外,通过至少使n型MISFET和p型MISFET的晶面或晶轴不同,可以提供迁移度被提高的半导体元件等。再者,因为确保了透光性,所以该半导体元件适宜用于半导体显示器件,尤其是其显示部分或驱动电路(半导体集成电路)。本发明的半导体元件等因迁移度高而可以实现工作的高速化,并且可以低电压驱动,因而可以实现半导体器件的低耗电化。

附图说明

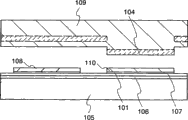

图1A至1D是说明根据实施方式1的SOI衬底的制造方法的图;

图2A和2B是说明根据实施方式1的SOI衬底的制造方法的图;

图3是说明根据实施方式1的SOI衬底的制造方法的图;

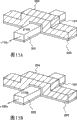

图4A和4B是说明根据实施方式2的SOI衬底的制造方法的图;

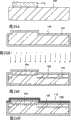

图5A和5B是说明在实施方式6中将单晶半导体层从键合衬底接合到支撑衬底的方式的图;

图6是说明在实施方式7中将单晶半导体层从键合衬底接合到支撑衬底的方式的图;

图7A和7B是说明根据实施方式8的半导体器件的制造方法的图;

图8A和8B是说明根据实施方式8的半导体器件的制造方法的图;

图9A和9B是说明根据实施方式8的半导体器件的制造方法的图;

图10A和10B是说明根据实施方式8的半导体器件的制造方法的图;

图11A和11B是说明根据实施方式8的半导体器件的制造方法的图;

图12A和12B是说明根据实施方式8的半导体器件的制造方法的图;

图13A和13B是说明根据实施方式8的半导体器件的制造方法的图;

图14A和14B是说明在实施方式10中,相对于p型MISFET和n型MISFET的SOI层的晶体定向的优选组合的一例的图;

图15A和15B是说明在实施方式10中,相对于p型MISFET和n型MISFET的SOI层的晶体定向的优选组合的一例的图;

图16是说明根据实施方式12的半导体器件的一例的微处理器的 形态的框图;

图17是说明根据实施方式13的半导体器件的一例的微型计算机的形态的框图;

图18是说明根据实施方式13的半导体器件的一例的微型计算机的外观例的立体图;

图19是说明根据实施方式13的半导体器件的一例的微型计算机的结构的截面图;

图20A至20D是说明根据实施方式3的半导体元件衬底的制造方法的图;

图21A和21B是说明根据实施方式3的半导体元件衬底的制造方法的图;

图22A至22C是说明根据实施方式3的半导体元件衬底的制造方法的图;

图23A至23D是说明根据实施方式4的半导体元件衬底的制造方法的图;

图24A至24C是说明根据实施方式5的半导体元件衬底的制造方法的图;

图25是示出根据实施方式5的半导体元件衬底的杂质浓度的图;

图26A至26D是说明根据实施方式5的半导体元件衬底的制造方法的图;

图27A和27B是说明根据实施方式9的半导体器件的制造方法的图;

图28A和28B是说明根据实施方式9的半导体器件的制造方法的图;

图29A和29B是说明根据实施方式9的半导体器件的制造方法的图;

图30A和30B是说明根据实施方式9的半导体器件的制造方法的图;

图31A和31B是说明根据实施方式9的半导体器件的制造方法 的图;

图32A和32B是说明根据实施方式9的半导体器件的制造方法的图;

图33A和33B是说明根据实施方式9的半导体器件的制造方法的图;

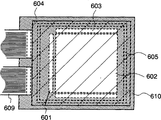

图34A和34B是说明根据实施方式11的半导体显示器件的一例的发光器件的形态的图。

具体实施方式

下面,参照附图说明本发明的实施方式。但是,本发明不局限于以下说明,所属技术领域的普通人员可以很容易地理解一个事实就是其方式和详细内容在不脱离本发明的宗旨及其范围下可以被变换为各种各样的形式。因此,本发明不应该被解释为只限定在本实施方式所记载的内容中。另外,在以下说明的本发明的结构中,在不同附图中共同使用相同符号来表示相同的部分。

实施方式1

在本实施方式中说明将构成n型MISFET和p型MISFET的半导体层从晶面不同的单晶半导体衬底(下面,也称为键合片)转置到其他衬底,即具有绝缘表面的衬底(下面,也称为支撑衬底)的相同表面的方式。在以下说明中,示出如下方式:分别对n型MISFET及p型MISFET适用使向沟道长方向流过的载流子的迁移度增加的晶面的方式;对n型MISFET适用晶面{100}的半导体层,并且对p型MISFET适用晶面{110}的半导体层。

在n型MISFET中,为了获得形成沟道形成区、源区及漏区的单晶半导体层,使用晶面{100}的键合片。在p型MISFET中,为了获得形成沟道形成区、源区及漏区的单晶半导体层,使用晶面{110}的键合片。这样,从晶面互不相同的键合片取出各晶面的单晶半导体层,并且固定于相同支撑衬底。为了固定,优选进行下面示出的工序。

在图1A中示出在第一键合片100上形成有氧化硅膜101和氮化 硅膜102的状态。第一键合片100是晶面为{100}的单晶半导体衬底。为了从第一键合片100取出单晶半导体层,以高剂量的条件向第一键合片100添加氢离子。但这样做的结果会带来使第一键合片100的表面变得粗糙的问题。因此,在之后的贴合工序中有可能不能顺利完成接合。在此,为了保护第一键合片100的表面,优选设置氧化硅膜101。氧化硅膜101优选通过热氧化而形成,例如,优选在水蒸气气氛下以900℃至1100℃进行加热处理而形成。作为氧化硅膜101的其他制造方法,可以通过氧等离子体处理使硅氧化而形成,该方法与热氧化的方法相比,可以低温度制造细致的氧化硅膜。此外,氧化硅膜101还可以通过气相成长法淀积氧化硅膜,并且通过氧等离子体处理使其表面细致化而形成,该方法与热氧化的方法相比可以低温度而制造。

在氧化硅膜101上形成氮化硅膜102。氮化硅膜102使用硅氧和氨以气相成长法淀积而形成。氮化硅膜102用作当向第一键合片100进行形成槽的加工时的硬质掩模。形成槽的加工需要顾及MISFET的半导体层的形状而进行。也就是,当对第一键合片100进行形成槽的加工时,使转置的部分成为凸状而残留,以可以将MISFET的半导体层转置到支撑衬底。如图1B所示那样,使用光致抗蚀剂形成掩模图案103,并且对氮化硅膜102及氧化硅膜101进行蚀刻,

其次,如图1C所示,使用氮化硅膜102作为硬质掩模来进行第一键合片100的蚀刻。第一键合片100的蚀刻深度根据转置到支撑衬底的单晶半导体层的厚度而决定。该单晶半导体层的厚度可以根据添加氢离子的深度来控制。在第一键合片100上形成的槽的深度优选为比脆弱层深。

在图1D中进行的氢离子添加需要顾及转置到支撑衬底的单晶半导体层的厚度而进行。该单晶半导体层的厚度为10nm至200nm,优选为10nm至50nm。当单晶半导体层的厚度薄时,可以提高迁移度和S值,并且抑制短沟道效应。当将氢离子添加到第一键合片100时,添加氢离子时的加速电压需要顾及到这种厚度。通过该处理,在第一键合片100的离其表面有一定的深度的区域中形成脆弱层104。该脆 弱层104不仅可以使用氢还可以使用稀气体,或者也可以混合两者而使用。在进行离子添加的工序之后,去除表面的氮化硅膜102。

如图2A所示,进行第一键合片100上的氧化硅膜101的表面和支撑衬底105的接合,即所谓的贴合工序。可以在低温下进行该接合,因此作为支撑衬底105可以使用各种各样的衬底,例如绝缘衬底如玻璃、石英、蓝宝石等;半导体衬底如硅、砷化镓、磷化铟等。

在支撑衬底105的表面形成有氮化硅膜106和氧化硅膜107。为了防止钠离子等杂质从支撑衬底105扩散且污染单晶半导体层而设置氮化硅膜106。为了实现该目的,可以适用氮氧化硅膜(作为其组成,氮的含量多于氧,当使用卢瑟福背散射光谱学法(RBS:RutherfordBackscattering Spectrometry))以及氢前方散射法(HFS:HydrogenForward Scattering)测量时,作为浓度范围,其包含5至30原子%的氧、20至55原子%的氮、25至35原子%的Si、10至30原子%的氢)、氮化铝、氮氧化铝等而代替氮化硅膜。在从支撑衬底105没有扩散影响到单晶半导体层的杂质时,可以省略氮化硅膜106。另一方面,设置氧化硅膜107是为了与氧化硅膜101形成接合。在此情况下,可以适用氧氮化硅膜(作为其组成,氧的含量多于氮,当使用卢瑟福背散射光谱学法以及氢前方散射法测量时,作为浓度范围,其包含50至70原子%的氧、0.5至15原子%的氮、25至35原子%的Si、0.1至10原子%的氢)而代替氧化硅膜。

通过密接其表面被清洁了的第一键合片100一侧的氧化硅膜101和支撑衬底一侧的氧化硅膜107而形成接合。在室温下可以进行该接合。该接合是原子级的接合,根据凡得瓦力的作用,可以在室温下形成坚固的接合。因为第一键合片100被加工有槽,所以形成单晶半导体层的凸状部与支撑衬底105接触。

在第一键合片100和支撑衬底105之间形成接合之后,如图2B所示那样,从第一键合片100剥离单晶半导体层,并且将其固定于支撑衬底105。单晶半导体层的剥离是通过在脆弱层104中形成的微小的空洞的体积变化而产生裂缝等,而使沿脆弱层104产生断裂面来进 行的。为了产生断裂面以使接合更坚固,优选进行400℃至600℃的加热处理。通过上述步骤,在绝缘表面上形成单晶半导体层(下面也称为SOI层)。在图2B中示出在支撑衬底105上接合第一SOI层108的状态。

当第一键合片100的晶面为{100}时,第一SOI层108的晶面也成为{100}。当要使其他晶面的SOI层形成在支撑衬底105上时,使用具有该晶面的键合片即可。

图3示出从与第一键合片100晶面不同的第二键合片109(如晶面为{110}的片)剥离单晶半导体层之后的状态。在第二键合片109中形成有脆弱层104,与第一键合片100同样,在支撑衬底105上接合有第二SOI层110。

通过上述工序,在支撑衬底105上设置晶面互不相同的第一SOI层108和第二SOI层110。在上述工序中,在第一键合片100的晶面为{100}时第一SOI层108的晶面也成为{100},并且当第二键合片109的晶面为{110}时第二SOI层110的晶面也成为{110}。为了使表面平坦化,优选对转置了的第一SOI层108及第二SOI层110进行化学机械研磨(Chemical Mechanical Polishing:CMP)。通过CMP既可以使第一SOI层108及第二SOI层110的厚度进一步薄膜化,又可以将其调制为5nm至25nm的厚度。当SOI层的厚度薄时,可以提高迁移度和S值,并且可以抑制短沟道效应。由于薄膜化可以使单晶半导体膜的S值接近,所以是优选的。

在本实施方式的结构中,可以由晶面为{100}的第一SOI层108形成n型MISFET。此外,可以由晶面为{110}的第二SOI层110形成p型MISFET。即,在每个MISFET中可以在使电子和空穴的电场效应迁移度成为最高的晶面的层上设置沟道形成区。

在本实施方式中示出在一定的深度的区域中添加氢离子等而从键合片剥离单晶半导体层的方法,但是也可以使用其他SOI技术。例如,可以通过使键合片表面阳极化来形成多孔硅质层,并且在其上通过外延生长法形成单晶硅层来用作本实施方式所示的SOI层。当使用 该结构的键合片时,使用水喷射法来使多孔硅质层和外延生长的单晶硅层分离。因此,可以获得如图2B或图3所示的设有SOI层的支撑衬底。

在本实施方式中,可以在形成半导体器件的支撑衬底上形成晶面不同的单晶半导体层(SOI层)。在设定该晶面时,使n型MISFET及p型MISFET可以获得高电场效应迁移度地决定该晶面。通过适用可以使载流子的迁移度增加的晶面及/或晶轴,可以使载流子的有效质量为最轻量,因此可以使载流子的实际的迁移度为最大。通过使用设置有这种单晶半导体层的支撑衬底,可以实现半导体器件的高性能化。

实施方式2

本实施方式将参照图4A和4B对与图1A至1C不同的键合片的制造工序进行说明。在图4A中,在第一键合片100的表面上形成氧化硅膜101、氮化硅膜102。之后,添加氢或稀有气体,或者氢和稀有气体的离子,来在第一键合片100上形成脆弱层104。然后,如图4B所示那样进行形成槽的加工。在该形成槽的加工中,槽的深度加工为深于脆弱层104,这样可以使脆弱层104只残留在要剥离的单晶半导体层的区域中。根据这种结构,可以使转置更加容易进行。

实施方式3

本实施方式说明一种半导体元件衬底的制造方法,即将构成n型MISFET和p型MISFET的SOI层从晶面不同的各键合片转置到由与键合片不同的具有透光性的绝缘衬底构成的支撑衬底的相同表面的制造方法。在本实施方式中,n型MISFET使用晶面{100}的键合片形成沟道形成区、源区及漏区。p型MISFET使用晶面{110}的键合片形成沟道形成区、源区及漏区。此外,在本实施方式中按将n型MISFET的SOI层转置到具有透光性的绝缘衬底之后,将p型MISFET的SOI层转置到该绝缘衬底的顺序而说明,但是先转置哪个都可以。

如图20A所示那样,对于晶面为{100}的第一键合片100将离子 种111添加到预定的深度的区域中,而形成脆弱层104,该离子种111是选自氢或卤素的离子种、混合它们的离子种、或者对氢或卤素混合稀有气体的离子种111。此时,如使用离子注入法可以在质量分离的状态下注入氢或卤素。向第一键合片100优选以高剂量条件(1×1015/cm2至1×1017/cm2)添加选自氢或卤素的离子种。这是因为之后在进行剥离时容易从第一键合片100取下MISFET的SOI层。注意,形成有脆弱层的预定的深度之后成为转置到绝缘衬底时的n型MISFET的SOI层的膜厚度。因此,根据离子种的添加条件,可以决定转置时的SOI层的膜厚度。当添加上述离子种时,直接添加到键合片100的方法和在键合片上形成绝缘层等的状态下进行添加的方法都可以采用。无论上述在哪一种方法中,根据添加条件,将脆弱层可以形成为与转置后的SOI层的膜厚度相同的深度。

如图20B所示那样,在第一键合片100上形成粘合层112。粘合层112使用氧化硅膜以10nm至200nm的厚度设置在最上层。氧化硅膜通过使用有机硅烷的化学气相成长法而形成。通过使用有机硅烷气体的化学气相成长法而形成的氧化硅膜的平坦性高,因此可以确实地进行在贴合工序中的接合。注意,氧化硅膜也可以通过热氧化法或等离子体CVD法形成,再者可以向通过上述任何方法形成的氧化硅膜进行等离子体处理,通过等离子体处理可以提高氧化硅膜的细致性。这样的粘合层112可以不仅仅形成在第一键合片100的上面,也可以形成在其侧面或背面。

粘合层112的最上层优选为氧化硅膜,但是除了上述氧化硅膜以外还可以具有其他膜,在键合片和氧化硅膜之间例如可以具有氧化硅膜、氮化硅膜、氧氮化硅膜。例如,当具有氧氮化硅膜时,也可以层叠氮和氧的浓度不同的氧氮化硅膜。氧浓度被提高的氧氮化硅(SiON)膜具有提高形成在最上层的氧化硅膜和其他层的附着性的功能,并且氮浓度被提高的氮氧化硅(SiNO)膜具有防止杂质污染的功能。因此,可以在第一键合片上按SiNO膜、SiON膜、氧化硅膜的顺序层叠而形成粘合层112。

注意,设置在粘合层112的最上层的氧化硅膜通过以高剂量条件的添加的结果,也具有维持其表面粗糙的第一键合片100的平坦性的功能。

如图20C所示,在第一键合片100上选择性地设置抗蚀剂等的掩模113。该掩模是考虑到之后转置的p型MISFET的SOI层的布置而设置的。如以邻接的方式设置n型MISFET的SOI层和p型MISFET的SOI层,可以简单地制造CMOS电路。

如图20D所示,使用掩模113,对第一键合片100和粘合层112进行蚀刻,来形成n型MISFET的SOI层108。SOI层108是在其上残留粘合层的状态且其形状为矩形。注意,使用掩模113先蚀刻粘合层112,然后以粘合层112为掩模来蚀刻第一键合片100。不管采用什么蚀刻方法蚀刻第一键合片100,都需要至少使脆弱层104露出。因为之后进行SOI层的转置时,需要以脆弱层为界面来剥离第一键合片100。

其次,准备具有透光性的绝缘衬底(作为支撑衬底)105。作为绝缘衬底105可以使用玻璃、石英、塑料、蓝宝石等,这些衬底对半导体显示器件而言是优选的。此外,当制造不需要透光性的器件时,作为绝缘衬底105,可以使用硅、砷化镓、磷化铟等的半导体衬底。也可以在绝缘衬底105上形成具有硅的膜。作为具有硅的膜,有氧化硅膜、氮化硅膜、氧氮化硅膜。氧化硅膜可以通过使用有机硅烷气体的化学气相成长法来形成。通过使用有机硅烷气体的化学气相成长法来形成的氧化硅膜可以提高绝缘衬底105的平坦性,并且提高与粘合层112的附着性。为了提高防止杂质污染的功能,既可以采用氮浓度被提高的氮氧化硅(SiNO)膜,又可以采用防止杂质污染性能高的氮化铝或氮氧化铝。为了提高氧氮化硅膜和其他层的附着性,也可以采用氧浓度被提高的氧氮化硅(SiON)膜。具有这种硅的膜除了化学气相成长法之外,还可以通过热氧化法或等离子体CVD法而形成。

如图21A所示那样,中间夹着被选择性地蚀刻的粘合层具有透光性的绝缘衬底105和第一键合片100重叠在一起。此时,优选对彼 此重叠的面进行冲洗。被选择性地蚀刻的粘合层的最上层设置有氧化硅膜,通过该氧化硅膜提高与绝缘衬底105的附着性。在此,当在绝缘衬底105上形成有氧化硅膜时,可以进一步提高附着性。绝缘衬底105、或绝缘衬底上的氧化硅膜和第一键合片100的接合可以在室温下进行。该接合是原子级的接合,根据凡得瓦力的作用,在室温下形成坚固的接合。为了提高附着性,可以在绝缘衬底105和第一键合片100重叠在一起的情况下,进行加热处理。通过进行加热处理,不但可以提高附着性,而且可以使脆弱层104产生裂缝,因此可以使MISFET的SO1层的提取,也就是第一键合片100的剥离变得简单。该裂缝可以由在脆弱层104中形成的微小的空洞的体积变化而产生。为了不但使接合为坚固的接合,而且使沿脆弱层104产生破裂面,优选以400℃至600℃进行大约5分钟至30分钟的加热处理,如以600℃进行20分钟的加热处理,即可。此外,除了进行加热处理之外还可以进行加压处理,也可以同时进行这两个处理。

如图21B所示,可以在绝缘衬底105上残留SOI层108,并且以脆弱层104为界面,而剥离第一键合片100。当第一键合片100的晶面为{100}时,SOI层108的晶面也为{100},于是,可以提供迁移度高的n型MISFET。

其次,如图22A所示,对于晶面为{110}的第二键合片109,与图1及2所示的工序同样地形成SOI层110。虽然是同样的工序,但在此适当地再次进行说明。首先,通过离子掺杂法或离子注入法添加选自氢或卤素的离子种而形成脆弱层,来形成粘合层112。因为粘合层112的最上层是氧化硅膜,所以可以提高与绝缘衬底105的附着性。与图1A至1D及图2A和2B的相同点是如下:优选通过使用有机硅烷气体的化学气相成长法等形成氧化硅膜;通过在绝缘衬底105上也形成具有硅的膜,可以提高与第二键合片109的附着性;可以在将绝缘衬底105和第二键合片109重叠在一起的状态下,进行加热处理来提高附着性;如进行加热处理可以使脆弱层104产生裂缝,并且除了进行加热处理以外,还可以进行加压处理,也可以同时进行该两个处 理;在不设有SOI层110的区域中脆弱层进行蚀刻而使脆弱层104露出;选择性地形成凸状的SOI层110,并且氧化硅膜设置在SOI层110的表面。

如图22B所示,将转置有SOI层108的绝缘衬底105和选择性地形成有SOI层110的第二键合片109重叠在一起。当重叠时,使SOI层110与在图20D及21A和21B所示的SOI层108邻接,这样可以简单地制造CMOS电路。

当重叠时,若使SOI层108薄于SOI层110,则可以防止在不需要的区域附着。换言之,与SOI层108的膜厚度等于SOI层110的膜厚度的情况相比,可以积极地防止SOI层108和第二键合片109附着。这样,为了使SOI层108薄于SOI层110,使在第一键合片100中的脆弱层104的深度和在第二键合片109中的脆弱层104的深度不同即可。即,使形成每个脆弱层104的剂量等不同即可。此外,因为键合片的晶面不同,即使使剂量相同,也有每个键合片的离子种的添加深度不同的情况。利用该情况,可以使每个脆弱层的深度不同。

然后,如图22C所示那样,进行第二键合片109和绝缘衬底105的剥离。由此,可以在转置有SOI层108的绝缘衬底105上残留SOI层110,并且以脆弱层104为界面剥离第二键合片109。此时,若通过上述加热处理在脆弱层104上产生有裂缝,则可以简单地进行该剥离。

也可以对转置到绝缘衬底105上的SOI层108和SOI层110进行平坦化处理。作为平坦化处理,可以使用选自照射激光束、加热处理、或CMP研磨中的任何一种或组合上述多种的方法。此外,在SOI层108的表面和SOI层110的表面的高度不同的情况下,可以保持该两者高度不同的状态,即,SOI层108的膜厚度薄于SOI层110的膜厚度的状态,也可以使两者的高度一致。而要使高度一致,仅将SO1层110削薄即可,优选使用CMP研磨将SOI层110削薄。此时也可以使两个SOI层进一步薄膜化,优选将两个SOI层研磨为5nm至25nm的厚度。如使SOI层薄膜化,可以提高迁移度和S值,并且可 以抑制短沟道效应。由于实现薄膜化可以使单晶半导体膜的S值接近,所以是优选的。

如此,通过在绝缘衬底的相同表面上转置晶面不同的n型MISFET的SOI层和p型MISFET的SOI层,可以提供上述迁移度等被提高的半导体元件及半导体集成电路。再者,因为还确保了透光性,所以该半导体集成电路等适合被用于半导体显示器件。本发明的半导体器件因为在具有透光性的绝缘衬底上转置有如迁移度等电特性高的MISFET,所以可以实现工作的高速化,且可以低电压驱动,因此可以实现低耗电化。此外,根据本实施方式,不需要形成用于元件分离的结构,因此可以使制造工序简化。

此外,在本实施方式中示出了在一定的深度中添加氢离子等,且将成为SOI层的单晶半导体层从键合片转置到支撑衬底的方法,但是也可以使用其他SOI技术制造同样的支撑衬底。例如,可以在键合片的表面通过阳极化形成多孔硅层,并且在其上通过外延生长法形成单晶硅层以用作本实施方式所示的SOI层。当使用该结构的键合片时,使用水喷射法来使多孔硅质层和外延生长的单晶硅层分离。

实施方式4

在本实施方式中,对如下制造工序进行说明,如图23A所示那样,首先对晶面为{100}的第一键合片选择性地进行蚀刻,然后如图23B所示那样,形成脆弱层,并且将晶面不同的n型MISFET的SOI层和p型MISFET的SOI层转置到相同绝缘衬底上。

如图23A所示那样,在第一键合片100上选择性地形成抗蚀剂等的掩模113。如上述实施方式所示那样,为了简单地制造CMOS电路,在设置掩模113时,需要考虑到之后转置的p型MISFET的SOI层的布置而选择性地设置掩模113。

如图23B所示,使用掩模113形成n型MISFET的SOI层108。也就是,在第一键合片100上形成成为SOI层108的凸部。之后,将与上述实施方式相同的离子种111添加到第一键合片100,来形成脆弱层104。因为在第一键合片100的离其表面有预定的深度的区域中 形成有脆弱层104,所以在成为SOI层108的区域中的脆弱层与其他区域的脆弱层相比,形成在第一键合片100的表面一侧。

如图23C所示,形成与实施方式相同的粘合层112。粘合层112沿着第一键合片100的表面而形成。换言之,覆盖SOI层108地形成粘合层112。

如图23D所示,中间夹着粘合层112,将与上述实施方式相同的绝缘衬底105重叠于第一键合片100。与上述实施方式相同的是:在粘合层112的最上层设置有氧化硅膜,通过该氧化硅膜来提高与绝缘衬底105的附着性;并且通过在绝缘衬底105上形成有氧化硅膜来提高附着性。注意,在本实施方式中,第一键合片100在SOI层108的凸部上与绝缘衬底105积极地附着。其他与上述实施方式相同的是:在将绝缘衬底105和第一键合片100重叠在一起的状态下,可以通过进行加热处理来提高附着性,并且通过加热处理,除了可以提高附着性以外,还可以使脆弱层104产生裂缝。此外,与上述实施方式同样的是:除了进行加热处理以外,还可以进行加压处理,也可以同时进行这两个处理。

然后,与上述实施方式同样地进行第一键合片100和绝缘衬底105的剥离,来形成转置有SOI层108的绝缘衬底105。然后在该绝缘衬底上转置p型MISFET的SOI层。该SOI层是根据与本实施方式相同的工序,选择性地蚀刻第二键合片,之后形成脆弱层来获得的p型MISFET的SOI层。将该SOI层转置到转置有SOI层108的绝缘衬底105上。

如此,通过在绝缘衬底的相同表面上至少转置晶面不同的n型MISFET的SOI层和p型MISFET的SOI层,可以提供迁移度被提高了的半导体集成电路等,并且因为确保了透光性,所以可以将该半导体集成电路等用于半导体显示器件。本发明的半导体显示器件因为将迁移度高的MISFET转置在具有透光性的绝缘衬底上,所以可以实现工作的高速化,且可以低电压驱动,因此可以实现低耗电化。此外,根据本实施方式,不需要形成用于元件分离的结构,所以可以使制造 工序简化。

注意,在本实施方式中,按将n型MISFET的SOI层转置到具有透光性的绝缘衬底之后,将p型MISFET的SOI层转置到该绝缘衬底的顺序而说明,但是先转置哪个都可以。

此外,在本实施方式中示出了通过在一定的深度中添加氢离子等来将单晶半导体层从键合片剥离的方法,但是也可以使用其他SOI技术制造相同的支撑衬底。例如,在键合片的表面通过阳极化形成多孔硅层,并且将在其上通过外延生长法形成的单晶硅层用作本实施方式所示的SOI层。当使用该结构的键合片时,可以使用水喷射法来使多孔硅质层和外延生长的单晶硅层分离。

实施方式5

在本实施方式中,如图24和图26所示那样,说明经过以氧化膜覆盖键合片的周围的状态的制造工序。本实施方式可以将以氧化膜覆盖之外的工序例如如上述实施方式那样,在键合片上形成脆弱层之后选择性地进行蚀刻的工序;以及如上述实施方式那样,在对键合片选择性地进行蚀刻之后形成脆弱层的工序自由组合。

在图24A中,对晶面为{100}的第一键合片100使用硫酸和过氧化氢以及纯水的混合液简称SPM(Sulfuric acid/hydrogen PeroxideMixture)、氨水和过氧化氢以及纯水的混合液简称APM(AmmoniaPeroxide Mixture)、盐酸和过氧化氢以及纯水的混合液简称HPM(Hydrochloric acid/hydrogen Peroxide Mixture)、氟酸和纯水的混合液,也叫做稀释的氢氟酸DHF(Diluted Hydrogen Fluoride)等进行冲洗。然后,进行第一键合片100的热氧化。热氧化既可以通过干式氧化形成,又可以通过在氧气气氛中添加有卤素的氧化形成。作为包含卤素的氧化典型的为含有氯的HCL,除此之外还可以适用选自HF、NF3、HBr、Cl2、ClF3、BCl3、F2、Br2等中的一种或多种。作为这种热氧化的例子,优选在相对于氧以0.5体积%至10体积%(优选为3体积%)的比率含有HCl的气氛中,以900℃至1150℃的温度进行热氧化。通过在这种温度范围内进行热处理,可以获得对于第一 键合片100中的杂质元素的由于卤素的作用来实现的吸杂效应。作为吸杂效应,获得去除尤其是金属杂质(成为外因性杂质的重金属)的效果。作为典型的重金属,可以举出Fe、Cr、Ni等的金属,有时含有Mo。此时,因氯等卤素的作用,在第一键合片100中的金属等杂质成为挥发性的盐化物,并且分离到气相中而被去除。对于其表面被化学机学研磨(CMP)处理了的第一键合片100,可以高效地去除杂质。像这样,通过使氧化膜120含有卤素,可以获得通过捕获外因性杂质的重金属来防止污染第一键合片100的效果。此外,HCl的氢具有弥补第一键合片100和氧化膜120的界面的缺陷且降低界面的局部能级密度的功能。热氧化的处理时间为0.1小时至6小时,优选为0.5小时至1小时。这样形成的氧化膜的厚度为10nm至1000nm(优选为50nm至200nm),例如为100nm。

图24B示出添加与上述实施方式相同的氢或卤素等的离子种来形成脆弱层104的工序。添加离子种可以从相对于第一键合片100的斜方向进行。注意,在对第一键合片100掺杂不被质量分离的离子且形成脆弱层104的过程中导入重金属。

图25示出添加到第一键合片100的氢或卤素离子的分布的曲线H。向第一键合片100添加的氢或卤素离子为高斯分布。当然,当将离子在电场中加速而添加到键合片时,离子以某一深度为峰值而大致成为高斯分布,在此以其峰值为基准而示出脆弱层104。在第一键合片100的表面的与离子的平均进入深度相近的深度的区域中形成脆弱层104。例如,脆弱层104的厚度优选形成为与SOI层的厚度5nm至500nm,优选为10nm至200nm适应的深度并且在添加离子时考虑到这种厚度地设定加速电压和剂量。

注意,因为重金属的离子的质量数大,所以其只在第一键合片中离子被添加的一侧的表面分布得多。因为在第一键合片100的表面上形成有氧化膜120,通过将该氧化膜120的膜厚度形成为厚于金属离子的添加深度,可以使该金属的分布不超出氧化膜120(在图25中所示的曲线M)。在其膜中含有卤素的氧化膜120通过HCl氧化等在 氧化膜120中固定捕获的该重金属,而可以防止第一键合片100的污染。

再者,通过在形成氧化膜120之后所进行的加热处理,包含在第一键合片100中其他金属的杂质析出到氧化膜120,通过使该金属与卤素(如氯)反应而被捕获。通过该步骤而在氧化膜120中固定捕获的该杂质,从而可以防止第一键合片100的污染。

这样,本实施方式的氧化膜120通过捕获重金属或杂质且防止再扩散,因此可以实现MISFET的高性能化。

注意,在将离子种质量分离之后添加到第一键合片100也可以同样形成脆弱层104。在此情况下,通过将质量大的离子(如H3 +离子)选择性地添加也可以有与上述吸杂效果同样的效果。

然后,如图24C所示那样,与上述实施方式同样地形成粘合层112,并且使用掩模113,蚀刻在脆弱层104上方的第一键合片100及粘合层112。因为与上述实施方式同样地进行之后的工序,所以省略说明。

虽然上面说明了在键合片中形成脆弱层之后选择性地进行蚀刻的工序,但是也可以采用在选择性地蚀刻键合片之后形成脆弱层的工序。如图26A所示,使用掩模113蚀刻第一键合片100。之后,如图26B所示,对于蚀刻了的第一键合片100形成氧化膜120。如上述所示形成氧化膜120。如图26C所示形成脆弱层104,并且如图26D所示形成粘合层112。因为与上述实施方式同样地进行之后的工序,所以省略说明。

如此也可以在键合片上形成氧化膜。其结果,可以吸杂当形成脆弱层时包含于键合片中的重金属和杂质等,因此可以减低键合片的污染。

实施方式6

在将晶面不同的SOI层接合于支撑衬底的情况下,作为更优选的方式,将沟道长方向的晶轴设为特定方向。通过使SOI层的晶面的晶轴的各向异性和SOI层的载流子流过的方向的晶轴的各向异性一 致,可以提高MISFET的流过沟道形成区的电子和空穴的载流子迁移度。这是由于在结晶中载流子的有效质量具有各向异性的缘故。

如图5A所示,当从晶面{100}的键合片取出n型MISFET用的SOI层时,SOI层的沟道长方向优选为与<100>方位平行的方向。注意,与<100>方位平行的方向不但有用(a)示出的方向,而且还有用(b)示出的方向,所以也可以与其中任何方向平行地取出SOI层。

另一方面,为了形成用于p型MISFET的SOI层,如图5B所示那样使用晶面{110}的键合片,并且SOI层的沟道长方向优选为与<110>方位平行的方向。如此,当n型MISFET设为<100>方位、p型MISFET设为<110>方位时,可以提高流过沟道形成区域的电子和空穴的迁移度。

实施方式7

在本实施方式中示出从具有同一个晶面的键合片取出适合于n型MISFET和p型MISFET的SOI层的结构。在图6中示出使用晶面{110}的键合片的情况。在此情况下,当取出n型MISFET用的SOI层时,将沟道长方向设为与<100>方位平行的方向。另一方面,为了形成用于p型MISFET的SOI层,将沟道长方向设为与<110>方位平行的方向。

根据本实施方式,在绝缘衬底上可以获得这样的半导体集成电路,其中形成n型MISFET的第一SOI层和形成p型MISFET的第二SOI层晶面相同,并且沟道长方向的晶轴的方向互不相同。当n型MISFET设为<100>方位、p型MISFET设为<110>方位时,可以提高流过沟道形成区域的电子和空穴的电场效应迁移度。此外,可以分别将n型MISFET的SOI层和p型MISFET的SOI层接合到支撑衬底。因此,与布置为使具有相同晶面的衬底的晶轴的方向互不相同的情况相比,确保了n型MISFET和p型MISFET的电路布置的设计的自由度,因此可以提高半导体集成电路的集成度。因为可以对n型MISFET以及p型MISFET分别选择能够获取高的电场迁移度的 晶面或晶轴,所以通过使用这样的支撑衬底,可以实现半导体集成电路的高功能化。

此外,将本发明的半导体集成电路转置在具有透光性的绝缘衬底上的半导体显示器件由于转置了迁移度高的MISFET,所以可以实现工作的高速化,并且可以低电压驱动,因此可以实现低耗电化。

实施方式8

在本实施方式中,说明使用本发明的支撑衬底来制造反相器电路的工序。注意,本发明不局限于这种单纯的电路,而可以实现微处理器等各种各样的半导体器件。在图7至13中,每个A示出反相器电路的俯视图,并且每个B示出相应于线A-B的截面图。

图7A和7B示出在设置有第一SOI层201及第二SOI层202的支撑衬底105上形成栅极绝缘层及栅电极的工序。在第一SOI层201及第二SOI层202上设置有栅电极204。作为栅极绝缘层203,适用氧化硅(SiOx)、氧氮化硅(SiOxNy)、氧化铪(HfOx)、氧化铝(AlxOy,x>y>0)、氧化钽(TaxOy,x>y>0)等材料。虽然在图7B中示出将栅极绝缘层203的侧端部和栅电极204的侧端部加工为一致,但是在栅电极204的蚀刻中,也可以使栅极绝缘层203保留。

注意,在本实施方式中,第一SOI层201相当于p型MISFET,并且第二SOI层202相当于n型MISFET。

当作为栅极绝缘层203使用高介电常数材料(high-k材料)时,由多晶硅、硅化物、金属或金属氮化物形成栅电极204。优选由金属或金属氮化物形成栅电极204。例如,由金属氮化物材料形成与栅极绝缘层203接触的第一栅电极层205,其上的第二栅电极层206使用金属材料而形成。通过使用该组合,即使使栅极绝缘层薄膜化,也可以防止在栅电极中扩大耗尽层,并且即使进行微细化,也可以防止晶体管的驱动能力欠佳。

在图8A和8B中,在栅电极204上形成第一绝缘层207。第一绝缘层207由氧化硅膜或氧氮化硅膜形成。作为其他方式,可以通过氧化或氮化处理来使栅电极204绝缘化,且形成同样的层。再者在栅 电极204的侧面上以1nm至10nm的厚度淀积形成第一绝缘层207。设置第一绝缘层207是为了在下面工序中在第一SOI层201及第二SOI层202中形成以控制价电子为目的的不添加有杂质的偏移区。

图9A和9B示出在第一SOI层201及第二SOI层202中形成超浅接合(源-漏极延长)的工序。为了抑制短沟道效应设置该超浅接合是优选的。在用于p型MISFET的第一SOI层201中形成添加有第15族元素的第一超浅接合部208,且在用于n型MISFET的第二SOI层202中形成添加有第13族元素的第二超浅接合部209。将该超浅接合部的杂质浓度设为比低浓度漏区高一位数。如,向第一超浅接合部208将硼以15keV、3×1013/cm2的剂量进行离子注入。向第二超浅接合部209将砷以15keV、2×1014/cm2的剂量进行离子注入。

其次,如图10A和10B所示,在栅电极204的侧面上形成第一侧壁210、第二侧壁211。例如,由氮化硅膜形成第一侧壁210、第二侧壁211。这种侧壁通过各向异性刻蚀以自对准的方式形成。

在此情况下,虽然可以使第一SOI层201一侧的第一侧壁210的幅度和第二SOI层202一侧的第二侧壁211的幅度相同,但是优选将该两个幅度加工为不同。优选用于p型MISFET的第一SOI层201的第一侧壁210的幅度比用于n型MISFET的第二SOI层202的第二侧壁211的幅度厚。因为在p型MISFET中,为了形成源区及漏区被注入的硼容易扩散,而容易引起短沟道效应。通过采用这种结构,在p型MISFET中,可以对源区及漏区添加高浓度的硼,并且可以使源区及漏区低电阻化。

形成侧壁之后,如图11A和11B所示,在蚀刻第一绝缘层207的露出部之后,以自对准的方式形成源区及漏区。可以通过在电场加速控制价电子的杂质离子来注入的离子注入法进行该步骤。例如,对用于p型MISFET的第一SOI层201,将硼以30keV、3×1015/cm2的剂量进行离子注入。对用于n型MISFET的第二SOI层202,将砷以50keV、5×1015/cm2的剂量进行离子注入。适当地设定离子种、加速电压及剂量的掺杂条件即可。

为了使源区及漏区进一步低电阻化,也可以形成硅化物层。作为硅化物层,适用钴硅化物或镍硅化物即可。当SOI层的厚度薄时,可以对直到该区域的SOI层的底部进行硅化物反应,来使其全部都硅化物化。

在图12A和12B中示出形成钝化层214、第一层间绝缘层215、插头216的工序。钝化层214通过CVD法将氮化硅膜、氮氧化硅膜等淀积到整个面上。第一层间绝缘层215通过CVD法淀积磷硅玻璃(PSG)或硼磷硅玻璃(BPSG),并且通过回流处理实现平坦化而形成。此外,通过CVD 法使用四乙基正硅酸盐(Tetra-Ethyl-Ortho-Silicate,Si(OCH2CH3)4)形成氧化硅膜,然后通过CMP实现平坦化。在形成插头216时,使用钨硅化物使其嵌入于在第一层间绝缘层215中形成的接触孔地来形成插头216。通过CVD法使用六氟化钨(WF6)和硅烷(SH4)形成钨硅化物。

根据半导体器件的结构考虑布线的多层化。在图13中示出在第一层间绝缘层215上设有第二层间绝缘层217、第一布线218、第二布线219、第三布线220的结构。这些布线既可以由钨硅化物形成,又可以通过金属镶嵌方法设置Cu布线。

实施方式9

在本实施方式中,说明作为通过本发明的转置步骤而形成的具有半导体元件的器件(半导体器件)的例子的反相器电路。注意,本发明不局限于这种单纯的电路,可以实现微处理器等各种各样的半导体器件。在图27至33中每个(A)示出反相器电路的俯视图,每个(B)示出相应于线A-B的截面图。

图27A和27B示出在设有粘合层112、第一SOI层108、以及第二SOI层110的绝缘衬底105上形成栅极绝缘层及栅电极的工序。在图27A中,将第一SOI层108和第二SOI层110平行地贴合在一起,但是既可以将第一SOI层108和第二SOI层110直交地贴合在一起,又可以在略微偏离平行的状态下贴合在一起。例如,在SOI层有时发生晶面的偏离或晶轴的偏离,通过在略微偏离平行的状态下贴合在一 起,可以缓和该偏离。具有晶面{110}的SOI层因为容易受到该偏离的影响,所以优选在与第二SOI层110略微偏离平行的状态下进行贴合。

注意,为了使第一SOI层108和第二SOI层110的膜厚度一致,施加平坦化处理。在第一SOI层108及第二SOI层上中间夹着栅极绝缘层203,设置栅电极204。作为栅极绝缘层203,可以适用氧化硅(SiOx)、氧氮化硅(SiOxNy)、氧化铪(HfOx)、氧化铝(AlxOy,x>y>0)、氧化钽(TaxOy,x>y>0)等材料。虽然在图27B中栅极绝缘层203的侧端部和栅电极204的侧端部被加工为一致,但是在栅电极204的蚀刻中,也可以保留栅极绝缘层203。如可以使栅极绝缘层203以锥角形而残留。

栅电极204既可以为单层结构,又可以为叠层结构。在本实施方式中示出第一栅电极层205和第二栅电极层206的叠层结构的情况。当作为栅极绝缘层203使用高介电常数材料(high-k材料)时,由多晶硅、硅化物、金属或金属氮化物形成栅电极204,优选由金属或金属氮化物形成。考虑到栅电极为叠层结构,使用金属氮化物材料形成与栅极绝缘层203接触的第一栅电极层205,并使用金属材料形成第二栅电极206。通过使用该组合,即使在使栅极绝缘层薄膜化时,也可以积极地防止栅电极中的耗尽层的扩大,并且即使在使栅极绝缘层微细化时,也可以防止晶体管的驱动能力欠佳。

在图28中示出在栅电极204上形成第一绝缘层207的工序。第一绝缘层207用作栅极绝缘层。通过CVD法或溅射法使用氧化硅膜或氧氮化硅膜形成第一绝缘层207。作为其他方式,可以通过氧化或氮化处理来使栅电极204绝缘化,而形成同样的层。在栅电极204的侧面上也以1nm至10nm的厚度形成第一绝缘层207。设置第一绝缘层207是为了在第一SOI层108及第二SOI层110中形成以控制价电子为目的的不添加有杂质的偏移区。

图29示出在第一SOI层108及第二SOI层110中形成超浅杂质(源-漏极延长)的工序。该超浅杂质有可以抑制短沟道的效应。所述 工序包括在用于n型MISFET的第一SOI层108中形成添加有第15族元素的第一超浅接合部(第一超浅杂质区)208的工序,以及在用于p型MISFET的第二SOI层110中形成添加有第13族元素的第二超浅接合部(第二超浅杂质区)209的工序。注意,在图29A中,为了明显地示出超浅接合部208、209,虽然仅仅示出栅电极204的周围的第一绝缘层207,在栅极绝缘层的外侧以虚线示出超浅接合部208、209,但是第一绝缘层207覆盖第一SOI层108、第二SOI层110、以及栅电极204的整体。该超浅杂质区的杂质浓度,例如向第一超浅接合部208将砷以15keV、2×1014/cm2的剂量进行离子注入,并且向第二超浅接合部209将硼以15keV、3×1013/cm2的剂量进行离子注入。

其次,如图30所示,在栅电极204的侧面上形成第一侧壁210、第二侧壁211。例如,由氮化硅膜形成第一侧壁210、第二侧壁211。这些侧壁通过各向异性蚀刻以自对准的方式形成。

在此情况下,虽然可以使第一SOI层108一侧的第一侧壁210的幅度和第二SOI层110一侧的第二侧壁211的幅度相同,但是优选将该两个的幅度加工为不同。优选使p型MISFET的第二SOI层110的第二侧壁211的幅度比n型MISFET的第一SOI层108的第一侧壁210的幅度厚。这是因为在p型MISFET中为了形成源区及漏区而被注入的硼容易扩散,而有容易引起短沟道效应的缘故。反而是通过采用这种结构,在p型MISFET中,可以对源区及漏区添加高浓度的硼,而可以使源区及漏区低电阻化。

形成侧壁之后,如图31所示,在蚀刻第一绝缘层207的露出部之后,以自对准的方式形成源区及漏区。可以通过在电场加速控制价电子的杂质离子来注入的离子注入法进行该步骤。在图31B中示出对第一SOI层108添加第15族元素,而形成作为源区及漏区的第一杂质区212的状态。此外,对第二SOI层110添加第13族元素,而形成作为源区及漏区的第二杂质区213。例如,对n型MISFET的第一SOI层108,将砷以50keV、5×1015/cm2的剂量进行离子注入。对p型MISFET的第二SOI层110,将硼以30keV、3×1015/cm2的剂量进 行离子注入。上述的离子种、加速电压及剂量的掺杂条件只是一例,可以适当地设定条件。

为了使源区及漏区进一步低电阻化,对于第一及第二SOI层也可以形成硅化物。作为硅化物层,适用钴硅化物或镍硅化物即可。至少使源区及漏区硅化物化即可,在SOI层的上面及端面形成硅化物层。注意,当SOI层的厚度薄等时,也可以直到该区域的SOI层的底部进行硅化物反应,来实现低电阻化。此外,为了使栅电极204进一步低电阻化,优选在栅电极层的上面形成硅化物层。可以同时制造形成在源区及漏区的硅化物层和形成在栅电极层的硅化物层。

在图32中示出形成钝化层214、第一层间绝缘层215、插头216的工序。钝化层214通过CVD法将氮化硅膜、氮氧化硅膜等淀积到整个面上。第一层间绝缘层215通过CVD法淀积磷硅玻璃(PSG)或硼磷硅玻璃(BPSG),并且通过回流处理实现平坦化而形成。此外,通过CVD法使用四乙基正硅酸盐(Tetra-Ethyl-Ortho-Silicate,Si(OCH2CH3)4)形成氧化硅膜,然后可以通过CMP实现平坦化。使用钨硅化物以嵌入在第一层间绝缘层215中形成的接触孔的方式来形成插头216。通过CVD法使用六氟化钨(WF6)和硅烷(SH4)形成钨硅化物。

根据半导体元件及使用该元件的器件的结构来考虑布线的多层化。在图33中示出在第一层间绝缘层215上设置有第二层间绝缘层217和布线218、219、220的结构。布线既可以由钨硅化物形成,又可以通过金属镶嵌方法设置Cu布线。

实施方式10

在本实施方式中例示出本发明的p型MISFET和n型MISFET的晶面及晶轴的组合。

在图14中示出从晶面不同的键合片取出构成p型MISFET和n型MISFET的SOI层的情况。图14A示出p型MISFET,其中从晶面为{110}的键合片取出SOI层。此时,更优选的方式是SOI层的沟道长方向为<110>方位。图14B示出n型MISFET,其中从晶面为 {100}的键合片取出SOI层。此时,更优选的方式是SOI层的沟道长方向为<100>方位。通过如上所述的组合可以提高电子及空穴的迁移度。

在图15中示出从晶面相同的键合片取出构成p型MISFET和n型MISFET的SOI层。图15A示出p型MISFET,其中从晶面为{110}的键合片取出SOI层。此时,更优选的方式是SOI层的沟道长方向为<110>方位。图15B示出n型MISFET,其中从晶面为{110}的键合片取出SOI层。此时,更优选的方式是SOI层的沟道长方向为<100>方位。通过如上所述的组合可以提高电子及空穴的迁移度。

根据本实施方式,在相同绝缘表面上设置n型MISFET的第一SOI层和p型MISFET的第二SOI层,并且,可以获得该两个SOI层的晶面互不相同的半导体元件。此外,即使在使用相同晶面的键合片形成n型MISFET的第一SOI层和p型MISFET的第二SOI层的情况下,也可以通过向不同的晶轴方向流过载流子,来进一步提高迁移度。通过提高MISFET的迁移度,可以实现半导体元件、及使用该元件的半导体显示器件的工作的高速化。此外,也可以低电压驱动,因此可以实现低耗电化。此外,根据本实施方式,由于不需要形成用于进行元件分离的结构,所以可以使制造工序简化。

实施方式11

在本实施方式中参照图34对作为半导体器件的一例的发光器件进行说明。图34A是发光器件的俯视图。在绝缘衬底610上设置有驱动电路部(源极侧驱动电路)601、像素部602、驱动电路部(栅极侧驱动电路)603。注意,因为被密封衬底604密封,所以以虚线示出源极侧驱动电路601、像素部602、栅极侧驱动电路603。此外,为了将绝缘衬底610和密封衬底604贴合在一起,提供有密封剂605。作为密封剂605优选使用环氧基树脂。作为用于密封衬底604的材料,除了使用玻璃衬底或石英衬底之外,还可以使用FRP(Fiberglass-Reinforced Plastics:纤维增强塑料)、PVF(聚氟乙烯)、聚酯、丙烯等构成的塑料衬底。此外,在密封剂605围绕的内侧由绝 缘衬底610和密封衬底604形成空间607。在空间中填充有填充剂,除了由惰性气体填充的情况之外(氮或氩等),还有由具有作为密封剂的功能的物质填充的情况。

注意,引导布线是用来传送输入到源极侧驱动电路601及栅极侧驱动电路603的信号的布线,并且引导布线从作为外部输入终端的FPC(柔性印刷电路)609接收视频信号、时钟信号、起始信号、复位信号等。注意,虽然在此仅示出了FPC,但该FPC也可以安装有印刷线路板(PWB)。

如图34B所示那样,从图34A所示的发光器件只取出绝缘衬底610、源极侧驱动电路601、像素部602、栅极侧驱动电路603。说明对源极侧驱动电路601及栅极侧驱动电路603转置本发明的n型MISFET的SOI层108,对像素部602转置p型MISFET的SOI层110的方式。

虽然源极侧驱动电路601及栅极侧驱动电路603可以通过转置n型MISFET及p型MISFET形成CMOS电路,但是为了提高键合衬底的布置的自由度,仅仅对源极侧驱动电路601及栅极侧驱动电路603这样的特定区域中转置n型MISFET,来形成NMOS电路。

此外,像素部602至少具有作为开关元件的开关用晶体管和电流控制用晶体管。虽然这些开关元件也可以通过转置n性MISFET及p型MISFET形成,但是为了提高键合衬底的布置的自由度,仅仅在像素部602这样的特定区域中转置p型MISFET。

再者,像素部具有包含夹在阳极和阴极之间的发光物质的层,由来自该发光物质的自发光可以进行发光器件的显示。作为用作阳极的材料,优选使用具有高功函数的材料。例如,可以使用ITO膜、含有硅的铟锡氧化物膜、包含2wt%至20wt%的氧化锌的氧化铟膜、氮化钛膜、铬膜、钨膜、Zn膜、Pt膜等的单层膜;氮化钛膜和以铝为主要成分的膜的叠层;以及氮化钛膜、以铝为主要成分的膜和氮化钛膜的三层结构等。作为用作阴极的材料,优选使用具有低功函数的材料(Al、Mg、Li、Ca、或它们的合金或化合物如MgAg、MgIn、AlLi、 LiF、CaF2等)。

当对这种半导体显示器件使用本发明的设置在绝缘衬底的相同表面的p型MISFET的第一SOI层和n型MISFET的第二SOI层时,可以进一步提高迁移度。通过提高MISFET的迁移度,可以实现半导体显示器件及用于该显示器件等的驱动电路等的半导体集成电路的工作的高速化。此外,可以低电压驱动,因此可以实现低耗电化。此外,根据本实施方式,由于不需要形成用于元件分离的结构,所以可以使制造工序简化。

实施方式12

在本实施方式中,作为具有半导体元件的器件(半导体器件)的一例,参照图16对微处理器的形态进行说明。本实施方式的半导体元件可以使用通过上述实施方式所制造的任何半导体元件。

在图16中示出微处理器221的一例。在该微处理器221中构成n型MISFET的SOI层的晶面和构成p型MISFET的SOI层的晶面不同。当然,如上述实施方式所示那样,也可以是构成n型MISFET的SOI层和构成p型MISFET的SOI层具有相同的晶面,但从晶轴的角度来看电子和空穴流过的方向不同的方式。

该微处理器221包括计算电路(ALU:算术逻辑单元)222、计算电路控制部(ALU控制器)223、指令译码部(Instruction Decoder)224、中断控制部(Interrupt Controller)225、时序控制部(TimingController)226、寄存器(Register)227、寄存器控制部(RegisterController)228、总线接口(总线I/F)229、读出专用存储器(ROM)250、以及ROM接口(ROM I/F)231。

将通过总线接口229输入到微处理器221的指令输入到指令译码部224并且在被译码后,输入到计算电路控制部223、中断控制部225、寄存器控制部228、时序控制部226。计算电路控制部223、中断控制部225、寄存器控制部228、时序控制部226根据被译码的指令进行多种控制。具体地说,计算电路控制部223产生用于控制计算电路222的工作的信号。此外,中断控制部225当微处理器221执行程序时, 根据其优先度或掩模状态来判断并处理来自外部输入/输出装置或外围电路的中断要求。寄存器控制部228产生寄存器227的地址,并且根据微处理器的状态进行寄存器227的读取或写入。

此外,时序控制部226产生用于控制计算电路222、计算电路控制部223、指令译码部224、中断控制部225、寄存器控制部228的工作时序的信号。例如,时序控制部226具备根据参考时钟信号CLK1产生内部时钟信号CLK2的内部时钟产生部,并将该内部时钟信号CLK2提供给上述各种电路。注意,在图16中示出的微处理器221只不过是将该结构简化而示出的一例,实际的微处理器根据其用途具有各种各样的结构。

当使用本发明的半导体元件时,在本实施方式的微处理器中,用于p型MISFET的第一SOI层和用于n型MISFET的第二SOI层都设置在相同的绝缘表面上,并且该两个SOI层的晶面不同。或者,第一SOI层和第二SOI层即使使用相同晶面的结晶且以正方向布置,也可以构成载流子流向不同晶轴方向的结构。这样,通过适用对于流过晶体管的沟道的载流子来说能够提高迁移度的晶面,可以实现微处理器的工作的高速化。

此外,本实施方式的微处理器可以低电压驱动,从而可以实现低耗电化。即,可以降低载流子原子扩散的可能性,因此可以使电子或空穴接受的电阻减少,从而可以提高微处理器的性能。

实施方式13

在本实施方式中,参照图17对作为具有半导体元件的器件的一例的具有通讯电路且可以非接触地进行数据的输入/输出的微处理器的方式进行说明。本实施方式的半导体元件可以使用通过上述实施方式所制造的任何半导体元件。

图17示出根据本实施方式的微型计算机232的框图。该微型计算机232具有天线电路233、模拟电路部234及数字电路部235。模拟电路部234包括:具有共振电容的共振电路236、恒压电路237、整流电路238、解调电路239、调制电路240、复位电路241、振荡电 路242、电源管理电路243。数字电路部235具有RF接口244、控制寄存器245、时钟控制器246、接口247、中央处理单元248、随机存取存储器249、读出专用存储器250。此外,通过将天线电路233所接收的无线信号在整流电路238经过整流而充电给蓄电部251,来获得微型计算机232的工作所需要的电力。蓄电部251由陶瓷电容或双电层电容器等电容器构成。蓄电部251不需要与微型机算机232形成为一体,而是作为另外的部件,安装在具有构成微型计算机232的具有绝缘表面的衬底即可。

这种结构的微型计算机232的工作是如下。天线电路233所接收的信号由共振电路236产生感应电动势。被输入的信号在解调电路239中被解调,且控制指令或数字信号被输出到数字电路部235。复位电路241生成使数字电路部235复位的初始化的信号。例如,生成用作复位信号的晚于电源电压的上升而启动的信号。振荡电路242根据恒压电路237生成的控制信号,改变时钟信号的频率和占空比。由低通滤波器形成的解调电路239使例如振幅偏移键控(ASK:AmplitudeShift Keying)方式的发送信号的振幅变动两值化。调制电路240将发送数据在通过振幅偏移键控方式改变发送信号的振幅之后而发送。调制电路240通过改变共振电路236的共振点改变通讯信号的振幅。时钟控制器246生成用于根据在电源电压或中央处理单元248中消耗的电流而改变时钟信号的频率和占空比的控制信号。电源管理电路243对电源电压进行监视。

从天线电路233输入到微型计算机232的信号在解调电路239中被解调之后,在RF接口中被分解为控制指令和数据等。控制指令存储到控制寄存器245。控制指令包括读出在读出专用存储器250中存储的数据;将数据写入到随机存取存储器249;向中央处理单元248发出的计算指令等。中央处理单元248通过接口247访问读出专用存储器250、随机存取存储器249、控制寄存器245。接口247根据中央处理单元248所要求的地址,具有生成访问读出专用存储器250、随机存取存储器249、控制寄存器245中任一个的访问信号的功能。

中央处理单元248的计算方式可以采用使读出专用存储器250存储OS(operating system:操作系统),并且在启动的同时执行读出程序的方式。此外,也可以采用以专用电路构成计算电路,且通过硬件进行计算的处理方式。在同时使用硬件和软件的方式中,可以适用在专用的计算电路中进行一部分的处理,并且使用程序由中央处理单元248进行其他的计算的方式。

图18示出根据具有如上述结构的本实施方式的微型计算机的外观。绝缘衬地105中设有多个SOI层,因此具有形成n型MISFET及p型MISFET的元件形成层252。元件形成层252形成图17中的模拟电路部234及数字电路部235。天线253设置在绝缘衬底105上。此外,可以设置天线连接端子来代替该天线253。在图18中所示的天线253为磁场型的螺旋天线,但是也可以与电场型的偶极天线等组合。

图19示出图18所示的微型计算机的重要部分,模式地示出其截面结构。在绝缘衬底105上由第一SOI层108及第二SOI层110形成n型MISFET及p型MISFET。第二层间绝缘层217以下的下层结构与上述实时方式同样,因此省略该部分的说明。

在第一布线218上形成有第三层间绝缘层254、第四层间绝缘层255。第三层间绝缘层254由氧化硅膜形成、第四层间绝缘层255由氮化硅膜形成,并且由于双嵌入式,在第三层间绝缘层254中形成的开口部比在第四层间绝缘层255中形成的开口部狭小。在该开口部中形成氮化钽等的金属阻挡层256,并由铜镀法形成铜布线257。再者形成第五层间绝缘层258、第六层间绝缘层259,并只对于第六层间绝缘层形成开口部,在该开口部中形成金属阻挡层260及由铜镀法形成的铜布线261。在铜布线261上形成有第七层间绝缘层262,并形成用于将天线253和铜布线261连接的开口部。然后,将天线253设置在第七层间绝缘层262上,并且使其与铜布线261连接。在图19中,在天线253和铜布线261的界面形成保护层263,在由铜镀法形成天线253时设置该保护层。也可以通过喷墨法或印刷法等直接描绘来形成天线253,还可以通过溅射法堆积铝等导电膜,然后通过光刻 法加工为天线形状,来形成天线253。

这种微型计算机可以通过使用大面积的玻璃衬底作为绝缘衬底105,来提高生产率。如市场上流通的第四世代液晶面板采用730mm×920mm的玻璃衬底,其面积为671600mm2。当从这种玻璃衬底提取微型计算机时,即使不考虑芯片的切割边,当以2mm2来切割时,大约可以获取34万个芯片。玻璃衬底的厚度为0.4mm至0.7mm,当在固定MISFET的SOI层的面以及相反的面贴合保护膜时,可以使器件整体薄到大约0.1mm至0.3mm。

当使用本发明的半导体元件时,在本实施方式的微型计算机中,用于p型MISFET的第一SOI层和用于n型MISFET的第二SOI层都设置在相同的绝缘表面上,并且该两个SOI层的晶面不同。或者,第一SOI层和第二SOI层即使使用相同晶面的结晶且以正方向布置,也可以构成为向不同的晶轴方向流过载流子的结构。这样,通过对于流过晶体管的沟道的载流子适用能够提高迁移度的晶面,可以实现微型计算机的工作的高速化。

此外,本实施方式的微型计算机可以低电压驱动,因此可以实现低耗电化。即,可以降低载流子的原子扩散的可能性,因此可以使电子或空穴接受的电阻减少,从而可以提高微型计算机的性能。

本申请基于2007年3月16日在日本专利局提交的日本专利申请序列号2007-068086以及2007年5月18日在日本专利局提交的日本专利申请序列号2007-133138,在此引用其全部内容作为参考。

Claims (4)

1.一种半导体器件,包括:

设置在绝缘衬底的相同表面上的至少第一单晶半导体层及第二单晶半导体层,

其中,所述第一单晶半导体层具有n型杂质区,所述第二单晶半导体层具有p型杂质区,

并且,所述第一单晶半导体层的晶面为{100},所述第二单晶半导体层的晶面为{110},

并且,所述第一单晶半导体层的沟道长方向为<100>方位,所述第二单晶半导体层的沟道长方向为<110>方位。

2.一种半导体器件,包括:

设置在绝缘衬底的相同表面上的至少第一单晶半导体层及第二单晶半导体层,

其中,所述第一单晶半导体层具有n型杂质区,所述第二单晶半导体层具有p型杂质区,

并且,所述第一单晶半导体层的晶面和所述第二单晶半导体层的晶面为{110},

并且,所述第一单晶半导体层的沟道长方向为<100>方位,所述第二单晶半导体层的沟道长方向为<110>方位。

3.一种半导体显示器件,包括:

设置在绝缘衬底的相同表面上的至少第一单晶半导体层及第二单晶半导体层,

其中,所述第一单晶半导体层具有n型杂质区,所述第二单晶半导体层具有p型杂质区,

并且,所述第一单晶半导体层的晶面为{100},所述第二单晶半导体层的晶面为{110},

并且,所述第一单晶半导体层的沟道长方向为<100>方位,所述第二单晶半导体层的沟道长方向为<110>方位,

并且,所述绝缘衬底具有透光性。

4.一种半导体显示器件,包括:

设置在绝缘衬底的相同表面上的至少第一单晶半导体层及第二单晶半导体层,

其中,所述第一单晶半导体层具有n型杂质区,所述第二单晶半导体层具有p型杂质区,

并且,所述第一单晶半导体层的晶面和所述第二单晶半导体层的晶面为{110},

并且,所述第一单晶半导体层的沟道长方向为<100>方位,所述第二单晶半导体层的沟道长方向为<110>方位,

并且,所述绝缘衬底具有透光性。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007-068086 | 2007-03-16 | ||

| JP2007068086 | 2007-03-16 | ||

| JP2007-133138 | 2007-05-18 | ||

| JP2007133138 | 2007-05-18 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101266982A CN101266982A (zh) | 2008-09-17 |

| CN101266982B true CN101266982B (zh) | 2012-01-11 |

Family

ID=39761809

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200810085387XA Expired - Fee Related CN101266982B (zh) | 2007-03-16 | 2008-03-14 | 半导体器件、半导体显示器件 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7755113B2 (zh) |

| JP (1) | JP5364281B2 (zh) |

| KR (1) | KR101441941B1 (zh) |

| CN (1) | CN101266982B (zh) |

Families Citing this family (31)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1993126B1 (en) * | 2007-05-18 | 2011-09-21 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing methods of semiconductor substrate |

| US8067793B2 (en) | 2007-09-27 | 2011-11-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including storage capacitor with yttrium oxide capacitor dielectric |

| JP5490393B2 (ja) * | 2007-10-10 | 2014-05-14 | 株式会社半導体エネルギー研究所 | 半導体基板の製造方法 |

| US7816232B2 (en) * | 2007-11-27 | 2010-10-19 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor substrate and semiconductor substrate manufacturing apparatus |

| US8093136B2 (en) * | 2007-12-28 | 2012-01-10 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing SOI substrate |

| JP2009231376A (ja) * | 2008-03-19 | 2009-10-08 | Shin Etsu Handotai Co Ltd | Soiウェーハ及び半導体デバイスならびにsoiウェーハの製造方法 |

| EP2105957A3 (en) * | 2008-03-26 | 2011-01-19 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing soi substrate and method for manufacturing semiconductor device |

| JP5654206B2 (ja) * | 2008-03-26 | 2015-01-14 | 株式会社半導体エネルギー研究所 | Soi基板の作製方法及び該soi基板を用いた半導体装置 |

| JP5478166B2 (ja) * | 2008-09-11 | 2014-04-23 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP5478199B2 (ja) * | 2008-11-13 | 2014-04-23 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| SG178179A1 (en) * | 2009-10-09 | 2012-03-29 | Semiconductor Energy Lab | Reprocessing method of semiconductor substrate, manufacturing method of reprocessed semiconductor substrate, and manufacturing method of soi substrate |

| US8630326B2 (en) | 2009-10-13 | 2014-01-14 | Skorpios Technologies, Inc. | Method and system of heterogeneous substrate bonding for photonic integration |

| US9922967B2 (en) | 2010-12-08 | 2018-03-20 | Skorpios Technologies, Inc. | Multilevel template assisted wafer bonding |

| US8735191B2 (en) | 2012-01-04 | 2014-05-27 | Skorpios Technologies, Inc. | Method and system for template assisted wafer bonding using pedestals |

| JP2012156495A (ja) | 2011-01-07 | 2012-08-16 | Semiconductor Energy Lab Co Ltd | Soi基板の作製方法 |

| US9123529B2 (en) | 2011-06-21 | 2015-09-01 | Semiconductor Energy Laboratory Co., Ltd. | Method for reprocessing semiconductor substrate, method for manufacturing reprocessed semiconductor substrate, and method for manufacturing SOI substrate |

| CN102270576A (zh) * | 2011-09-01 | 2011-12-07 | 上海宏力半导体制造有限公司 | Mos晶体管制造方法 |

| CN102437051A (zh) * | 2011-11-24 | 2012-05-02 | 上海华力微电子有限公司 | 硅化物阻止层刻蚀方法、通孔刻蚀停止层形成方法 |

| US8685840B2 (en) * | 2011-12-07 | 2014-04-01 | Institute Of Nuclear Energy Research, Atomic Energy Council | In-situ gettering method for removing metal impurities from the surface and interior of a upgraded metallurgical grade silicon wafer |

| US9324449B2 (en) | 2012-03-28 | 2016-04-26 | Semiconductor Energy Laboratory Co., Ltd. | Driver circuit, signal processing unit having the driver circuit, method for manufacturing the signal processing unit, and display device |

| JP6178118B2 (ja) * | 2013-05-31 | 2017-08-09 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US9196728B2 (en) * | 2013-12-31 | 2015-11-24 | Texas Instruments Incorporated | LDMOS CHC reliability |

| US9209142B1 (en) * | 2014-09-05 | 2015-12-08 | Skorpios Technologies, Inc. | Semiconductor bonding with compliant resin and utilizing hydrogen implantation for transfer-wafer removal |

| JP6449798B2 (ja) * | 2016-01-26 | 2019-01-09 | 太陽誘電株式会社 | 積層セラミック電子部品及びその製造方法、並びにセラミック素体 |

| US9620479B1 (en) * | 2016-06-30 | 2017-04-11 | International Business Machines Corporation | 3D bonded semiconductor structure with an embedded resistor |

| US9941241B2 (en) | 2016-06-30 | 2018-04-10 | International Business Machines Corporation | Method for wafer-wafer bonding |

| US9716088B1 (en) | 2016-06-30 | 2017-07-25 | International Business Machines Corporation | 3D bonded semiconductor structure with an embedded capacitor |

| US10950703B2 (en) | 2017-11-07 | 2021-03-16 | Taiwan Semiconductor Manufacturing Company Ltd. | Semiconductor structure for memory device and method for forming the same |

| CN109637923B (zh) * | 2018-11-14 | 2021-06-11 | 惠科股份有限公司 | 一种显示基板及其制作方法和显示装置 |

| CN109659235B (zh) * | 2018-12-14 | 2021-12-03 | 武汉华星光电半导体显示技术有限公司 | Tft的制备方法、tft、阵列基板及显示装置 |

| JP6953480B2 (ja) * | 2019-07-31 | 2021-10-27 | 株式会社Kokusai Electric | 半導体装置の製造方法、基板処理装置、およびプログラム |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1450649A (zh) * | 2002-03-26 | 2003-10-22 | 夏普公司 | 半导体器件及其制法、soi衬底及其制法和其显示器件 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2681472B1 (fr) | 1991-09-18 | 1993-10-29 | Commissariat Energie Atomique | Procede de fabrication de films minces de materiau semiconducteur. |

| JPH0590117A (ja) * | 1991-09-27 | 1993-04-09 | Toshiba Corp | 単結晶薄膜半導体装置 |

| JP4103968B2 (ja) | 1996-09-18 | 2008-06-18 | 株式会社半導体エネルギー研究所 | 絶縁ゲイト型半導体装置 |

| US6388652B1 (en) | 1997-08-20 | 2002-05-14 | Semiconductor Energy Laboratory Co., Ltd. | Electrooptical device |

| US6686623B2 (en) | 1997-11-18 | 2004-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Nonvolatile memory and electronic apparatus |

| JPH11163363A (ja) | 1997-11-22 | 1999-06-18 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2000012864A (ja) | 1998-06-22 | 2000-01-14 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| US6271101B1 (en) | 1998-07-29 | 2001-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Process for production of SOI substrate and process for production of semiconductor device |

| JP4476390B2 (ja) | 1998-09-04 | 2010-06-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4507395B2 (ja) * | 2000-11-30 | 2010-07-21 | セイコーエプソン株式会社 | 電気光学装置用素子基板の製造方法 |

| JP2003282885A (ja) * | 2002-03-26 | 2003-10-03 | Sharp Corp | 半導体装置およびその製造方法 |

| US6908797B2 (en) | 2002-07-09 | 2005-06-21 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing a semiconductor device |

| US6818529B2 (en) * | 2002-09-12 | 2004-11-16 | Applied Materials, Inc. | Apparatus and method for forming a silicon film across the surface of a glass substrate |

| US7508034B2 (en) | 2002-09-25 | 2009-03-24 | Sharp Kabushiki Kaisha | Single-crystal silicon substrate, SOI substrate, semiconductor device, display device, and manufacturing method of semiconductor device |

| JP2004134675A (ja) | 2002-10-11 | 2004-04-30 | Sharp Corp | Soi基板、表示装置およびsoi基板の製造方法 |

| JP2004119943A (ja) | 2002-09-30 | 2004-04-15 | Renesas Technology Corp | 半導体ウェハおよびその製造方法 |

| JP2006012995A (ja) * | 2004-06-23 | 2006-01-12 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2006229047A (ja) | 2005-02-18 | 2006-08-31 | Renesas Technology Corp | 半導体装置及び半導体装置の製造方法 |

| WO2007046290A1 (en) | 2005-10-18 | 2007-04-26 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US7435639B2 (en) * | 2006-05-31 | 2008-10-14 | Freescale Semiconductor, Inc. | Dual surface SOI by lateral epitaxial overgrowth |

| FR2915318B1 (fr) * | 2007-04-20 | 2009-07-17 | St Microelectronics Crolles 2 | Procede de realisation d'un circuit electronique integre a deux portions de couches actives ayant des orientations cristallines differentes |

-

2008

- 2008-03-12 US US12/073,927 patent/US7755113B2/en not_active Expired - Fee Related

- 2008-03-13 JP JP2008064627A patent/JP5364281B2/ja not_active Expired - Fee Related

- 2008-03-14 CN CN200810085387XA patent/CN101266982B/zh not_active Expired - Fee Related

- 2008-03-14 KR KR1020080023648A patent/KR101441941B1/ko active IP Right Grant

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1450649A (zh) * | 2002-03-26 | 2003-10-22 | 夏普公司 | 半导体器件及其制法、soi衬底及其制法和其显示器件 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009004736A (ja) | 2009-01-08 |

| KR20080084699A (ko) | 2008-09-19 |

| CN101266982A (zh) | 2008-09-17 |

| US20080224274A1 (en) | 2008-09-18 |

| US7755113B2 (en) | 2010-07-13 |

| KR101441941B1 (ko) | 2014-09-18 |

| JP5364281B2 (ja) | 2013-12-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101266982B (zh) | 半导体器件、半导体显示器件 | |

| KR101461206B1 (ko) | 반도체장치 및 그의 제조방법 | |

| US8247307B2 (en) | Manufacturing method of substrate provided with semiconductor films | |

| CN101393859B (zh) | 设置有半导体膜的衬底及其制造方法 | |

| TWI259508B (en) | Semiconductor substrate, semiconductor device, and manufacturing methods for them | |

| CN101308783B (zh) | 半导体衬底、半导体装置、以及其制造方法 | |

| KR101521832B1 (ko) | Soi 기판의 제작 방법 | |

| WO2009042547A1 (en) | Semiconductor device with (110)-oriented silicon | |

| JP5511173B2 (ja) | 半導体装置の作製方法 | |

| KR20100036209A (ko) | 반도체 기판의 제작 방법 | |

| JP5394043B2 (ja) | 半導体基板及びそれを用いた半導体装置、並びにそれらの作製方法 | |

| US8138063B2 (en) | Manufacturing method of a semiconductor device including a single crystal semiconductor film, and a semiconductor film including impurity | |

| US20060272574A1 (en) | Methods for manufacturing integrated circuits | |

| US8039401B2 (en) | Structure and method for forming hybrid substrate | |

| CN1624921A (zh) | 使用硅-硅直接晶片键合、在具有不同晶向的混合衬底上的cmos | |

| US20110006376A1 (en) | Semiconductor device, semiconductor device manufacturing method, and display device | |

| JP2000183351A (ja) | 薄膜半導体装置の製造方法 | |

| JPH09252138A (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20120111 Termination date: 20190314 |

|

| CF01 | Termination of patent right due to non-payment of annual fee |