CN1121016C - 配置逻辑器件阵列的方法和系统 - Google Patents

配置逻辑器件阵列的方法和系统 Download PDFInfo

- Publication number

- CN1121016C CN1121016C CN97199308A CN97199308A CN1121016C CN 1121016 C CN1121016 C CN 1121016C CN 97199308 A CN97199308 A CN 97199308A CN 97199308 A CN97199308 A CN 97199308A CN 1121016 C CN1121016 C CN 1121016C

- Authority

- CN

- China

- Prior art keywords

- logical

- logic

- logical block

- fpga

- design

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/34—Circuit design for reconfigurable circuits, e.g. field programmable gate arrays [FPGA] or programmable logic devices [PLD]

Abstract

一种部分重新配置门阵列的系统和方法,通过逻辑电路的放置和路径(312)产生一个设计数据库(314),访问该数据库以修改由放置和选路所创建的逻辑单元配置(322)。根据修改情况,创建仅包含实现修改逻辑单元的位流的部分配置位流(324)。将部分配置位流下载到门阵列(326),由此执行门阵列的部分重新配置。在另一个实施例中,根据本发明的系统包括软件实用程序(604),它允许应用程序(602)在包含可编程门阵列的系统中执行,在运行过程中对门阵列进行重新配置。实用程序包括根据在运行时间期间检测到的外部条件而修改设计的程序。这种方法避免了需要提供一组预定备用设计,而允许应用程序自身作出决定。

Description

技术领域

本发明总的涉及可编程逻辑器件,更具体地涉及现场可编程门阵列(FPGA)的配置。

背景技术

在集成电路技术的早期,诸如移位寄存器、多路转换器、加法器等的逻辑电路是由数字集成电路构成的。这些小规模集成(SSI)电路通常含有数目较少(例如四至八个)的逻辑门,如“与”门、“或”门、触发电路和锁存器等,需要几十个晶体管。随着技术的发展,能够将越来越多的晶体管装入到IC电路中。目前,半导体制造商能够将数百万个晶体管装在单个晶片上,从而形成高度复杂的芯片,如现代微处理器。

装有这些VLSI(特大规模集成)和ULSI(超大规模集成)芯片的系统同样是复杂的。这种系统通常采用若干个常规逻辑芯片提供各种各样的支撑逻辑功能。已研制出允许制造商快速地实现客户的逻辑设计的门阵列。这些器件是由利用标准方法制造的逻辑门阵列组成的。器件的定制是在最后几步制造步骤中发生的,在这几步中形成与逻辑门连接的金属层以实现所需的逻辑功能。

这些门阵列演变为可编程的器件,给仅需要少量器件或者还未完全开发逻辑设计但是需要少量样品作测试的设计人员提供了更大的灵活性。另一种可编程逻辑器件采用熔断器提供器件中逻辑门之间的互连。熔断器被熔断便断开连接,或者在所谓的抗熔断器的情况中形成连接。因此,这种器件只能使用一次,仅存储一组逻辑功能。

可编程逻辑器件的继续发展已经导致可重新编程的互连关系的发展,更重要的是可配置的逻辑单元的发展。顾名思义,可配置逻辑单元允许设计人员能够对逻辑单元进行编程,使其具有许多基本逻辑门中任何一个门的功能或者更高级的逻辑功能。当前的制造技术使得生产具有数以千计个可配置逻辑单元及其相关互连的高密度器件,即称为现场可编程门阵列(FPGA)成为可能。提供这种高密度器件的能力使得设计人员能够采用越来越复杂的逻辑功能。象以前的产品一样,FPGA包括可编程的互连关系。此外,互连关系是可重复编程的,进一步增大了FPGA的利用价值。

然而,以往对这些可重复编程FPGA的重新配置通常需要对整个器件进行重新配置。Atmel公司(本发明的受让人)制造的FPGA代表了这种器件向前又迈进了一步。将这种器件称为可动态重新配置的FPGA,允许仅对所选的一部分逻辑阵列进行重新配置。用这种方法能够对FPGA作出变化,不必对整个器件进行编程,从而允许仅对所选的一部分阵列进行重新配置。

参考图1,典型的FPGA 100包括多个可配置的逻辑单元130、可配置的I/O块110和可配置的互连关系120、122,共同称之为FPGA资源。尽管互连关系120、122是以各个互连线网格示出的,但是每条“线”实际上是一组互连线,例如,如图3B所示。每个逻辑单元130和I/O块110包括数据线140、142,它们能够有选择地耦合到互连关系120、122上。

典型设计周期从设计一个或多个然后将在FPGA中实现的逻辑电路开始。逻辑设计包括逻辑门和这些逻辑门之间的互连关系。然而,特定的设计,如数字滤波器利用“常数”,即1和0的串来限定其特性。为了描述本发明,把这种常数称为设计的一部分,也可以称为逻辑门。

例如,图2示出一种简单的逻辑设计。逻辑设计中的每个元件用一个实例名来识别。因此,图2中的与门和或门取名为G1-G3。图3A示出逻辑设计是如何在FPGA 100’中出现的。将图2中所示的门G1-G3中的每一个门和互连关系映射到图3A中所示的所选逻辑单元和互连关系上。同样,将输入A-D和输出OUT(图2)映射到所选I/O块。因此,互连关系120a-120c和122a-122c(以较淡的线表示)与逻辑单元G1-G3和I/O块110a-110e连接在一起。图3B示出了图3A配置中一部分放大图。说明不同逻辑单元、互连关系和I/O块之间的具体互连情况。尽管在该图中的设计并未示出常数的使用,但是,众所周知,能够将现代FPGA中逻辑单元构造为输出逻辑“1”或逻辑“0”,能够根据需要如此构造一组逻辑单元,产生一个或多个1和0的串。

现在将说明把图2的设计转换到如图3A中所示的FPGA的步骤。由于绝大多数的目前设计在功能上趋向于相当复杂,通常采用计算机辅助设计(CAD)工具以便于设计过程。因此,在图4中,设计流程图200从输入逻辑电路初始设计,即步骤210开始,例如通过利用CAD工具。

接着是逻辑电路的逻辑门的放置和选路,步骤212。作为放置和选路步骤的结果,产生设计数据库,步骤214。设计数据库规定FPGA中将参与实现逻辑电路的这些逻辑单元、I/O块和互连关系(即资源),包括所选资源的位置及其路经或逻辑结构。图1示出用于识别逻辑单元位置的若干坐标系中的一个。在图1所示的传统坐标系中,逻辑单元按照从左到右和从下到上的次序编号,从左下角单元(0,0)开始,到右上角单元(3,3)结束。通常,设计数据库另外还包括在设计阶段期间给逻辑电路元件指定的实例名,图2。

从包含在设计数据库中的信息,由通常称为位流编译器的工具产生配置位流,步骤216。位流编译器获取存储在设计数据库中的位置和配置信息,产生将配置FPGA中各种资源的限定位流。在物理级上,限定位流代表FPGA中晶体管(开关)的开/关(ON/OFF)状态,它实际上控制每个逻辑单元和I/O块的配置以及逻辑单元与I/O块之间的互连。

在这里,或是可以把配置位流下载到逻辑阵列,由此而配置器件,步骤218a,或是可以把位流保存在磁盘上,步骤218b。图4中用虚线表示这两种可供选择的方案。

即使已经对设计作了调试并按照预期的进行操作,偶然也会发生需要对初始设计进行变化。例如,新的要求可能导致功能定义的变化,这就必须改变初始设计。利用通常的现有技术,对初始设计的最终版本的修改,步骤220导致上述步骤的重复。因此,设计人员利用CAD工具访问初始设计的最终版本并对该设计作出所需改变。执行第二次放置和选路步骤,步骤222,由此产生第二个设计数据库,步骤224。然后,根据新的设计数据库由位流编译器产生第二个配置位流,步骤226。

与第一配置位流一样,可以把也可以不把第二配置位流下载到FPGA。如果需要下载,可提供两种选择:即能够把位流整体下载到FPGA,由此重新配置整个阵列,以包含改进的设计。另一种选择,这里FPGA是可动态重新配置的,意思是指器件能够被部分重新配置,能够仅对第二配置位流中对应于设计变化的这些部分进行下载。通过确定第一与第二配置位流之间的差异产生部分(可重新配置的)位流首先实现之,步骤228。然后,把部分位流下载到可动态重新配置的FPGA,步骤230,由此而实行FPGA的部分重新配置,其中,仅对改进设计中所涉及的这些逻辑单元、互连关系和I/O块进行重新编程。最后,对于另外的设计改进重复循环,就象出现设计功能要求上变化一样。

设计中逻辑门的放置和选路是一项计算强度高的活动。当设计人员由于高密度FPGA的提供能力趋于采用越来越复杂的设计,放置和选路操作会大大增加。在图4所示的现有方法中,考虑到设计循环中的每一次迭代可能需要完全的放置和选路操作,专用于放置和选路计算的时间量会达到惊人的程度。

现有技术方法的另一个方面是可能会出现改进后的设计将导致放置和选路配置不同于以前设计的放置和选路配置。如果以前的设计已经精心地调谐到提供特定临界时序特性,这就成为一个问题。通过全部放置和选路操作进行的下一设计会导致具有不同净长度的逻辑的不同放置,由此对电路的时序产生不利影响。在涉及实时应用的地方,这是一种不可以接受的情况。

需要一种对于完全完成和调试逻辑设计的重新设计在周转时间方面能改善现有技术的方法。还需要一种开发方法,维持现有设计中未涉及设计修改的部分不受影响。

到这里,讨论一直集中围绕逻辑电路的设计是在设计人员的工作实验室的环境中。然而,已观察到,FPGA的现场应用会不适合于单个静态设计。尽管FPGA可以在实际工作条件下在现场重新配置,但是,新的配置通常由存储在诸如EPROM的非易失性装置中的完整设计组成。从EPROM读出配置位流并将其下载到FPGA中。因此,可供使用的配置的尺寸受EPROM的存储容量的限制。在诸如自适应滤波的应用中,迫切需要滤波器的响应能够根据诸如被滤波数据的频率和相位特性,即通常不可预料的条件,在运行时变化。在这种情况中,事前便不能指定新的配置,如滤波器参数。

然而,还需要在运行过程中根据装置正在工作的环境对FPGA进行配置的能力。此外,由于仅需要对FPGA中一部分进行重新配置,如在自适应滤波器的情况中,需要具有运行过程中进行部分重新配置的能力。

发明概要

根据本发明,一种对可动态重新配置FPGA进行配置的方法,从输入初始逻辑设计开始。在该设计上进行放置和选路,导致将位置分配给实现该设计的FPGA中的逻辑单元和互连关系。设计数据库是放置和选路操作的结果。接着,在设计数据库上工作的位流编译器产生配置位流。位流或是可以被下载到FPGA,由此对装置进行配置,或是可以简单地被保存在存储媒介上。

根据相应的设计数据库作出对初始设计最后工作版本的变化。修改后的设计数据库被保存起来,从修改后的设计数据库产生第二配置位流。根据本发明,第二配置位流仅由对应于修改后逻辑设计的这些逻辑单元、I/O块和互连关系的定义位串组成。

通过直接访问设计数据库以执行设计的变化,完全可避免本来需要的耗费在放置和选路计算上的时间。当必须对逻辑设计的最后工作版本作修改时,例如,由于在装入FPGA的系统的功能要求上的变化需要修改时,这是尤其有用的,也是想要的特性。经常的情况是,设计变化自然越来越多,仅涉及到整个设计的一个局部部分。在其它时间,设计人员希望对逻辑设计的最后工作版本的变化做实验。本发明的配置方法可保证用很短的检修时间来实现设计变化,所以,渐增的变化和“What-if”实验是可行的和便利的,不会对项目开发产生不利影响也不产生停止工作时间表。此外,由于放置和选路操作是旁通的,设计中设计人员未作修改的关键部分的任何时序将不受影响并保证提供已知的时序性能。更通俗地说,设计中未作修改的任何部分将继续按预期行使其特性。因此,采用本发明的方法,保证产生的FPGA应用在结构上是正确的,因此功能上是正确的。

在本发明的一个较佳实施例中,通过图形接口把设计数据库提供给用户。接口允许用户指定一部分设计数据库进行显示。设计数据库通过其实例名和在FPGA中的位置确定逻辑单元、I/O块和互连关系。给用户提供逻辑单元,包括被配置为输出常数逻辑值的这些逻辑单元的名称、位置和当前配置。也给出逻辑单元当中的互连关系。

通过从一张以图形方式或者文本方式表示的逻辑门和互连线选项的表或菜单中进行选择可以作出对设计数据库的修改。对于常数的修改可以以文本方式通过输入新的常数值或者以图形方式通过操纵一个或多个能够打开(逻辑“0”)或关闭(逻辑“1”)的开关的图标进行。

在本发明的另一个实施例中,对FPGA进行实时重新配置的系统包括与装置的硬件接口和为了下载新配置数据而访问该装置的软件实用程序。软件实用程序包括产生部分配置位流的手段,允许应用程序根据运行中检测到的操作环境中的特定条件对FPGA进行配置。硬件接口和软件实用程序允许在装置使用中访问FPGA,从而能够对装置中的一部分进行重新配置。

附图简述

图1是典型FPGA的结构。

图2是逻辑电路的一个例子。

图3A和3B示出图2的逻辑电路在图1的FPGA中的实施。

图4是在FPGA设计中通用步骤的要点。

图5是本发明设计方法的一个实施例的要点。

图6是按本发明配置FPGA的系统的方框图。

图7A-7C示出数字滤波器设计。

图8A和8B是本发明的用户接口的屏幕样板。

图9A-9D示出利用基于ROM查找表实现的加法器电路和减法器电路。

图10A-10B示出本发明的用户接口的屏幕样板。

图11示出一个实时FPGA重新配置的系统。

实现本发明的最佳方式

参考图5,按照本发明一个实施例的配置方法300包括创建一种初始设计,步骤310,和执行放置位置和选路径的操作,获得一个第一设计数据库,步骤312和314。然后,位流编译器创建配置位流,步骤316,可以将其下载到FPGA上,配置装置,步骤318a。另一方面,配置位流可以简单存储在存储器装置中,步骤318b。配置位流包括多个定义位流,它指定FPGA中的资源将如何进行配置。

当需要对初始逻辑设计的最终工作版本进行变化时,设计修改可以直接对设计数据库进行。然后,继续图5所示的方法300,向设计人员显示设计数据库中的一部分,步骤320。设计人员选择设计数据库中需要作修改的这些部分和输入变化,步骤322。根据输入的修改情况,产生部分配置位流(也称为重新配置位流),它仅由对应于修改的定义位流构成。然后,可以将这部分位流下载或保存到存储媒体中,步骤326。

图6示出对动态可配置FPGA进行配置的系统,它体现了图5所示的方法。系统400包括数据存储器420和各个模块402-420。采用诸如CAD工具、简图捕获程序等设计输入模块402来创建初始设计420a并存储到磁盘420上。放置和选路模块404获取初始设计420a并创建设计数据库420b,它也存储在磁盘上。位流编译器406产生配置位流420c,下载模块408把配置位流下载到FPGA150。

设计人员通过图形用户接口(GUI)模块410输入对初始逻辑设计最终工作版本的修改。GUI从设计数据库420b进行读出并显示由设计人员所选的设计数据库中的一部分。GUI接收对设计数据库的修改并仅根据输入的修改创建部分位流。GUI装入位流编译器的功能,产生部分位流。然后将部分位流420d存储到磁盘上,接着通过下载模块408下载到FPGA。另一方面,GUI能够把部分位流直接传送到下载模块408。在这里应当注意:如果不需要间接下载到FPGA,那么能够采用另一种存储媒体来存储配置(和重新配置)位流。例如,可以把配置(和重新配置)位流下载到EEPROM等存储媒体上,以供下一步分配。

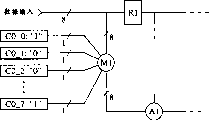

为了说明图6所示的方法,考虑一个自适应数字滤波器,如图7A中所示。滤波器设计500由串联级联的延迟寄存器R1-R7、乘法器M1-M8和加法器A1-A7组成。数据宽带为八位(一字节)。一组滤波器系数C0-C7起乘法运算的被乘数的作用。由于数据中的每个字节通过寄存器移位和传播,所有乘法器形成系数与数据之间的乘积项。然后由加法器A1-A7对乘积项求和。

回想一下逻辑设计,如滤波器设计500中的每个元件具有一个由设计人员开始指定的实例名。因此,参考图7A,寄存器取名为R1-R7,乘法器取名为M1-M8,加法器取名为A1-A7。还给系数C0-C7指定了实例名。具体说,包含系数的每一个位具有一个名称。从图7C中所示的系数C0的扩展图中更加清楚地示出了这一情况。系数是一个八位量,这里,将位取名为C0_0至C0_7。再回到图7A,应当明白,也可以给元件R1-R7、M1-M8和A1-A7当中的互连关系取名。然而,为了避免图面的杂乱,已经省略了这些互连关系的实例名。

滤波器设计500的放置和选路导致设计数据库,由实例名、每个寄存器和算术算符以及被选作实现这些功能的逻辑单元的位置和配置指定。以同样的方式,设计数据库列出位的实例名,包括系数C0-C7、它们的相应逻辑单元的位置和逻辑单元是否被配置为产生逻辑“0”或逻辑“1”。通过FPGA中的坐标系,如图1中所示的坐标系识别出现在设计数据库中的逻辑单元。

图7B示出图7A的数字滤波器的改进设计500’,这里已经指定了一组不同的系数C’0-C’7。希望根据本发明的方法作这种修改的设计人员开始访问基于初始设计500创建的第一设计数据库。这最好是利用图形用户接口(GUI)实现,当然基于文本的接口也一样是有效的,也许使用更困难和更低效些。

在一个实施例中,GUI有一种模式,用于对逻辑设计中所定义的逻辑常数进行编辑。例如,图8A的屏幕样板显示了设计500中的每个常数C0-C7。在“实例名”列下是包括每个系数C0-C7位的名称。每个位由一个配置为输出常数逻辑电平的逻辑单元实现。回想一下,每个逻辑单元具有一个相应的实例名。在单元被范围识别的地方,如在图8A的情况中,显示范围中第一和最后单元的实例名。在“位置”列下是在相应逻辑单元的FPGA中的位置。为了说明起见假设,被使用的坐标编号惯例遵循图1中所示的惯例。因此,根据图8A,包括系数C0的逻辑单元位于FPGA中第10行的第7-14列中;系数C1的逻辑单元位于第12行的第7-14列中,依此类推。“现行配置”列显示由逻辑单元产生的当前逻辑值。例如,包括系数C0的第7、8、9、10、11、12、13和14列中八个逻辑单元显示,为当前配置相应的输出逻辑值“1”、“0”、“1”、“0”、“1”、“0”、“1”和“1”。“新配置”列由输入字段组成,允许用户输入新的逻辑值,作为一位串。这位串位中的每个位与这位串所表示的常数单元具有一一对应关系。

由于设计数据库包含产生图8A所示显示屏所需的所有信息,GUI通过设计数据库进行简单搜索,找出已经被配置为产生常数逻辑电平的这些逻辑单元,访问它们的实例名、单元位置和当前配置信息。访问设计数据库和产生如图8A中所示显示信息的具体软件实施细节将随任何给定设计数据库格式所使用的精确数据结构而变化。在计算机程序员的范围和能力之内,这些实施细节是专业人员所公知的。

图8A中所示的逻辑常数最好按照水平相邻性分组。在一个给定的常数逻辑单元块中,可以将逻辑单元分组为水平单元组或垂直单元组。例如,在图8A中,可以看出,单元位置(7,18)至(14,21)限定32个逻辑单元的块。这些单元被显示为四个由八个水平相邻单元组成的组。因此,四个水平组是:(7,18)至(14,18);(7,19)至(14,19);(7,20)至(14,20)和(7,21)至(14,21)。

另一方面,块(7,18)至(14,21)中的单元最好能够按照垂直相邻性分组。在图8B的屏幕样板中示出这一情况。在这种情况下,有八个由四个单元组成的垂直组,每一个为:(7,18)至(7,21);(8,18)至(8,21);(9,18)至(9,21);(10,18)至(10,21);(11,18)至(11,21);(12,18)至(12,21);(13,18)至(13,21)和(14,18)至(14,21)。于是将这些单元的其它字段修改反映其垂直分组。

根据较佳实施例,将相邻常数单元的组表示为单元的范围。由于构成系数C0-C3的单元仅呈现水平相邻性它们显示成水平组。同样,对仅显示垂直相邻性的单元进行垂直分组。能够对常数单元进行垂直或水平分组的地方,按照用户指定的优先选择进行分组。因此,根据设计人员的优先选择,能够对系数C4-C7进行水平或垂直分组,如图8A和8B所示。在图中所示的例子中,优先选择可以针对水平相邻性,如图gA所示。然而,在另一种设计中,可以按垂直方式排列系数,在这种情况中,可以作出图8B所示的垂直优选。

在本发明的另一个实施例中,可以将非相邻的常数单元分组在一起。GUI允许用户选择常数单元中的任意组合并将所选单元作为一个组处理。尽管这些单元是非相邻的,但是,GUI可显示作为一个组的单元,并允许用户对作为一个组的单元的逻辑值进行修改。因此,以一一对应关系把由用户输入的代表新逻辑值的一位值串映射到组中的常数单元,与以上结合图8A和8B所说明的情况差不多。

输入新系数值C0’-C7’后,GUI按照图5中的步骤324产生部分配置位流。由于GUI既拥有单元位置(从设计数据库获得)又拥有它们的新配置(从设计人员获得),GUI能够产生配置位流,该配置位流将实现设计人员指定的设计变化。

部分配置位流仅仅基于设计人员输入的变化,并包括仅针对FPGS中参与设计变化的这些单元的配置信息。不需要对整个设计进行放置和选路操作,导出配置位流的变化,正如采用现有技术方法的情况那样,见图4。相反地,GUI从用户输入直接进入到部分配置位流。这种方法显著地缩短了实施设计变化所需的时间,从而允许设计人员快速实现和测试设计方案的替换。

较佳实施例的GUI进一步包括一种对配置成逻辑门的逻辑单元进行修改的模式。例如,考虑图9A中所示的基于ROM的查找表,它由ROM阵列和解码器组成。查找表通常是用于执行诸如全加器和全减器的逻辑功能的功能发生器,图9B示出其真值表。图9C和9D分别示出加法器和减法器的实现,这里,图9A中解码器的八个输出(0-7)在图9C和9D中示为A0-A7。可以看出,在四个地方加法器电路不同于减法器电路:加法器中“与”门G8、12在减法器中被“或”门G7、G11所替代;加法器中“或”门G24、G28在减法器中被“与”门G23、G27所替代。

利用本发明的方法,设计人员通过简单地对感兴趣的四个门进行定位或识别以及变化它们的相应逻辑单元的配置能够方便地从一种电路切换到另一种电路。参考图10A和10B,GUI能够在窗口中显示放置在FPGA中的逻辑设计。通过滚动窗口,能够把阵列中的任何一部分带入到视窗中。另一方面,GUI通过把适当的信息输入到图10A中所示的单元位置字段或实例名字段中,能够定位部分阵列。

对于以下的讨论假设:初始逻辑设计装入图9C中的加法器电路,需要转换到图9D中的减法器电路。GUI访问在加法器电路的初始设计上进行放置和选路操作而产生的设计数据库,并根据FPGA的元件显示设计布局。显示可以由构成FPGA的逻辑单元的图标或其它图形表示组成。另一方面,GUI可以显示代表由每个逻辑单元所提供逻辑功能的图标。另一种选择是提供FPGA组成的文本表示,然而这一方法在传送和引导有关FPGA信息方面不如图形方法有效。

设计人员或是通过滚动或是通过指定门的实例名而显示待改变的部分加法器电路。图10A的屏幕样板上显示了以一部分加法器电路,即门G6、G8、G10和G12为中心的一部分设计数据库。可以看出,“或”门G6已经指定为56行、100列中的逻辑单元,“与”门G8已经指定为56行、101列中的逻辑单元,依此类推。为了把门G8从“与”门变为“或”门,设计人员首先选择该门,例如通过将鼠标器光标置于该门的图标上并接下鼠标器按钮。图10B示出被突出的门G8,表示该门已经被选定。单击鼠标器另一按钮(或揿键)产生一弹出菜单,显示一张可能的逻辑门表。从菜单中选择“或”条目,引起所选门G8被配置为“或”门。以同样的方式改变门G12。接着,设计人员通过滚动窗口将门G24和G28带入视屏。然后,以如上所述的方式对门G24和G28进行修改。

当修改完成时,揿一下OK按钮。正如图5所示的方法中描述的,GUI仅根据修改产生部分配置位流。产生的位流仅由把初始设计的四个单元(加法器电路中的G8、G12、G24和G28)重新定义为减法器的门G7、G11、G23和G27的特性所需的位串构成。因此,通过直接访问初始全加器设计的设计数据库和在其上作出变化,设计人员能够避免执行完全放置和选路操作步骤而耗费的时间。

最后要说明一点,可以观察到,以上讨论的特定门的选择和菜单方法不是实施本发明的关键所在。基于图形的其它输入/选择方法也是同样有效的。

通常相对于查找表,如图9B中所示的查找表,由查找表实施的逻辑功能完全由表的输出所限定,因此,图9B中列SUM和Cout完全限定全加器功能,列SUB和Bout完全限定全减器功能。GUI无需显示执行特定查找表的特定逻辑单元,而是能够仅列出表输出和允许用户输入对表输出的变化。然后,GUI指定所需逻辑单元完成新的查找表。以这种方式在更高的抽象水平上代表查找表,以一种更有意义的方法将该表提供给用户,从而对用户隐去意义不大的实施细节,因此,具有更大的适用性。

从图9C和9D可以看出,由2个输入“与”门和2个输入“或”门的级联串联连接能够实现查找表。例如,全加器的SUM输出由门G2、G6、G10、G14、G18、G22、G26和G30来实现,而Cout输出则由门G4、G8、G12、G16、G20、G24、G28和G32来实现。因此,GUI简单地通过改变实现查找表的适当门,能够方便地重新配置一个限定第一功能查找表来执行第二功能。

现在,讨论将针对本发明的另一实施例,它允许设计人员对可动态重新配置的FPGA进行实时重新配置,即在重新配置时可以运行的系统中的阵列。参考图11,典型系统600包括CPU或微处理器610、FPGA 620、EPROM622或其它一些非易失性RAM器件、以及诸如磁盘存储器的数据存储器630。在CPU610上运行的系统软件包括配置FPGA的专用应用软件602和FPGA实用程序604。在系统引导时,已经编程并在EPROM622中的配置位流载入到FPGA。另一种选择是,能够用存储在数据存储器630中的配置位流初始配置FPGA。

在系统600操作期间,软件能够检测有关其操作环境的特定条件。例如,相对于图8A和8B中所示的数字滤波器设计,软件602可以确定需要作调节的滤波器截止频率。相应地,可以对以前积累的数据进行分析,根据分析结果计算新的系数。然后,调用特定的FPGA实用程序604来创建包含定义新系数的位流的部分配置位流。接着,应用软件602调用其它FPGA实用程序把部分配置位流下载到FPGA,由此实现该滤波器设计中的变化。

实时作出的设计变化的范围不受FPGA实用程序604的限制,但是受装载到FPGA的特定设计的复杂性程度的限制。在运行过程中的变化可以由应用软件限制,限于仅改变逻辑常数或者限于各逻辑门。然而,这种限制是应用所特有的,由计算机电源、存储器、操作环境等的提供能力确定,并不是由于本发明造成的限制。

FPGA实用程序604的一组应用编程接口(API)包括:

ConstantCell

Function:

Generate a configuration bitstream which configures each

logic cell in the specified range to produce either a

logic one or a logic zero.

Parameters:

xStart-X coordinate of the first logic cell

yStart-Y coordinate of the first logic cell

xEnd-X coordinate of the last logic cell

yEnd-Y coordinate of the last logic cell

value_string-the corresponding string of l′s and o′s

buf-pointer to a memory store for storing the

configuration bitstring

Return:

the number of bytes in the bitstream

DownLoad

Function:

Download a configuration bitstring to the FPGA.

Parameters:

buf-pointer to the configuration bitstring to be downloaded

Return:

n/a

GateCell

Function:

Generate a configuration bitstream which reconfigures a

previously defined logic gate to implement a different logic

function.Only the logic function of the gate is changed.

Other aspects of the gate remain the same,such as the number

of input and output terminals.

Parameters,

x_coord-X coordinate location of the logic cell

y_coord-Y coordinate location of the logic cell

logic-the specific logic function:AND,NAND,OR,NOR,XOR,

INVERTER,etc.

buf-pointer to a memory store for storing the configuration

bitstring

Return:

the number of bits in the bitstream

<!-- SIPO <DP n="12"> -->

<dp n="d12"/>

ReadCell

Function:

Return the current configuration for the specified logic cell.

Parameters:

x_coord-x coordinate location of the logic cell

y_coord-Y coordinate location of the logic cell

buf-pointer to a memory store for storing the cell

configuration

Return:

n/a

以下的C语言代码片段说明如何在典型应用中使用这些实用程序。给出的例子针对图8A的数字滤波器,说明如何根据外部操作环境来调节系数C0-C7。

:

:

/w ... a determination has been made that the filter

needs adjustment ... */

:

:

/* read the current values of filter coefficients Co-C7*/

for(i=0;i<8;++i) /* each coefficient */

for(j=0,j<8;++j)/* each bit */

ReadCell(xloc_coeff[i][j],yloc_coeff[i][j],

current_buf[i]+j);

/*derive new coefficient values and store in new_buf */

:

:

/* create configuration bitstreams for the new values */

z=0;/* point to beginning of bstream */

for(i=0;i<8;++i)

{

zl=ConstantCell(xloc_coeff[i][0],yloc_coeff[i][0],

xloc_coeff[i][7],yloc_coeff[i][7],new_buf[i],

bstream + z);

z+=zl;/* point to end of bstream */

}

/*download bitstream to FPGA */

DownLoad(bstream);

根据本发明的对FPGA重新配置的系统允许FPGA的重新配置实时进行和允许仅对FPGA中的一部分进行重新配置。此外,本发明允许应用软件根据外部操作环境确定设计中部分的变化。这种方法的优点在于:设计人员不需要事前确定所有可能的备用设计及其相应的配置位流。而是,应用软件能够确定设计变化,在运行过程中创建部分配置位流,根据它们所出现的环境中的条件而实施这些变化。

Claims (16)

1.一种配置可编程逻辑单元阵列的方法,其特征在于:所述阵列包括多个可编程互连关系,每个所述逻辑单元在所述阵列中具有一个唯一单元位置,所述阵列具有一种相关的逻辑设计,所述方法包括:

访问一个设计数据库,该数据库代表逻辑单元定义和对应于所述逻辑设计的逻辑单元互连关系的一种配置;

把所述设计数据库的一部分提供给用户;

输入用户指定的变化,对所述设计数据库的用户所选部分进行重新定义;

产生一部分配置位流,仅描述与所述设计数据库的所述重新定义部分相关的所述逻辑单元和所述的互连关系;以及

将所述部分配置位流下载到所述逻辑单元阵列中,由此仅配置所述逻辑单元阵列中对应于所述用户指定变化的这些部分。

2.如权利要求1所述的方法,其特征在于:所述的提供步骤包括识别被配置为逻辑门的特定逻辑单元以及对于每一个所述特定逻辑单元显示其单元位置和显示其相应逻辑门的图形图象或文本表示。

3.如权利要求2所述的方法,其特征在于:所述的输入用户指定变化的步骤包括识别有待重新配置的逻辑单元、显示备用逻辑门的表以及从所述表中选择一个备用逻辑门,对所述被识别逻辑单元进行重新配置。

4.如权利要求3所述的方法,其特征在于:所述的显示备用逻辑门表的步骤包括显示所述备用逻辑门的图形表示。

5.如权利要求2所述的方法,其特征在于:所述的提供步骤进一步包括:

识别所述设计数据库中的固定值逻辑单元;

对于不与其它任何固定值逻辑单元邻接的固定值逻辑单元,显示所述固定值逻辑单元的单元位置和当前值;以及

对于一组相邻的固定值逻辑单元,将所述这组的单元位置显示为单元位置的范围以及将所述组中的逻辑单元的当前值显示为位流。

6.如权利要求1所述的方法,其特征在于:所述的提供步骤包括仅显示被限定输出常数逻辑“1”或常数逻辑“0”的这些逻辑单元。

7.如权利要求1所述的方法,其特征在于:所述的提供步骤包括:

识别所述设计数据库中的固定值逻辑单元;

对于不与其它任何固定值逻辑单元邻接的固定值逻辑单元,显示所述固定值逻辑单元的单元位置和当前值;以及

对于一组相邻的固定值逻辑单元,将所述这组的单元位置显示为单元位置的范围以及将所述组中的每个逻辑单元的当前值集中地显示为位流。

8.一种在FPGA中产生所述FPGA的配置位流的方法,所述FPGA包括可编程逻辑单元和I/O块以及设置在所述逻辑单元与所述I/O块之间的可编程互连关系,所述方法包括:输入一逻辑电路,所述逻辑电路包括多个逻辑门和所述逻辑门之间的连接;选择逻辑单元和互连关系来实现所述逻辑电路;形成一个包含所述所选逻辑单元和互连关系的放置和选路信息的设计数据库;根据所述放置和选路信息产生第一配置位流,所述第一配置位流包括所有的所述所选逻辑单元和互连关系的定义,由此而实现所述逻辑电路;把所述第一配置位流存储到数据存储器中,接着下载到所述FPGA中;以及将变化加入到所述逻辑电路设计中;所述方法的改进包括:

识别所述设计数据库中的第一类逻辑单元,它们被配置为逻辑门;

对于所述第一类逻辑单元中的每一个,显示其单元位置和其相应逻辑门的表示;

识别所述设计数据库中的第二类逻辑单元,它们被配置为产生常数逻辑值;

显示所述第二类逻辑单元的单元位置和逻辑值;

输入对所述设计数据库所选部分的修改;

产生第二配置位流,包括仅针对所述逻辑单元和所述互连关系中与所述设计数据库的所述所选部分的所述修改相关的这些的新定义。

9.如权利要求8所述的方法,其特征在于:在对所述第一配置位流进行下载的所述步骤后进一步包括把第二位流下载到所述FPGA中的步骤。

10.如权利要求8所述的方法,其特征在于:所述的显示所述第二类逻辑单元包括形成包含所述第二类逻辑单元中相互相邻这些逻辑单元的单元组,以及利用单元位置的范围显示每一个所述单元组中逻辑单元的单元位置。

11.如权利要求10所述的方法,其特征在于:所述的形成单元组的子步骤包括形成所述第二类逻辑单元中这一些与其它所述第二类逻辑单元水平相邻的水平组,所述第二类逻辑单元中这一些与其它所述第二类逻辑单元垂直相邻的垂直组,如果给定的逻辑单元既属于水平组又属于垂直组,那么,把所述的给定逻辑单元分配给所述的水平组。

12.如权利要求10所述的方法,其特征在于:所述的形成单元组的子步骤包括形成所述第二类逻辑单元中这一些与其它所述第二类逻辑单元水平相邻的水平组,所述第二类逻辑单元中这一些与其它所述第二类逻辑单元垂直相邻的垂直组,如果给定的逻辑单元既属于水平组又属于垂直组,那么,把所述的给定逻辑单元分配给所述的垂直组。

13.如权利要求8所述的方法,其特征在于:所述的显示所述第二类逻辑单元包括形成包含所述第二类逻辑单元中用户指定逻辑单元的单元组,以及显示每一个所述单元组中逻辑单元的单元位置和逻辑值。

14.一种配置FPGA的系统,所述FPGA具有至少一个编程逻辑设计,所述系统包括:

在所述FPGA的运行时间操作期间检测所述FPGA外部条件的装置;

响应于所述FPGA外部条件的检测结果重新设计一部分所述逻辑设计的装置;

仅基于所述重新设计的部分形成部分配置位流的装置;

将所述部分配置位流发送到所述FPGA,由此在运行时间中对所述FPGA进行部分重新配置以实现所述逻辑设计的所述重新设计部分的装置。

15.如权利要求14所述的系统,其特征在于进一步包括至少存储设计数据库中代表所述逻辑设计的一部分的装置,所述的重新设计的装置包括访问所述设计数据库,由此提供对所述逻辑设计进行重新设计基础的装置。

16.一种配置FPGA的系统,所述FPGA具有至少一个编程逻辑常数,所述系统包括:

在所述FPGA的运行时间操作期间检测所述FPGA外部条件的装置;

响应于所述FPGA外部条件的检测结果确定所述逻辑常数的一个新值装置;

仅基于所述重新设计的部分形成部分配置位流的装置;

将所述部分配置位流发送到所述FPGA,由此在运行时间中对所述FPGA进行部分重新配置的装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US08/739,606 US5946219A (en) | 1996-10-30 | 1996-10-30 | Method and system for configuring an array of logic devices |

| US08/739,606 | 1996-10-30 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1241275A CN1241275A (zh) | 2000-01-12 |

| CN1121016C true CN1121016C (zh) | 2003-09-10 |

Family

ID=24973056

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN97199308A Expired - Fee Related CN1121016C (zh) | 1996-10-30 | 1997-10-15 | 配置逻辑器件阵列的方法和系统 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US5946219A (zh) |

| EP (1) | EP0958542A4 (zh) |

| JP (1) | JP2001504958A (zh) |

| KR (1) | KR100446338B1 (zh) |

| CN (1) | CN1121016C (zh) |

| HK (1) | HK1022753A1 (zh) |

| TW (1) | TW359801B (zh) |

| WO (1) | WO1998019256A1 (zh) |

Families Citing this family (79)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6317860B1 (en) * | 1996-10-28 | 2001-11-13 | Altera Corporation | Electronic design automation tool for display of design profile |

| US6134707A (en) * | 1996-11-14 | 2000-10-17 | Altera Corporation | Apparatus and method for in-system programming of integrated circuits containing programmable elements |

| US6078736A (en) * | 1997-08-28 | 2000-06-20 | Xilinx, Inc. | Method of designing FPGAs for dynamically reconfigurable computing |

| US6430732B1 (en) | 1998-03-27 | 2002-08-06 | Xilinx, Inc. | Method for structured layout in a hardware description language |

| US6260182B1 (en) | 1998-03-27 | 2001-07-10 | Xilinx, Inc. | Method for specifying routing in a logic module by direct module communication |

| US6292925B1 (en) | 1998-03-27 | 2001-09-18 | Xilinx, Inc. | Context-sensitive self implementing modules |

| US6237129B1 (en) | 1998-03-27 | 2001-05-22 | Xilinx, Inc. | Method for constraining circuit element positions in structured layouts |

| US6216258B1 (en) | 1998-03-27 | 2001-04-10 | Xilinx, Inc. | FPGA modules parameterized by expressions |

| US6243851B1 (en) | 1998-03-27 | 2001-06-05 | Xilinx, Inc. | Heterogeneous method for determining module placement in FPGAs |

| US6178541B1 (en) * | 1998-03-30 | 2001-01-23 | Lsi Logic Corporation | PLD/ASIC hybrid integrated circuit |

| DE19843640A1 (de) * | 1998-09-23 | 2000-03-30 | Siemens Ag | Verfahren zum Konfigurieren eines konfigurierbaren Hardware-Blocks |

| US6658564B1 (en) * | 1998-11-20 | 2003-12-02 | Altera Corporation | Reconfigurable programmable logic device computer system |

| TW476069B (en) * | 1998-11-20 | 2002-02-11 | Via Tech Inc | Placement and routing for array device |

| US6430736B1 (en) | 1999-02-26 | 2002-08-06 | Xilinx, Inc. | Method and apparatus for evolving configuration bitstreams |

| US6363517B1 (en) | 1999-02-26 | 2002-03-26 | Xilinx, Inc. | Method and apparatus for remotely evolving configuration bitstreams |

| US6378122B1 (en) | 1999-02-26 | 2002-04-23 | Xilinx, Inc. | Method and apparatus for evolving a plurality of versions of a configuration bitstream in parallel |

| US6363519B1 (en) | 1999-02-26 | 2002-03-26 | Xilinx, Inc. | Method and apparatus for testing evolvable configuration bitstreams |

| US6539532B1 (en) | 1999-02-26 | 2003-03-25 | Xilinx, Inc. | Method and apparatus for relocating elements in an evolvable configuration bitstream |

| WO2000068775A1 (en) | 1999-05-07 | 2000-11-16 | Morphics Technology Inc. | Apparatus and method for programmable datapath arithmetic arrays |

| EP1177631B1 (en) | 1999-05-07 | 2005-12-28 | Infineon Technologies AG | Heterogeneous programmable gate array |

| DE60021375T2 (de) | 1999-05-07 | 2006-05-24 | Infineon Technologies Ag | Vorrichtung und verfahren zur dynamischen definition von teilfeldern innerhalb eines programmierbaren gatterfeldes |

| US6438737B1 (en) | 2000-02-15 | 2002-08-20 | Intel Corporation | Reconfigurable logic for a computer |

| US6453456B1 (en) * | 2000-03-22 | 2002-09-17 | Xilinx, Inc. | System and method for interactive implementation and testing of logic cores on a programmable logic device |

| US6725441B1 (en) | 2000-03-22 | 2004-04-20 | Xilinx, Inc. | Method and apparatus for defining and modifying connections between logic cores implemented on programmable logic devices |

| US6542844B1 (en) | 2000-08-02 | 2003-04-01 | International Business Machines Corporation | Method and apparatus for tracing hardware states using dynamically reconfigurable test circuits |

| US6530071B1 (en) * | 2000-09-28 | 2003-03-04 | Xilinx, Inc. | Method and apparatus for tolerating defects in a programmable logic device using runtime parameterizable cores |

| US6904436B1 (en) * | 2000-10-04 | 2005-06-07 | Cypress Semiconductor Corporation | Method and system for generating a bit order data structure of configuration bits from a schematic hierarchy |

| US6625794B1 (en) * | 2000-11-06 | 2003-09-23 | Xilinx, Inc. | Method and system for safe device reconfiguration |

| US6836842B1 (en) * | 2001-04-24 | 2004-12-28 | Xilinx, Inc. | Method of partial reconfiguration of a PLD in which only updated portions of configuration data are selected for reconfiguring the PLD |

| US6912706B1 (en) | 2001-08-15 | 2005-06-28 | Xilinx, Inc. | Instruction processor and programmable logic device cooperative computing arrangement and method |

| CN1307586C (zh) * | 2001-10-16 | 2007-03-28 | 捷豹逻辑股份有限公司 | 高效逻辑打包的现场可编程门阵列核心单元 |

| US7406674B1 (en) | 2001-10-24 | 2008-07-29 | Cypress Semiconductor Corporation | Method and apparatus for generating microcontroller configuration information |

| US7206919B2 (en) * | 2001-12-14 | 2007-04-17 | Stmicroelectronics Pvt. Ltd. | Rapid partial configuration of reconfigurable devices |

| AU2003268373A1 (en) * | 2002-09-04 | 2004-03-29 | Mentor Graphics (Holdings) Ltd. | Polymorphic computational system and method |

| KR200304200Y1 (ko) * | 2002-09-16 | 2003-02-19 | 신창업 | 마이크 보호용 커버 |

| US7194615B2 (en) * | 2002-09-17 | 2007-03-20 | Nokia Corporation | Reconfigurable apparatus being configurable to operate in a logarithmic scale |

| US7124392B2 (en) | 2002-09-27 | 2006-10-17 | Stmicroelectronics, Pvt. Ltd. | Mapping of programmable logic devices |

| US7111110B1 (en) * | 2002-12-10 | 2006-09-19 | Altera Corporation | Versatile RAM for programmable logic device |

| CN1304994C (zh) * | 2003-08-27 | 2007-03-14 | 四川南山之桥微电子有限公司 | 可运行的2层/3层交换机和路由器芯片及制定方法 |

| JP3966873B2 (ja) * | 2003-10-08 | 2007-08-29 | 株式会社東芝 | 論理回路装置、動作電圧変更方法 |

| US7669035B2 (en) * | 2004-01-21 | 2010-02-23 | The Charles Stark Draper Laboratory, Inc. | Systems and methods for reconfigurable computing |

| JP4095576B2 (ja) * | 2004-05-17 | 2008-06-04 | 株式会社東芝 | プログラマブル論理回路を用いる汎用論理回路装置 |

| US7343578B1 (en) * | 2004-08-12 | 2008-03-11 | Xilinx, Inc. | Method and system for generating a bitstream view of a design |

| US7406673B1 (en) | 2004-08-12 | 2008-07-29 | Xilinx, Inc. | Method and system for identifying essential configuration bits |

| US7519823B1 (en) | 2004-08-12 | 2009-04-14 | Xilinx, Inc. | Concealed, non-intrusive watermarks for configuration bitstreams |

| US20060200603A1 (en) * | 2005-03-01 | 2006-09-07 | Naoto Kaneko | Dynamic resource allocation for a reconfigurable IC |

| US7861190B1 (en) * | 2005-03-17 | 2010-12-28 | Altera Corporation | Power-driven timing analysis and placement for programmable logic |

| US7275232B2 (en) * | 2005-04-01 | 2007-09-25 | Altera Corporation | Methods for producing equivalent field-programmable gate arrays and structured application specific integrated circuits |

| US7784005B1 (en) * | 2005-06-14 | 2010-08-24 | Xilinx, Inc. | Electronic circuit design viewer |

| US7571395B1 (en) * | 2005-08-03 | 2009-08-04 | Xilinx, Inc. | Generation of a circuit design from a command language specification of blocks in matrix form |

| US7739092B1 (en) * | 2006-01-31 | 2010-06-15 | Xilinx, Inc. | Fast hardware co-simulation reset using partial bitstreams |

| US7827023B2 (en) * | 2006-02-01 | 2010-11-02 | Cadence Design Systems, Inc. | Method and apparatus for increasing the efficiency of an emulation engine |

| US7631223B1 (en) * | 2006-06-06 | 2009-12-08 | Lattice Semiconductor Corporation | Programmable logic device methods and system for providing multi-boot configuration data support |

| US7640527B1 (en) * | 2006-06-29 | 2009-12-29 | Xilinx, Inc. | Method and apparatus for partial reconfiguration circuit design for a programmable device |

| US7634743B1 (en) * | 2006-07-21 | 2009-12-15 | Cadence Design Systems, Inc. | Method for updating a placed and routed netlist |

| US7521961B1 (en) * | 2007-01-23 | 2009-04-21 | Xilinx, Inc. | Method and system for partially reconfigurable switch |

| US7873934B1 (en) * | 2007-11-23 | 2011-01-18 | Altera Corporation | Method and apparatus for implementing carry chains on field programmable gate array devices |

| JP2010114772A (ja) * | 2008-11-07 | 2010-05-20 | Nec Electronics Corp | 半導体装置、差分プログラム実施方法 |

| US8214592B2 (en) * | 2009-04-15 | 2012-07-03 | International Business Machines Corporation | Dynamic runtime modification of array layout for offset |

| US8276105B2 (en) * | 2009-09-18 | 2012-09-25 | International Business Machines Corporation | Automatic positioning of gate array circuits in an integrated circuit design |

| US8368423B2 (en) * | 2009-12-23 | 2013-02-05 | L-3 Communications Integrated Systems, L.P. | Heterogeneous computer architecture based on partial reconfiguration |

| US8397054B2 (en) * | 2009-12-23 | 2013-03-12 | L-3 Communications Integrated Systems L.P. | Multi-phased computational reconfiguration |

| US7982504B1 (en) * | 2010-01-29 | 2011-07-19 | Hewlett Packard Development Company, L.P. | Interconnection architecture for multilayer circuits |

| US8595670B1 (en) * | 2010-03-08 | 2013-11-26 | Altera Corporation | Method and apparatus for circuit block reconfiguration EDA |

| US8364946B2 (en) | 2010-03-22 | 2013-01-29 | Ishebabi Harold | Reconfigurable computing system and method of developing application for deployment on the same |

| US9116751B2 (en) | 2011-02-08 | 2015-08-25 | Canon Kabushiki Kaisha | Reconfigurable device, processing assignment method, processing arrangement method, information processing apparatus, and control method therefor |

| US8751998B2 (en) * | 2011-07-01 | 2014-06-10 | Altera Corporation | Method and system for partial reconfiguration simulation |

| TWI459216B (zh) * | 2011-09-09 | 2014-11-01 | Iner Aec Executive Yuan | 數位安全系統硬體化之方法 |

| EP2894572B1 (en) | 2014-01-09 | 2018-08-29 | Université de Rennes 1 | Method and device for programming a FPGA |

| CN104850669A (zh) * | 2014-02-14 | 2015-08-19 | 国网河南省电力公司鹤壁供电公司 | 逻辑器件及构建方法、逻辑器件库、逻辑器构建方法 |

| US9929734B2 (en) * | 2015-09-08 | 2018-03-27 | Dspace Digital Signal Processing And Control Engineering Gmbh | Method for changing the configuration of a programmable logic module |

| US9619610B1 (en) * | 2015-10-01 | 2017-04-11 | Altera Corporation | Control block size reduction through IP migration in an integrated circuit device |

| CN108182303B (zh) * | 2017-12-13 | 2020-08-28 | 京微齐力(北京)科技有限公司 | 基于混合功能存储单元的可编程器件结构 |

| KR102559581B1 (ko) | 2018-05-23 | 2023-07-25 | 삼성전자주식회사 | 재구성 가능 로직을 포함하는 스토리지 장치 및 상기 스토리지 장치의 동작 방법 |

| US10838389B2 (en) | 2018-12-13 | 2020-11-17 | Hamilton Sunstrand Corporation | Reconfigurable control architecture for programmable logic devices |

| US11556382B1 (en) | 2019-07-10 | 2023-01-17 | Meta Platforms, Inc. | Hardware accelerated compute kernels for heterogeneous compute environments |

| US11042414B1 (en) | 2019-07-10 | 2021-06-22 | Facebook, Inc. | Hardware accelerated compute kernels |

| US11042413B1 (en) * | 2019-07-10 | 2021-06-22 | Facebook, Inc. | Dynamic allocation of FPGA resources |

| CN111274199A (zh) * | 2020-01-23 | 2020-06-12 | 中国科学院微电子研究所 | 差异上注定向修改的fpga在轨重构实现方法 |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4845633A (en) * | 1985-12-02 | 1989-07-04 | Apple Computer Inc. | System for programming graphically a programmable, asynchronous logic cell and array |

| US5089973A (en) * | 1986-11-07 | 1992-02-18 | Apple Computer Inc. | Programmable logic cell and array |

| US4745084A (en) * | 1986-11-12 | 1988-05-17 | Vlsi Technology, Inc. | Method of making a customized semiconductor integrated device |

| JP2877303B2 (ja) * | 1987-03-31 | 1999-03-31 | 株式会社東芝 | 集積回路の自動設計装置 |

| US4970664A (en) * | 1988-06-10 | 1990-11-13 | Kaiser Richard R | Critical path analyzer with path context window |

| DE68925121T2 (de) * | 1988-10-05 | 1996-06-13 | Quickturn Systems Inc | Verfahren zur verwendung einer elektronisch wiederkonfigurierbaren gatterfeld-logik und dadurch hergestelltes gerät |

| US5208768A (en) * | 1988-11-14 | 1993-05-04 | Digital Equipment Corporation | Expert system including arrangement for acquiring redesign knowledge |

| US4967367A (en) * | 1988-11-21 | 1990-10-30 | Vlsi Technology, Inc. | Synthetic netlist system and method |

| US5448493A (en) * | 1989-12-20 | 1995-09-05 | Xilinx, Inc. | Structure and method for manually controlling automatic configuration in an integrated circuit logic block array |

| US5278769A (en) * | 1991-04-12 | 1994-01-11 | Lsi Logic Corporation | Automatic logic model generation from schematic data base |

| US5544067A (en) * | 1990-04-06 | 1996-08-06 | Lsi Logic Corporation | Method and system for creating, deriving and validating structural description of electronic system from higher level, behavior-oriented description, including interactive schematic design and simulation |

| US5623418A (en) * | 1990-04-06 | 1997-04-22 | Lsi Logic Corporation | System and method for creating and validating structural description of electronic system |

| US5555201A (en) * | 1990-04-06 | 1996-09-10 | Lsi Logic Corporation | Method and system for creating and validating low level description of electronic design from higher level, behavior-oriented description, including interactive system for hierarchical display of control and dataflow information |

| US5349691A (en) * | 1990-07-03 | 1994-09-20 | Xilinx, Inc. | Programming process for 3-level programming logic devices |

| US5499192A (en) * | 1991-10-30 | 1996-03-12 | Xilinx, Inc. | Method for generating logic modules from a high level block diagram |

| US5491640A (en) * | 1992-05-01 | 1996-02-13 | Vlsi Technology, Inc. | Method and apparatus for synthesizing datapaths for integrated circuit design and fabrication |

| SG49816A1 (en) * | 1992-07-02 | 1998-06-15 | Rafael C Camarota | Non-disruptive randomly addressable memory system |

| GB9223226D0 (en) * | 1992-11-05 | 1992-12-16 | Algotronix Ltd | Improved configurable cellular array (cal ii) |

| US5361373A (en) * | 1992-12-11 | 1994-11-01 | Gilson Kent L | Integrated circuit computing device comprising a dynamically configurable gate array having a microprocessor and reconfigurable instruction execution means and method therefor |

| CA2126265A1 (en) * | 1993-09-27 | 1995-03-28 | Michael Robert Cantone | System for synthesizing field programmable gate array implementations from high level circuit descriptions |

| US5394031A (en) * | 1993-12-08 | 1995-02-28 | At&T Corp. | Apparatus and method to improve programming speed of field programmable gate arrays |

| US5781756A (en) * | 1994-04-01 | 1998-07-14 | Xilinx, Inc. | Programmable logic device with partially configurable memory cells and a method for configuration |

| US5673198A (en) * | 1996-03-29 | 1997-09-30 | Xilinx, Inc. | Concurrent electronic circuit design and implementation |

-

1996

- 1996-10-30 US US08/739,606 patent/US5946219A/en not_active Expired - Lifetime

-

1997

- 1997-10-15 JP JP52050198A patent/JP2001504958A/ja not_active Ceased

- 1997-10-15 KR KR10-1999-7003512A patent/KR100446338B1/ko not_active IP Right Cessation

- 1997-10-15 WO PCT/US1997/018363 patent/WO1998019256A1/en not_active Application Discontinuation

- 1997-10-15 CN CN97199308A patent/CN1121016C/zh not_active Expired - Fee Related

- 1997-10-15 EP EP97910893A patent/EP0958542A4/en not_active Withdrawn

- 1997-10-23 TW TW086115676A patent/TW359801B/zh not_active IP Right Cessation

-

2000

- 2000-03-14 HK HK00101555A patent/HK1022753A1/xx not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| KR100446338B1 (ko) | 2004-09-01 |

| HK1022753A1 (en) | 2000-08-18 |

| US5946219A (en) | 1999-08-31 |

| WO1998019256A1 (en) | 1998-05-07 |

| JP2001504958A (ja) | 2001-04-10 |

| CN1241275A (zh) | 2000-01-12 |

| TW359801B (en) | 1999-06-01 |

| EP0958542A4 (en) | 2000-05-17 |

| KR20000052714A (ko) | 2000-08-25 |

| EP0958542A1 (en) | 1999-11-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1121016C (zh) | 配置逻辑器件阵列的方法和系统 | |

| Trimberger | Three ages of fpgas: a retrospective on the first thirty years of fpga technology: this paper reflects on how moore's law has driven the design of fpgas through three epochs: the age of invention, the age of expansion, and the age of accumulation | |

| US7073158B2 (en) | Automated system for designing and developing field programmable gate arrays | |

| US6530071B1 (en) | Method and apparatus for tolerating defects in a programmable logic device using runtime parameterizable cores | |

| EP0834823A1 (en) | Method and apparatus for efficiently implementing complex function blocks in integrated circuit designs | |

| US7679398B2 (en) | Reprogrammable instruction DSP | |

| US20060085779A1 (en) | Representing device layout using tree structure | |

| US7062744B2 (en) | Emulation solution for programmable instruction DSP | |

| Gokhale et al. | High level compilation for fine grained fpgas | |

| Adário et al. | Dynamically reconfigurable architecture for image processor applications | |

| Wilton | Heterogeneous technology mapping for area reduction in FPGAs with embedded memory arrays | |

| US7509246B1 (en) | System level simulation models for hardware modules | |

| Yang et al. | An ILP based hierarchical global routing approach for VLSI ASIC design | |

| Bazargan et al. | Integrating scheduling and physical design into a coherent compilation cycle for reconfigurable computing architectures | |

| US7117467B2 (en) | Methods for optimizing package and silicon co-design of integrated circuit | |

| US8032852B1 (en) | Method of automating clock signal provisioning within an integrated circuit | |

| Rau et al. | Embedded computing: New directions in architecture and automation | |

| Banerjee et al. | Fast FPGA placement using space-filling curve | |

| US7509618B1 (en) | Method and apparatus for facilitating an adaptive electronic design automation tool | |

| Mehta et al. | A low-energy reconfigurable fabric for the supercisc architecture | |

| Herath et al. | Ant colony optimization based module footprint selection and placement for lowering power in large FPGA designs | |

| Jha et al. | High-level library mapping for arithmetic components | |

| Koch | Regular datapaths on field-programmable gate arrays | |

| Mujumdar et al. | BINET: An algorithm for solving the binding problem | |

| Zhang et al. | NanoMap: An integrated design optimization flow for a hybrid nanotube/CMOS dynamically reconfigurable architecture |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C56 | Change in the name or address of the patentee | ||

| CP03 | Change of name, title or address |

Address after: American California Patentee after: Atmel Corp. Address before: American California Patentee before: Atmel Corporation |

|

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20030910 Termination date: 20131015 |