CN1267996C - 半导体器件及其制造方法 - Google Patents

半导体器件及其制造方法 Download PDFInfo

- Publication number

- CN1267996C CN1267996C CNB018083439A CN01808343A CN1267996C CN 1267996 C CN1267996 C CN 1267996C CN B018083439 A CNB018083439 A CN B018083439A CN 01808343 A CN01808343 A CN 01808343A CN 1267996 C CN1267996 C CN 1267996C

- Authority

- CN

- China

- Prior art keywords

- mentioned

- storage card

- semiconductor device

- mounting portion

- basal substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K19/00—Record carriers for use with machines and with at least a part designed to carry digital markings

- G06K19/06—Record carriers for use with machines and with at least a part designed to carry digital markings characterised by the kind of the digital marking, e.g. shape, nature, code

- G06K19/067—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components

- G06K19/07—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components with integrated circuit chips

- G06K19/077—Constructional details, e.g. mounting of circuits in the carrier

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K19/00—Record carriers for use with machines and with at least a part designed to carry digital markings

- G06K19/06—Record carriers for use with machines and with at least a part designed to carry digital markings characterised by the kind of the digital marking, e.g. shape, nature, code

- G06K19/067—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components

- G06K19/07—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components with integrated circuit chips

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K19/00—Record carriers for use with machines and with at least a part designed to carry digital markings

- G06K19/06—Record carriers for use with machines and with at least a part designed to carry digital markings characterised by the kind of the digital marking, e.g. shape, nature, code

- G06K19/067—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components

- G06K19/07—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components with integrated circuit chips

- G06K19/077—Constructional details, e.g. mounting of circuits in the carrier

- G06K19/0772—Physical layout of the record carrier

- G06K19/07732—Physical layout of the record carrier the record carrier having a housing or construction similar to well-known portable memory devices, such as SD cards, USB or memory sticks

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K19/00—Record carriers for use with machines and with at least a part designed to carry digital markings

- G06K19/06—Record carriers for use with machines and with at least a part designed to carry digital markings characterised by the kind of the digital marking, e.g. shape, nature, code

- G06K19/067—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components

- G06K19/07—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components with integrated circuit chips

- G06K19/077—Constructional details, e.g. mounting of circuits in the carrier

- G06K19/07737—Constructional details, e.g. mounting of circuits in the carrier the record carrier consisting of two or more mechanically separable parts

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K19/00—Record carriers for use with machines and with at least a part designed to carry digital markings

- G06K19/06—Record carriers for use with machines and with at least a part designed to carry digital markings characterised by the kind of the digital marking, e.g. shape, nature, code

- G06K19/067—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components

- G06K19/07—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components with integrated circuit chips

- G06K19/077—Constructional details, e.g. mounting of circuits in the carrier

- G06K19/07737—Constructional details, e.g. mounting of circuits in the carrier the record carrier consisting of two or more mechanically separable parts

- G06K19/07739—Constructional details, e.g. mounting of circuits in the carrier the record carrier consisting of two or more mechanically separable parts comprising a first part capable of functioning as a record carrier on its own and a second part being only functional as a form factor changing part, e.g. SIM cards type ID 0001, removably attached to a regular smart card form factor

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K19/00—Record carriers for use with machines and with at least a part designed to carry digital markings

- G06K19/06—Record carriers for use with machines and with at least a part designed to carry digital markings characterised by the kind of the digital marking, e.g. shape, nature, code

- G06K19/067—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components

- G06K19/07—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components with integrated circuit chips

- G06K19/077—Constructional details, e.g. mounting of circuits in the carrier

- G06K19/07743—External electrical contacts

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/02—Disposition of storage elements, e.g. in the form of a matrix array

- G11C5/04—Supports for storage elements, e.g. memory modules; Mounting or fixing of storage elements on such supports

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5388—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates for flat cards, e.g. credit cards

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/18—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different subgroups of the same main group of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K5/00—Casings, cabinets or drawers for electric apparatus

- H05K5/02—Details

- H05K5/0256—Details of interchangeable modules or receptacles therefor, e.g. cartridge mechanisms

- H05K5/026—Details of interchangeable modules or receptacles therefor, e.g. cartridge mechanisms having standardized interfaces

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K5/00—Casings, cabinets or drawers for electric apparatus

- H05K5/02—Details

- H05K5/0256—Details of interchangeable modules or receptacles therefor, e.g. cartridge mechanisms

- H05K5/0282—Adapters for connecting cards having a first standard in receptacles having a second standard

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05554—Shape in top view being square

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/8538—Bonding interfaces outside the semiconductor or solid-state body

- H01L2224/85399—Material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L24/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01039—Yttrium [Y]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/1015—Shape

- H01L2924/1016—Shape being a cuboid

- H01L2924/10161—Shape being a cuboid with a rectangular active surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Abstract

一种半导体器件,在将装载有半导体芯片的基板的器件装载面覆盖起来的壳体的一部分上,设置可以与用于加大上述壳体平面尺寸的辅助器具的凹部进行配合的截面凸状的安装部分,其中上述截面凸状的安装部分的状态,在上述壳体的表面一侧和背面一侧是非对称的。另一方面,上述壳体的表面一侧的上述截面凸状的安装部分的宽度,比位于上述壳体的表面相反一侧的上述截面凸状的安装部分的宽度更宽。另一方面,在被上述截面凸状的安装部分挟持起来的部分中设置沟部,以便钩住上述辅助器具的爪部,在装卸自由的状态下把上述辅助器具固定到上述壳体上。另一方面,在上述半导体芯片中形成有存储器电路。

Description

技术领域

本发明涉及半导体器件及其制造技术,例如,涉及在半导体存储卡(以下,简称为存储卡)中应用且有效的技术。

背景技术

多媒体卡(美国Sun Disk公司)或SD卡(松下、东芝、Sun Disk)等之类的存储卡,是在其内部的半导体存储器芯片内存储信息的存储装置之一。若用该存储卡,由于对于在半导体存储器芯片上形成的非易失性存储器直接地而且电学地进行存取,故与别的存储装置比较,写入、读出的时间要快一个没有机械系统控制的量,而且存储媒体的交换是可能的。此外,由于形状比较小型且重量轻,故主要地作为便携式个人计算机、移动电话或数字照相机等之类要求可搬运性的设备的辅助存储装置使用。近些年来这些设备的小型化不断前进,与之相伴随地要求存储卡进一步的小型化。此外,存储卡是一种新技术,其尺寸上的规格尚未完全统一。

发明内容

然而,在要减小存储卡的大小或者大小因国家而不同的情况下,如何才能使得既保持与已有的存储卡之间尺寸上的互换性,又可以对已有的存储卡应对设备使用,就成了一个重要的课题。

本发明的目的在于提供可以提高半导体器件通用性的技术。

本发明的上述以及其它的目的和新颖的特征,会从本说明书的讲述和附图弄得明白起来。

在本申请中公开的发明之内,简单地说,代表性的发明概要如下。

就是说,本发明是这样的发明:采用使用来变换内置半导体芯片的树脂制壳体的平面尺寸的金属制辅助器具的凹部进行配合的办法,将可以在装卸自由的状态下把上述辅助器具安装到上述壳体上的截面凸状的安装部分,设置在上述壳体上。其中上述截面凸状的安装部分的状态,在上述壳体的表面一侧和背面一侧是非对称的。另一方面,上述壳体的表面一侧的上述截面凸状的安装部分的宽度,比位于上述壳体的表面相反一侧的上述截面凸状的安装部分的宽度更宽。另一方面,在被上述截面凸状的安装部分挟持起来的部分中设置沟部,以便钩住上述辅助器具的爪部,在装卸自由的状态下把上述辅助器具固定到上述壳体上。另一方面,在上述半导体芯片中形成有存储器电路。

此外,本发明是这样的发明:具有使得把已装载上半导体芯片的基板的器件装载面罩起来那样地罩上的树脂制的壳体的平面面积的一半或一半以下的面积的基板。

本发明是这样的发明:具有使用下模的腔体深度比上模的腔体深度更大的模铸模具,成型用来把已装载上半导体芯片的基板的器件装载面罩起来的壳体的工序。

此外,本发明是这样:具有壳体,在上述壳体的一个面上形成的沟,在朝向器件装载面的状态下安装到上述沟内的基板,已装载到上述器件装载面上的多个半导体芯片,在上述沟和上述基板中沿着上述壳体的长边方向的长度形成得比上述壳体的长边方向的全长短,在上述基板或上述沟中,位于壳体中央一侧的拐角部分进行了倒角。

由本发明的一个实施形态得到的效果,简单地说来如下。

就是说,采用在内置半导体芯片的壳体的一部分内,设置可以配合用来加大上述壳体的平面尺寸的金属制的辅助器具的凹部的截面凸状的安装部分的办法,可以提高半导体器件的通用性。

此外,在基板和安装基板的壳体的沟内,对位于壳体中央一侧的拐角部分进行倒角的办法,可以提高半导体器件的弯曲强度。

本发明,可以应用于半导体器件及其制造方法。

附图说明

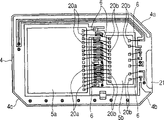

图1是作为本发明的一个实施形态的半导体器件和辅助器具的斜视图。

图2(a)的斜视图示出了图1的半导体器件的表面一侧的外观,(b)的斜视图示出了该半导体器件的背面一侧的外观。

图3(a)是图1的半导体器件的表面一侧的平面图,(b)是(a)的半导体器件的侧视图,(c)是(a)的半导体器件的背面图,(d)是(a)的半导体器件的背面一侧的平面图。

图4(a)是图1的半导体器件长边方向的辅助器具安装部分的主要部分扩大平面图,(b)是半导体器件短边方向的辅助器具安装部分的主要部分扩大平面图。

图5(a)是图3(a)A-A线的剖面图,(b)是(a)的主要部分的扩大剖面图。

图6是图1的半导体器件的基底基板的平面图。

图7(a)是图1的辅助基部的表面一侧的平面图,(b)是(a)的辅助器具的侧视图,(c)是(a)的辅助器具的背面图,(d)是(a)的辅助器具的背面一侧的平面图,(e)是(a)的辅助器具的爪部和支持部分的主要部分扩大剖面图。

图8(a)是图1的半导体器件和辅助器具的表面的平面图,(b)是(a)的侧视图,(c)是(a)的背面的平面图。

图9(a)是已有的全尺寸的半导体器件的表面的平面图,(b)是(a)的侧视图,(c)是(a)的背面的平面图。

图10(a)是图8的状态的半导体器件的辅助器具爪安装部分、与辅助器具的爪部之间的接合部分的主要部分扩大剖面图,(b)是图8的状态的半导体器件的辅助器具安装部分与辅助器具的凹部之间的接合部分的主要部分扩大剖面图。

图11是用来成型图1的半导体器件的一个构件的模具的剖面图。

图12(a)到(c)是图11的主要部分扩大剖面图。

图13(a)是半导体器件的全体平面图,(b)是把(a)的半导体器件的基板组装到全尺寸的半导体器件内使用的情况下的全体平面图。

图14是本发明的另一个实施形态的半导体器件和辅助器具的斜视图。

图15(a)、(b)的斜视图示出了图14的半导体器件的表面一侧和背面一侧的外观。

图16(a)是图14的半导体器件的表面一侧的平面图,(b)是(a)的半导体器件的侧视图,(c)是(a)的半导体器件的背面图,(d)是(a)的半导体器件的背面一侧的平面图。

图17(a)是图14的半导体器件和辅助器具的表面的平面图,(b)是(a)的侧视图,(c)是(a)的背面的平面图。

图18是本发明的再一个实施形态的半导体器件的背面一侧的平面图。

图19是本发明者所研究的半导体器件的基底基板的表面的平面图。

图20是图19的基底基板的背面的平面图。

图21是本发明者所研究的全尺寸的半导体器件用的器件帽的表面的平面图。

图22是图21的器件帽的背面的平面图。

图23是把图19和图20所示的基底基板安装到图21和图22的器件帽的沟内后的全尺寸的半导体器件的背面的平面图。

图24是本发明的一个实施形态中的构成半导体器件的基底基板的表面的平面图。

图25是图24的基底基板的背面的平面图。

图26是装载图24和图25所示的基底基板的全尺寸的半导体器件用的器件帽的表面的平面图。

图27是图26的器件帽的背面的平面图。

图28是把图24和图25所示的基底基板安装到图26和图27的器件帽内后的全尺寸的半导体器件的背面的平面图。

图29的图28的A1-A1线的剖面图。

图30是图23所示的半导体器件的弯曲强度试验的结果的说明图。

图31是图23所示的半导体器件的弯曲强度试验的结果的说明图。

图32是图23所示的半导体器件的弯曲强度试验的结果的说明图。

图33是作为本发明的一个实施形态的半导体器件的弯曲强度试验的结果的说明图。

图34是作为本发明的一个实施形态的半导体器件的弯曲强度试验的结果的说明图。

图35是作为本发明的一个实施形态的半导体器件的弯曲强度试验的结果的说明图。

图36是作为本发明的一个实施形态的半导体器件的器件帽的背面的平面图。

图37是作为本发明的一个实施形态的半导体器件的主要部分扩大剖面图。

图38是成型图26到图29等所示的半导体器件的器件帽的模具的一个例子的剖面图。

图39的基底基板的表面的平面图示出了作为本发明的一个实施形态的半导体器件的芯片的配置例。

图40的基底基板的表面的平面图示出了作为本发明的一个实施形态的半导体器件的芯片的配置例。

图41是作为本发明的一个实施形态的半导体器件的组装工序的流程图。

图42是图41的半导体器件的组装工序中的基底基板的表面的平面图。

图43是接在图42后边的半导体器件的组装工序中的基底基板的表面的平面图。

图44是接在图43后边的半导体器件的组装工序中的基底基板的表面的平面图。

图45是接在图44后边的半导体器件的组装工序地中的基底基板的表面的平面图。

图46是接在图45后边的半导体器件的组装工序中的基底基板的表面的平面图。

图47是作为本发明的另一个实施形态的全尺寸的半导体器件的背面的平面图。

图48是图47的区域Z1的扩大平面图。

图49是作为本发明的另一个实施形态的全尺寸的半导体器件的背面的平面图。

图50是图49的区域Z2的扩大平面图。

图51是作为本发明的另一个实施形态的全尺寸的半导体器件的背面的平面图。

图52是作为本发明的另一个实施形态的半尺寸的半导体器件的表面的平面图。

图53是图52的半导体器件的背面的平面图。

图54是作为本发明的另一个实施形态的半尺寸的半导体器件的表面的平面图。

图55是作为本发明的再一个实施形态的半尺寸的半导体器件的背面的平面图。

图56是作为本发明的另一个实施形态的全尺寸的半导体器件的剖面图。

图57是图56的主要部分扩大剖面图。

具体实施方式

在以下的实施形态中,为了便于说明,在需要时要分割成多个部分或实施形态进行说明,但是,除去特别说明的情况下之外,它们之间的关系是一方为另一方的一部分或全部的变形例、详细、补充说明等的关系,而不是彼此没有关系。

此外,在以下的实施形态中,在说到要素的数(包括个数、数值、量、范围等)的情况下,除去特别明示的情况和从原理上说显然要限定于特定数的情况外,也可以是特定数以上或以下而并不限定于该特定数。

还有,在以下的实施形态中,其构成要素(也包括要素步骤等),除去特别明示的情况和从原理上说被认为显然是必须的情况等之外,不言而喻并不是必须不可。

同样,在以下的实施形态中,在谈及构成要素的形状、位置关系等时,除去特别明示的情况和从原理上说被认为显然并非如此的情况等之外,规定还包括实质上与该形状等近似或类似的关系等。这种情况对于上述数值和范围也是同样的。

此外,在用来说明本实施形态的所有的图中具有同一功能的部分都赋予同一标号,其重复的说明予以省略。

此外,在本发明的实施形态中,即便是平面图,为了便于观看,有时候也加上了阴影线。

以下,根据附图详细地说明本发明的实施形态。

(实施形态1)

图1是作为本发明的一个实施形态的半导体器件和辅助器具的斜视图,图2(a)、(b)的斜视图示出了图1的半导体器件的表面一侧和背面一侧的外观,图3(a)是图1的半导体器件的表面一侧的平面图,图3(b)是(a)的半导体器件的侧视图,图3(c)是(a)的半导体器件的背面图,图3(d)是(a)的半导体器件的背面一侧的平面图,图4(a)是图1的半导体器件长边方向的辅助器具安装部分的主要部分扩大平面图,图4(b)是半导体器件短边方向的辅助器具安装部分的主要部分扩大平面图,图5(a)是图3(a)的半导体器件的短方向(A-A线)的剖面图,图5(b)是图5(a)的主要部分的扩大剖面图,图6示出了该半导体器件的基底基板的平面图。

本实施形态的半导体器件,例如是可作为信息设备或通信设备等之类的电子装置的辅助存储装置使用的存储卡1。该存储卡1,例如由平面矩形形状的小的薄板构成,其外形尺寸,例如长边为24mm左右,短边为18mm左右,厚度为1.4mm左右。如果是照原样不变的外形尺寸,则虽然在例如移动电话或数字照相机等之类的小型的电子装置中使用,但是借助于安装上金属制的适配器(辅助器具)2,就变成为也可以在便携式个人计算机等之类的相对大型的电子装置中使用的构造。例外,把原封不动地可以在上述大型电子装置中使用的存储卡叫做全尺寸的存储卡,把可以在上述小型电子装置中使用的本实施形态的存储卡1叫做半尺寸的存储卡。

形成该存储卡1的外形的器件帽(壳体)3,例如,从谋求轻重量化、加工容易性和柔软性的观点考虑,由ABS树脂或PPE(Poly PhenyleneEther,聚苯醚)等那样的具有绝缘性的树脂构成,在基底基板4中,使得把已装配上半导体芯片(以下,简称为芯片)5a、5a、5b的器件装载面覆盖起来那样地罩了起来,在器件帽3中,在存储卡1的背面一侧的两个拐角部分的2个地方处形成截面凸状的适配器安装部分3a。该适配器安装部分3a,是配合适配器2的凹部2a的部位,采用把器件帽3的表面、侧面和背面形成得比器件帽3中的适配器安装部分3a以外的部分的表面、侧面和背面,恰好凹下适配器2的板厚的量的部分形成。就是说,适配器安装部分3a被形成为使得其厚度比存储卡1的厚度稍薄一些。

在本实施形态中,采用把在存储卡1的器件帽3上形成的适配器安装部分3a作成为截面凸状的办法,与把适配器安装部分3a作成为凹状的情况下比较,可以把适配器安装部分3a的机械强度提高到2倍或2倍以上。

在把适配器安装部分3a作成为截面凸状的情况下,在存储卡1的厚度方向上必须设置2个凸部。但是,由于对于存储卡1的厚度来说存在着一个上限,故不大可能确保其每个凸部的厚度。由于器件帽3从谋求轻重量化、加工容易性和柔软性等的观点考虑由树脂构成,故如果构成适配器安装部分的凹部的各自的凸部的厚度形成得太薄,则不能确保机械强度。另一方面,如果凹部的各自的凸部都形成得太厚,凹部自身的形成就会变得困难起来。对此,在象本实施形态那样把适配器安装部分3a作成为截面凸状的情况下,在存储卡1的厚度方向上设置一个适配器安装部分3即可。就是说,可以把在凹部中形成适配器安装部分3的情况下的各自的凸部集中到一个地方,形成相对厚的凸部。在这里,可以把截面凸状的适配器安装部分3a的厚度的一半(d1/2)形成为厚达与凹坑厚度d2同等。就是说,可以作成为Max(d1/2)=d2(参看图3(a)到(c)和图4(a))。因此,由于可以把适配器安装部分3a形成得比较厚,故即便是用树脂制的器件帽3的一部分构成的适配器安装部分3a也可以确保机械强度。此外,适配器安装部分3a由于是截面凸状的,故形成也是容易的。此外,如果考虑用与器件帽3同一树脂形成适配器安装部分3a的情况,则可以确保d1=d2的同等程度强度,可以使d1薄到d1=d/3。

此外,在本实施形态中,采用在存储卡1的背面一侧的两个拐角部分的2个地方设置适配器安装部分3a的办法,由于把适配器2牢固地配合到存储卡1的背面一侧的长边方向两个端部上,故可以提高在把适配器2安装到存储卡1上时的稳定性。

此外,在本实施形态中,在器件帽3中,被上述两个拐角部分的适配器安装部分3a、3a挟持起来的地方,就是说,在存储卡1的背面一侧的长边方向的中央,被形成为与存储卡1的厚度大体上相等,变成为比适配器安装部分3a更厚。借助于此,与沿着存储卡1的长边方向使存储卡1的背面一侧全都变薄的情况比较,可以提高器件帽3和适配器2之间的接合部位的机械强度。

此外,在本实施形态中,采用把适配器安装部分3a作成为截面凸状的办法,就可以充分地确保既是适配器安装部分3a的长度(存储卡1的短边方向的长度)L1,就是说,使适配器2的凹部2a配合到适配器安装部分3a内的方向的长度,又是该凹部2a与适配器安装部分3a平面性地进行重叠的长度。在已把适配器安装部分3a作成为截面凸状的情况下,如上所述,如果考虑确保该凹部的每个凸部的强度,则不可能把上述长度L1形成得太长。对此,在本实施形态的情况下,由于可以确保适配器安装部分3a的厚度,可以确保适配器安装部分3a的机械强度,故可以把上述长度L1形成得某种程度地长。在这里,长度㈠变得比适配器安装部分2a的厚度d1更长。如上所述,得益于把适配器安装部分3的长度L1形成得长的办法,由于可以用适配器2的凹部2a牢固地抓住存储卡1的适配器安装部分3a,故可以确保存储卡1与适配器2之间的结合部分处的刚性。因此,可以减少或防止起因于弯曲等而使存储卡1与适配器2之间的结合部分断掉这样的事故。

此外,在本实施形态中,在存储卡1的表面和背面处适配器安装部分3a的状态变成为非对称。具体地说,适配器安装部分3a的宽度(存储卡1的长边方向的长度)W1、W2变成为非对称,其各自的宽度W1、W2的尺寸不同(参看图3)。这是因为要使适配器2的安装方向不要弄错的缘故。就是说,由于适配器安装部分3a的宽度W1、W2的尺寸不一样,如果把适配器2的安装方向弄错则结果就变成为不能安装适配器2。借助于此,就可以防止起因于适配器2的安装错误而对存储卡1造成损伤或破坏的现象。此外,由于不必特别注意适配器2的安装方向的对错,故在可以放心地安装存储卡1的同时,还可以对卡安装设备稳定地进行操作。

此外,在本实施形态中,在存储卡1的背面的背面一侧附近,在存储卡1的长边方向的中央,形成适配器爪安装部分3b。该适配器爪安装部分3b是把适配器2的爪部2b紧紧钩住的地方,具有凹坑部分3b1和沟部3b2。凹坑部分3b1采用从存储卡1的背面跨过沟部3b2使器件帽3的背面恰好凹进适配器2的板厚的量的办法形成。此外,借助于使适配器2的爪部2b进入该沟部3b2内的办法,结果就变成为把存储卡1和适配器2牢固地结合固定起来。

此外,在存储卡1的表面的背面一侧附近,在存储卡的长边方向的中央,形成卡取出沟3c。该卡取出沟3c,是在从上述电子装置取出存储卡1时,对取出进行辅助的沟。就是说,在使手指触碰到该卡取出沟3c上的状态下,采用与器件帽2的表面平行地提拉手指的办法,就可以从上述电子装置中抽出存储卡1。上述存储卡1的背面的沟部2b2的深度d2,被形成为使得比存储卡1的表面的卡取出沟2c的深度d3更深(参看图5(b))。

另外,存储卡1的前面一侧的角,是出于易于识别存储卡1的安装方向等的观点而被切掉的。此外,在存储卡1的器件帽3的表面上,在存储卡1的前面附近一侧,形成有表示在把存储卡1安装到上述电子装置中去时的插入方向的平面三角形状的标记3d。

装配在上述存储卡1的基底基板4上边的2块芯片5a、5a,具有同一外形尺寸,形成同一容量的闪速存储器(EEPROM)。这些芯片5a、5a,在一方的上部重叠上另一方的状态下装配到基底基板4上边。下层的芯片5a,用粘接剂等接合到基底基板的上表面上,上层的芯片5a则用粘接剂接合到下层的芯片5a的上表面上。另一方面,控制器用的芯片5b装配到存储器用的芯片5a的附近的基底基板4上边,同样用粘接剂等接合到基底基板4的上表面上。这3块芯片5a、5a、5b,不论哪一个都在使其主面(器件形成面)朝上的状态下装配到基底基板4上。

在已形成了闪速存储器(EEPROM)的2块芯片5a、5a的各自的主面上,沿着其一边一列地形成有多个键合焊盘。就是说,存储器用的芯片5a,采用在器件形成面的周边部分上形成键合焊盘,而且沿着这些键合焊盘的一边一列地进行配置的单边焊盘方式。另一方面,在控制器用的芯片5b的主面上,沿着例如相向的2个长边每边一列地形成多个键合焊盘。

2块芯片5a、5a,在朝向同一方向的状态下彼此重叠起来,一方的芯片5a的键合焊盘和另一方的芯片5a的键合焊盘邻近地进行配置。此外,上层的芯片5a,其一部分在与下层的芯片5a的一边平行的方向(X方向)和与之垂直的方向(Y方向)上偏离开来的状态下进行配置。

在上述芯片5a、5b的附近的基底基板4上边,形成多个电极,与各自的芯片5a、5a、5b对应的电极,通过由金(Au)等构成的键合焊丝6进行电连。在芯片5a的键合焊盘上,通过上述电极和已电连到电极上的基底基板4的布线,电连到在基底基板4的一端上形成的连接端子7和在另一端上形成的测试焊盘8上。连接端子7被用做把该存储卡1安装到上述电子设备上时的连接端子。并通过贯通孔10电连到基底基板4的下表面的外部连接端子9上。此外,测试焊盘8在该存储卡1的组装工序中用来测定电学特性。这样的芯片5a、5b,键合焊盘6和基底基板4的器件装载面的大半(除去连接端子7和测试焊盘8及其配置区域的周边),例如被由环氧树脂等构成的密封树脂11被覆起来。

其次,对上述适配器2进行说明。图7(a)是适配器2的表面一侧的平面图,(b)是(a)的适配器2的侧视图,(c)是(a)的适配器2的前面图,(d)是(a)的适配器2的背面一侧的平面图,(e)是(a)的适配器2的爪部2b和支持部分2c的主要部分扩大剖面图。

适配器2,用刚性更高的例如不锈钢、钛(Ti)、铁(Fe)或含铁合金等之类的金属板构成,虽然也可以用树脂材料形成。在作为适配器2的材料选择不锈钢的情况下,由于耐腐蚀性高,故没有必要对其表面施行电镀处理。另一方面,在作为适配器2的材料选择铁等的情况下可以采用对其表面施行电镀处理的办法提高耐腐蚀性。

此外,适配器2的凹部2a,可以采用把适配器2的长边方向的两端弯曲为使之变成为大体上的U形的办法形成。为此,适配器2在其厚度方向上具有某种程度的空着的区域。也可以把适配器2形成为中空状。

如上所述,在本实施形态中,适配器2可以采用把1块金属板弯曲或在该金属板上形成沟2d或孔2e之类的办法形成。就是说不使用需要精密加工的金属的切削技术等。此外,部件个数少。因此,可以降低适配器2的造价。

在适配器2中,从其前面开始,沿着适配器的短方向(图7(a)、(d)的上下方向)一直到其短方向的途中平面位置为止带状地形成平行地延伸的2条上述沟2d。被该2条的沟2d平面性地挟持着的部分(适配器2的长边方向中央)上,形成上述支持部分2c。在支持部分2c的另一端上,变成为一体地形成上述爪部2a。支持部分2c具有作为板簧(弹性体)的功能,从平面上看被形成矩形形状,此外,从断面上看从适配器2的表面向着背面逐渐地弯曲那样地,就是说,在使之具有挠曲的状态下成型。如上所述,采用使支持部分2c具有挠曲的办法谋求弹力的提高,和作为弹性体的耐久性的提高。如上所述,支持部分2c理想的是其长度被设计为目的为使之具有适度弹性的长度。

此外,在适配器2的背面一侧附近,形成了孔2e的开口。在把适配器2装配到上述存储器1上的状态下,在把它装配到电子装置中之后,在从电子装置中取出该存储卡1时,在该取出不能顺利地进行时等,就可以把爪或工具钩到该孔2e内取出存储卡1。孔2e也可以作成为沟等的压痕形状而不作成为孔。

图8(a)示出了把上述适配器2装配到上述存储卡1上后的状态,图8(a)是其存储卡1和适配器2的表面的平面图,(b)是(a)的侧视图,(c)是(a)的背面的平面图。此外,图9,为了进行比较,示出了上述全尺寸的存储卡50。图9(a)是存储卡50的表面的平面图,(b)是其侧视图,(c)是其背面的平面图。再有,图10(a)示出了存储卡1的适配器爪安装部分3b、与适配器2的爪部2之间的接合部分的剖面图,(b)是存储卡1的安装部分3a与适配器2的凹部2a之间的结合部分的剖面图。

适配器2,在把存储卡1的适配器安装部分配合到其凹部2a内,而且,把适配器2的支持部分2c的顶端部分的爪部2b配合到存储卡1的适配器爪安装部分3b的沟部3b2内的状态下,装配到存储卡1上。特别是适配器2的支持部分2c,在从存储卡1的表面一侧进入到背面一侧的状态下,装配到存储卡1上。采用把适配器2装配到存储卡1上的办法,就可以作成为与全尺寸的存储卡50同等的尺寸(例如32mm×24mm×1.4mm)。因此就可以在全尺寸的存储卡50用的上述大型的电子装置中使用可以在上述小型电子装置中使用的半尺寸的存储卡1。就是说,可以提高半尺寸的存储卡1的通用性。

适配器2的爪部2b,在图10(a)的上方向,就是说,在与器件帽3相向的方向上具有弹力的状态下,被牢固地嵌入到存储卡1的适配器爪安装部分3a的沟部3b2内。借助于此,就可以确实地把存储卡1和适配器2结合起来。而且,在适配器2的凹部2a中嵌入存储卡1的适配器安装部分3a。借助于此,就可以具有良好稳定性地将存储卡1和适配器2结合起来。

在要从存储卡1上取下适配器2时,要从适配器2的表面一侧向背面的方向推压适配器2的支持部分2c,从存储卡1的适配器爪安装部分3b上拿掉支持部分2c的顶端的爪部2b即可。因此,即便是用一只手也可以简单地拿掉适配器2,其取下作业可以极其容易地进行为此,在其装配时从存储卡1的表面可以观察的支持部分2c的长度,理想的是人的手指可以进入的那种程度。另外,支持部分2c,如上所述,由于具有弹性,故拿掉适配器2之后就会回到原来的形状。

其次,说明上述存储卡1的器件帽3的形成时使用的模具的一个例子。图11是该模具15的剖面图,示出了与图5同一部位的剖面图。此外,图12,是图11的主要部分扩大剖面图,(a)是器件帽3的背面一侧的与图5(b)同一部位的剖面图,(b)是与器件帽3的背面一侧的适配器安装部分3a对应的部位的剖面图,(c)是器件帽3的前面一侧的与图5同一部位的剖面图。

在下模15a和上模15b重叠起来的部分上形成用来成型器件帽3的腔体15c。在本实施形态中,面向该腔体15c的模具15(下模15a和上模15b)的拐角部分α1~α11等已变成为90度或90度以上(参看图12)。借助于此,就可以容易地进行器件帽3的成型。如果上述角度α1~α11比90度小,则在器件帽3成型后,器件帽3就难于从模具15中剥离,由于就变成为或者每次只形成一个器件帽3,或者需要特别的模具,故造价增高。相对于此,在本实施形态中,得益于把角度α1~α11等作成为90度或90度以上,由于不会产生这样的缺点,所以就变成为可以量产的状态。此外,也不需要特别的模具。因此,可以降低存储卡1的造价。用这样的模具15成型的器件帽3的表面、侧面和背面的拐角部分的角度,变成为90度或90度以上。

此外,在本实施形态中,在形成器件帽3的内侧面的下模15a一侧处的腔体15c的深度(大体上厚度为d5+d6)这一方形成得比在形成器件帽3的外侧表面的上模15b一侧处的腔体15c的深度(大体上与厚度d7同等)更深。因此,在相当于厚度d6的部分上,大半形成向下模15a一侧流入树脂用的浇口。下模15a一侧的腔体15c的深度这一方之所以深,是因为下模15a一侧的腔体15c的内侧(底面一侧)这一方凹凸和台阶多,如果没有某种程度的容量,就不能满意地填充树脂的缘故。此外,在厚度d5到d7中,厚度d6尺寸最大。这是因为要提高从浇口向腔体15c内流入的树脂的填充性的缘故。就是说,如果该厚度d6太薄,就不可能通过浇口使树脂向腔体15c内流入。在这里,厚度d5,例如为0.5mm左右,厚度d6例如为0.6mm左右,厚度d7例如为0.3mm左右。

在本实施形态中,采用向这样的模具15的腔体内填充树脂的办法成型了器件帽3之后,盖上该器件帽3,使得把已装载上芯片5a、5b的基底基板4的器件装载面覆盖起来,以制造上边所说的存储卡1。

其次,说明本实施形态的半导体器件的组装方法的一个例子。图13是用来说明该例子的说明图,(a)是存储卡1的全体平面图,(b)是把存储卡1的基底基板4组装到全尺寸的存储卡上使用的情况下的全体平面图。带阴影的部分表示基底基板4的平面。

在本实施形态中,在全尺寸的存储卡1A中保持原状不变地使用在半尺寸的存储卡1的组装中使用的基底基板4(已经装配上芯片5a等的状态的基底基板4)。就是说,作成为使得共有平面尺寸不同的存储卡1、1A的部分。

由于存储卡的成本的大半为基底基板4的成本占有,故降低基底基板4的成本,在降低存储卡1的造价方面是有效的。但是,在半尺寸的存储卡1和全尺寸的存储卡1a中分开制造基底基板4的情况下,由于分别需要分开的制造工序、制造装置和人员等,故将招致基底基板4的造价的增大,使存储卡的造价升高。相对于此,采用使存储卡1、1A共有的办法,由于在半尺寸和全尺寸中不再需要单独设置基底基板4的制造工序、制造装置和人员,故可以大幅度地降低存储卡1、1A的造价。

在采用这样的组装方法的情况下,如图13(b)所示,在全尺寸的存储卡1A上,装配其器件帽16的平面面积的一半或一半以下的平面面积的基底基板4。

(实施形态2)

图14是本发明的另一个实施形态的半导体器件和辅助器具的斜视图,图15(a)、(b)的斜视图示出了图14的半导体器件的表面一侧和背面一侧的外观,图16(a)是图14的半导体器件的表面一侧的平面图,图16(b)是(a)的半导体器件的侧视图,图16(c)是(a)的半导体器件的背面图,图16(d)是(a)的半导体器件的背面一侧的平面图,图17(a)是图14的半导体器件和辅助器具的表面的平面图,(b)是(a)的侧视图,(c)是(a)的背面的平面图。

本实施形态,除去存储卡1与适配器2之间的结合部位的形状与上述实施形态1不同之外,与上述实施形态1是同样的。就是说,存储卡1的适配器安装部分3a的侧面,被形成为使之与存储卡1的侧面变成为同一平面。就是说,适配器安装部分3a的侧面部分不凹下去。此外,在存储卡1的侧面上,也部分地形成这样的沟2a1:上述适配器安装部分3a的侧面部分进入到要配合到该适配器安装部分3a上的适配器2的凹部2a的部分内。

即便是在这样的情况下,如图17所示,也可以在干净整洁的状态下,把适配器2安装到存储卡1上而不会在存储卡1与适配器2之间的结合侧面上产生凹凸或缺欠。

在这样本实施形态中,也可以得到与上述实施形态1同样的效果。

(实施形态3)

图18示出了作为本发明的再一个实施形态的半导体器件的背面一侧的平面图。在本实施形态中,在存储卡的背面一侧,在适配器安装部分3a的附近沿着存储卡1的长边方向规则地排列起来地配置多个连接端子17。连接端子17设置在基底基板4的背面一侧,通过基底基板4的布线与在基底基板4上边形成的存储器电路电连。该连接端子17是上述存储器电路的测试用或功能追加用的端子。

(实施形态4)

首先,用图19到图23对在本发明人所研究的技术中本发明人首先发现的课题进行说明。

图19和图20分别示出了上述基底基板4的表面(器件装载面)和背面(外部连接端子形成面)的平面图。基底基板4平面矩形形状地形成,其一个拐角部分相应部位对拐角进行倒角形成倒角部分(第3倒角部分)4a。倒角部分4a被形成为沿着在存储卡的前面顶端(安装端)上形成的定位(index)用的倒角。

图21和图22分别示出了本发明人所研究的上述全尺寸的存储卡6的器件帽(第1壳体)16的表面和背面的平面图。该器件帽16,可以用与上述半尺寸用的器件帽3同样的树脂等形成。在器件帽16中,在存储卡的前面一侧的拐角部分的一方处形成上述定位用的倒角部分(第2倒角部分)16a。该倒角部分16a是出于易于识别全尺寸的存储卡的安装方向的观点而设置的。

此外,在器件帽16的背面,在上述存储卡的前面一侧形成沟16b。该沟16b,是用来把基底基板4安装到器件帽16的沟,被形成为使得占有从器件帽16的顶端附近到器件帽16的长边方向的一半短一些的位置为止。沟16b的平面形状和尺寸,用与基底基板4同一平面形状,而且,用比基底基板4大一些的尺寸形成,以便可以收纳基底基板4并良好地进行配合。因此,在沟16b中,器件帽16的前面一侧的一方的拐角部分被倒角,形成倒角部分16b1。此外,在沟16b的2个长边之内的器件帽16的长边方向中央一侧形成的长边,和沟16b的2个短边直角地进行交叉。另外,在沟16b的区域内在外周处,形成比其内侧厚一些,而且,比沟16b的外侧薄一些的台阶部分16e。刻在该台阶部分上的多个插针痕迹16f示出了在用模具成型了器件帽16之后在从模具中取出时推卸器(ejector)插针所接触的痕迹。

此外,在该器件帽16的表面和背面中,在背面一侧附近,形成卡取出沟16c1、16c2。该卡取出沟16c1、16c2是具有与在上述实施形态1中说明的卡取出沟3c(参看图1等)同样功能的沟。在背面一侧的沟部16c2的深度形成得比在表面一侧的卡取出沟16c1更深。该卡取出沟16c1、16c2也可以仅仅设置在任何一方。此外,在器件帽16的表面上,在前面附近一侧,形成表示在把全尺寸的存储卡安装到上述电子装置中时的插入方向的平面三角形形状的标记16d。此外,器件帽16的表面的大半部分,形成平面圆角的长方形形状的浅的凹坑16g。该凹坑16g,是用来粘贴表明存储卡分类等种种信息标签的凹坑。

图23示出了把图19和图20所示的基底基板4安装到图21和图22所示的器件帽16的沟16b内之后的全尺寸的存储卡1A的背面的平面图。基底基板4被收纳于器件帽16的长边方向的大体上单侧一半的区域内,且已良好地安装好。

本发明人对图23所示的的全尺寸的存储卡1A进行了弯曲强度试验。该弯曲强度试验,例如如下所述那样进行。首先,在使存储卡1A的背面朝向试验台的上表面的状态下,把存储卡1A载置到试验台上边。这时,要作成为使得在存储卡1A的长边方向的两端附近的2个地方上,在存储卡1A的背面和试验台上表面之间存在着支持构件,在存储卡1A的背面与试验台的上表面之间形成规定尺寸的间隙。在该状态下,采用在存储卡1A的表面上给长边方向中央加上规定量的荷重的办法使存储卡1A挠曲来评价破坏强度。

本发明人第1次发现:进行该试验的结果,图23所示的那样的存储卡1A,在全尺寸的存储卡中,与把基底基板和器件帽之间的平面尺寸作成为同等程度的构造的存储卡比较,弯曲强度弱,在存储卡1A的背面中央,在器件帽16与基底基板4之间的边界部分(隙间部分)处基底基板4剥离,或者以在器件帽16的沟16b的长边之内的器件帽16的长边方向中央一侧形成的长边与沟16b的2个短边直角交叉的部分为起点,在器件帽16上产生裂纹之类的缺欠。

于是,在本实施形态中,在把基底基板的平面尺寸作成为器件帽的平面尺寸的大约一半的全尺寸的存储卡中,作成为提高上述弯曲强度的构造。具体地说,例如如下所述。

图24和图25分别示出了本实施形态4的基底基板4的表面(器件装载面)和背面(外部端子形成面)的平面图。在本实施形态4的基底基板4中,除去上述倒角部分4a之外,使2个拐角部分相当部位的拐角倒角形成倒角部分(第1倒角部分)4b、4c。该倒角部分4b、4c被倒角为比倒角部分4a更小,以同一大小和形状形成为使得互相左右对称、除此之外,与在上述实施形态1、图19和图20等中说明的情况是同样的。

图26和图27,分别示出了装载图25和图26所示的基底基板4的全尺寸的存储卡用的器件帽16的表面和背面(基底基板安装面)的平面图。本实施形态4的器件帽16,安装基底基板4的沟(第1沟)16b的形状与上边所说的形状不同。除此之外的构成,与在上述实施形态1、图21和图22中说明的构成是同样的。就是说,在本实施形态4中,沟16b的平面形状和尺寸,用与其基底基板4同一平面形状且比基底基板4大一些的平面尺寸形成为使得可以收纳图24和图25所示的基底基板4而且可以良好地进行配合。因此,在该情况下的沟16b的2个长边之内的器件帽16的长边方向中央一侧形成的长边16b2和沟16b的2个短边16b3、16b3不进行直角交叉,其本来进行交叉的部分则进行倒角,形成倒角部分(第1倒角部分)16b4、16b5。就是说,沟16b变成为这样的构造:其长边16b2和短边16b3彼此间,通过被配置为使得对于它们斜向交叉的倒角部分16b4、16b5随意地改变。或者,作成为这样的构造:在沟16b中,本来要在器件16的长边方向中央一侧形成的2个拐角部分处,在使直角部分吻合起来的状态下配置直角2等边三角形形状的增强部分16h1、16h2。该倒角部分16b4、16b5的构成为被倒角得比倒角部分16a小,并以同一大小和形状形成为彼此左右对称。

图28示出了把图24和图25所示的基底基板4安装到图26和图27的器件帽16上后的全尺寸的存储卡1A的背面的平面图,图29示出了图28的A1-A1线剖面图。在本实施形态4中,基底基板4,在使其表面朝向器件帽16的背面的沟16b一侧,而且,使基底基板4的倒角部分4b、4c分别与沟16b的倒角部分16b4、16b5相向的状态下安装到沟16b内。基底基板4,以其表面外周部分接触到器件帽16的沟16b内的台阶部分16e上的状态进行支持。

在本实施形态4中,由于可以把基底基板4与沟16b之间的接触长度形成得比图23所示的情况更长,故可以提高基底基板4与器件帽16之间的接合强度。此外还可以采用在基底基板4上设置倒角部分4b、4c,在沟16b上设置倒角部分16b4、16b5,消除应力易于集中的直角部分的办法,分散应力。借助于这些,在进行上述弯曲强度试验时,就可以抑制或防止基底基板4的剥离,此外,还可以抑制或防止在器件帽16上产生裂纹。

此外,提高上述弯曲强度的构造并不需要追加别的新的构件,仅仅是对基底基板4的拐角部分和器件帽16的沟16b的拐角部分进行倒角的简单的构造,其形成是容易的。因此,可以提供可靠性高而不会影响生产性的全尺寸的存储卡1A。

此外,本实施形态4的全尺寸的存储卡1A,被作成为即便是在静电破坏试验中也有利的构造。在该静电破坏试验中,在已把存储卡安装到试验装置上的状态下,从背面一侧加上静电。在全尺寸的存储卡中,在把基底基板和器件帽的平面尺寸作成为同等程度的构造的情况下,由于把基底基板一直设置到存储卡的背面一侧附近为止,故从存储卡的背面一侧到前面一侧的芯片为止的导电路径的距离短。相对于此,在本实施形态4的存储卡1A的情况下,从其背面到长边方向的大体上一半左右为止用绝缘性的器件帽16形成,由于从其背面一侧到前面一侧的芯片为止的导电路径的距离长,故变成为在静电破坏试验中难于产生破坏的构造。

再有,在全尺寸的存储卡1A中,在基底基板4的平面尺寸被作成为器件帽16的平面尺寸的一半左右的构造中,与把基底基板和全尺寸的器件帽的平面尺寸作成为相等的构造比,由于可以减小基底基板4的面积和密封树脂11的体积,故存储卡1A可以形成得轻。特别是在本实施形态4的存储卡1A的情况下,由于如上所述还对基底基板,的拐角部分进行倒角,故可以推进轻重量化。因此,可以改善全尺寸的存储卡1A的携带性。

图30到图32,示出了图23所示的存储卡1A的弯曲强度试验的结果的说明图。可知在该构造的存储卡1A中,在器件帽16的长边方向的大体上中央部分的基底基板4与器件帽16之间的边界部位(位置b3、b4)处,弯曲强度急剧且矩形形状地下降得很大。另外标号b1到b4使得在图30到图32中可以了解彼此间的位置关系那样地示出了位置。

另一方面,在图33到图35中,示出了在本实施形态4的图28等中所示的存储卡1A的弯曲强度试验的结果的说明图。可知,在本实施形态4存储卡1A中,在器件帽16的长边方向的大体上中央的基底基板4与器件帽16之间的边界部位(位置b5、b6、b4)处,弯曲强度的下降是比较平缓的,同时其最低值与图31和图32的比变成为高的值。就是说,可以提高全尺寸的存储卡1A的弯曲强度。

其次根据图36和图37对本实施形态4的全尺寸的存储卡1A的尺寸方面的定义进行说明。

图36示出了本实施形态4的器件帽16的背面的平面图。沟16d短方向的长度(就是说,大体上的基底基板4的短方向的尺寸)X1,比器件帽16的长边方向的全长X2的一半还小(X1<X/2)。这是因为要作成为在全尺寸和半尺寸这两方都可以使用基底基板4的缘故。就是说,如果宽度X1等于全长X2的一半或比一半还长,则在上述实施形态6说明的半尺寸的存储卡1中就不再能使用该基底基板。长度X1例如为14.5mm左右,全长X2例如为32mm左右。

此外,在本实施形态4中,在倒角部分16b4、16b5中,把器件帽16的长边方向的长度X3和器件帽16的短方向的长度Y1作成为相等(X3=Y1)。因此,角度θ为45度。理论上说,是由于该情况可以整体地提高在拐角部分区域中的弯曲强度的缘故。此外,倘采用本发明人的研究,即便是假定Y1>X3,在弯曲强度上也可以得到良好的结果。长度X3、Y1例如为2mm左右。

倒角部分16a的长度L2,比长度X3、Y1还长(L2>X3,Y1)。这是因为当长度X3、Y1太大时,基底基板4的面积就会变得过小,变得不能载置芯片的缘故。长度L2例如为5.66mm左右。

此外,该长度X3、Y1比厚度d8、d9、d10大(X3,Y1>d8,d9,d10)。这是因为如果长度X3、Y1比厚度d8、d9、d10小,则因倒角量太小而不能充分地得到上述弯曲强度的缘故。厚度d8例如为1mm左右,厚度d9、d10例如为0.6mm左右。

此外,图37示出了本实施形态4的存储卡1A的主要部分的扩大剖面图。存储卡1A的总厚度相当于器件帽16的厚度d11。该厚度d11等于或大于厚度d12(d11≥d12)。厚度d12是从器件帽16的表面到基底基板4的背面为止的厚度。上述尺寸规定的理由是:如果该厚度d12比厚度d 11还厚,则不合乎存储卡的规格。深度d13表示沟16b的深度。厚度d11例如为1.4mm左右,厚度d12例如等于或小于1.4mm左右。深度d13例如为1.04mm左右,厚度d14例如为0.28mm左右。

其次,用图38说明在图26到图29等所示的全尺寸用的器件帽16的形成时使用的模具的一个例子。图38是该模具15的剖面图。其构造与在上述实施形态1的图11和图12(a)、(c)中说明的构造大体上相同。不同的是从腔体15c的长边方向的大体上的中央到形成器件帽16的背面部分的部分为止的长度,比图11和图12所示的部分的长度更长。

其次,用图39和图40说明本实施形态4的基底基板4的芯片的配置例。图39和图40示出了本实施形态4的基底基板4的表面(器件装载面)的平面图。

在本实施形态4中,在基底基板4的表面上,装载有1个存储器用的芯片5a和1个控制器用的芯片5b等。该2个芯片5a、5b被配置为沿着基底基板4的长边方向(就是说,配置多个外部连接端子9(参看图25、图28)的方向)排列。相对地大的存储器用的芯片5a被配置在离定位一侧的倒角4a远的位置上。另一方面相对地小的控制器用的芯片5b则被配置在距定位一侧的倒角部分4a近的一侧。归因于这样的配置,可以实现小型且大容量的存储卡。

在上述存储器用的芯片5a中,形成例如16M、32字节的存储容量的存储器电路。存储器用的芯片5a这一方,被作成为比控制器用芯片5b更接近于正方形的形状。存储器用的芯片5a的一边的长度L3被形成得比控制器用的芯片5b的在长边方向上延伸的一边长度L4更长。在存储器用的芯片5a的主面上,在一边的附近,沿着该一边配置多个键合焊盘20a。存储器用的芯片5a,被装载为使得其配置有多个键合焊盘20a的一边配置在基底基板4的长边方向中央一侧,就是说配置在控制器用的芯片5b一侧。该键合焊盘20a通过键合焊丝6与基底基板4的表面的布线电连。

另一方面,在控制器用的芯片5b的主面上,在2个长边的附近,沿着该长边配置有多个键合焊盘20b。控制器用的芯片5b在基底基板4的表面上边被装载为使得其长边对于配置有存储器用芯片5a的多个键合焊盘20a的一边变成为平行。该键合焊盘20b,通过键合焊丝6与基底基板4的表面的布线电连。这样的芯片5a、5b的配置,也可以应用于上述实施形态1到实施形态3。

另外,在基底基板4的表面的长边方向的顶端一侧(已形成了倒角部分4a的一侧)形成借助于镀金等形成的金属层21。该金属层21是在密封芯片5a、5b时配置模具的浇口的部分。就是说,使得在形成密封树脂11(参看图29)时,从该金属层21一侧通过控制器用的芯片5b的配置区域向存储器用芯片5a的配置区域流入树脂。

其次,说明本实施形态4的半导体器件的组装方法的一个例子。该组装工序,与在上述实施形态1的图13中说明的工序是相同的。在这里沿着图41的流程图用图42到图46说明该组装工序。

首先,准备图42所示的那种基底基板形成体22。在该基底基板形成体22的框体22a上,通过已经连接到各个基底基板4的2个短边中央上的微细的连结部分22b把多个基底基板4连接起来。在该阶段中,一体地形成框体22a、连结部分22b和基底基板4。此外,还已经形成了基底基板4的倒角部分4b、4c。接着,如图43所示,向基底基板形成体22的各个基底基板4的表面上边,装载芯片5a、5b(图41的工序100)。这时,把相对地大的存储器用芯片5a装载到距倒角部分4a远的地方,把相对地小的控制器用芯片5b,装载到距倒角部分4a近的地方。然后,实施目的为使基底基板4和芯片5a、5b的布线、电极(包括键合焊盘20a、20b)的表面清洁化的例如等离子体清洗工序(图41的工序101)。该工序的目的是:采用对形成得薄的镀金层的表面进行清洗的办法,使得在接在该工序后边的键合焊丝工序时焊丝和镀金层之间的连接状态变得良好起来。

接着,如图44所示,在各个基底基板4中,通过键合焊丝6把芯片5a、5b的键合焊盘20a、20b和基底基板4的布线及电极电连起来(图41的工序102)。接着,如图45所示,在各个基底基板4中,用连续自动模铸法把芯片5a、5b和键合焊丝6等密封起来(图41的工序103)。在上述的焊丝键合工序之后,在模铸工序之前,出于改善密封树脂的粘接性的观点也可以对基底基板4实施上述净化处理。然后,如图46所示,采用切断连结部分22b的办法,把基底基板4从基底基板形成体22上分离出来(图41的工序104)。经这样地处理之后形成基底基板4。

接着,在要制造全尺寸(FS)的存储卡1A的情况下,把上述基底基板4安装在图26和图27所示的器件帽16的沟16内后用粘接剂等进行固定(图41的工序105A)。另一方面,在制造半尺寸(HS)(或缩小尺寸(RS))的存储卡1的情况下,则把基底基板4安装到在上述实施形态1的图1到图5等中说明的器件帽3的背面的沟(这里的沟的平面形状被形成为在图27到图29中说明的形状)内并用粘接剂等进行固定(图41的工序105B)。

如上所述,在本实施形态中,可以用1个基底基板4制造全尺寸和半尺寸这么2种的存储卡1、1A。就是说,由于全尺寸和半尺寸的存储卡1、1A的制造工序和构件可以部分共通化,故与单独制造的情况下比较,制造工序的简化、制造时间的缩短和制造成本的降低就成为可能。

(实施形态5)

在本实施形态5中,说明在把基底基板的平面尺寸作成为器件帽的平面尺寸的一半左右的全尺寸的存储卡中,改善上述弯曲强度的构造的变形例。

图47示出了实施形态5的全尺寸的存储卡1A的背面的平面图,图48示出了图47的区域Z1的扩大平面图。在本实施形态5中,在基底基板4中,在位于全尺寸的器件帽16的长边方向中央一侧的两个拐角部分的附近,形成微细的长方形形状的凹凸4d,在与之对应的器件帽16的沟16b的拐角部分附近也形成微细的长方形形状的凹凸16b7,使之很好地配合到基底基板4的微细的凹凸4d内。该微细的凹凸4d、16b7,在图47中被形成为左右对称。除此之外与在实施形态1到4中说明的是同样的。上述凹凸4d、16b7也可以设置在沟16b的长边16b2和与之对应的基底基板4的长边一侧。

在本实施形态5中,由于在强度相对地弱的拐角部分处,也增大基底基板4与器件帽16之间的接触面积,故可以抑制或防止器件帽16的裂纹或基底基板4的剥离,可以改善上述弯曲强度。

(实施形态6)

在本实施形态6中,说明在把基底基板的平面尺寸作成为器件帽的平面尺寸的一半左右的全尺寸的存储卡中,改善上述弯曲强度的构造的另一个变形例。

图49示出了实施形态6的全尺寸的存储卡1A的背面的平面图,图50示出了图50的区域Z2的扩大平面图。在本实施形态6中,与上述实施形态5同样,在位于基底基板4和与之对应的器件帽16的沟16b的拐角部分附近,也形成微细的凹凸4d、16b7。与上述实施形态不同的是,在每个微细的凹凸4d、16b7的侧面上形成锥形。在该情况下,与实施形态5的情况下比较,基底基板4的微细的凹凸4d,和器件帽16的沟16b7的微细的凹凸4d更容易配合。除此之外与在实施形态1到5中说明的是同样的。上述凹凸4d、16b7也可以设置在沟16b的长边16b2和与之对应的基底基板4的长边一侧。

(实施形态7)

在本实施形态7中,说明在把基底基板的平面尺寸作成为器件帽的平面尺寸的一半左右的全尺寸的存储卡中,改善上述弯曲强度的构造的再一个变形例。

图51示出了本实施形态7的全尺寸的存储卡1A的背面的平面图。在本实施形态7中,在基底基板4中,在位于全尺寸的器件帽16的长边方向的中央一侧的长边,与之垂直的短边的两个拐角部分的附近,形成锯齿状的微细的凹凸4d,在与之对应的器件帽16的沟16b的长边和短边上也形成微细的锯齿状的凹凸16b7,使之很好地配合到基底基板4的微细的凹凸4d内。除此之外与在实施形态1到4中说明的是同样的。因此,在本实施形态7中,也可以得到与上述实施形态4到6同样的弯曲强度方面的效果。

(实施形态8)

在本实施形态8中,对在上述实施形态4中使用在图24和图25等中所示的基底基板的半尺寸的存储卡进行说明。

图52和图53分别本实施形态8的半尺寸的存储卡1的表面和背面的平面图。在存储卡1的器件帽(第2壳体)3的前面上,一方的拐角部分被倒角形成上述定位用的倒角部分3e。该倒角部分3e是出于使得易于识别存储卡1的安装方向的观点而设置的。此外,在器件帽3的表面上,在倒角部分3e一侧,形成从存储卡1的背面向前面延伸的箭头状的标记3d2。该标记3d2表示把存储卡1安装到上述电子装置中去时的插入方向。在本实施形态8的半尺寸的存储卡1中,虽然以其短方向的顶端为前面地安装到电子装置中,但是,由于一般地说有这样的固定观念:存储卡以其长边方向的顶端为前面安装到电子装置中,所以要把标记3d表示得大一点以免产生差错。此外,在器件帽3的表面上,在离开倒角部分3e的区域上,形成平面四方形状的浅的沟3f该浅的沟3f,是粘贴表明存储卡1的记录数据的内容的标签的区域。

此外,在本实施形态8的器件帽3的背面上,形成与其基底基板4同一平面形状而且平面尺寸比基底基板4大一些的沟(第2沟)3g,使得可以收纳图24和图25所示的基底基板4并可以良好地配合。因此,在该情况下的沟3g中,存储卡1的背面附近的长边3g1与沟3g的2个短边3g2、3g2不垂直交叉,其原本交叉的部分被倒角后形成倒角部分(第1倒角部分)3g3、3g4。关于该沟3g的构造(包括倒角部分3g3、3g4),与在上述实施形态4中说明的全尺寸的器件帽16的沟16b是一样的。因此,无论在全尺寸中在半尺寸中都可以应用基底基板4。此外,基底基板4向沟3g内的安装状态也与在上述实施形态4中说明的是相同的。此外,器件帽3的背面的上述沟部3b2还起着把存储卡从电子装置中取出来时的挂沟的作用。

(实施形态9)

在本实施形态9中,说明根据存储卡的规格改变背面的外部连接端子9的个数的情况下的应对例。

图54示出了使本实施形态9的存储卡1的外部连接端子9的个数与SD卡(松下、东芝、Sun Dsik)的外部连接端子的个数一致起来的情况下的例子。在存储卡1的背面(基底基板4的背面)上,配置总数为9个的外部连接端子9。此外,图55示出了使本实施形态9的存储卡1的外部连接端子9的个数与IC卡的外部连接端子的个数一致起来的情况下的例子。在存储卡1的背面(基底基板4的背面)上使总数为13个的外部连接端子9的一部分变成为2行地进行配置,不论哪一种情况都可以应对而没有什么特别的问题。

(实施形态10)

在本实施形态10中,说明在把基底基板的平面尺寸作成为器件帽的平面尺寸的一半左右的全尺寸的存储卡中,改善上述弯曲强度的构造的再一个变形例。

图56示出了本实施形态10的全尺寸的存储卡1A的剖面图,图57是图56的主要部分扩大剖面图。在本实施形态10中,在器件帽16的沟16b的长边16b2上一体地设置帽檐部分16i。帽檐部分16i既可以沿着长边16b2延伸,也可以形成为分散到长边16b2的一部分内。采用象这样地设置帽檐部分16i的办法(就是说,采用设置增强构件的办法),在沟16b的长边16b2一侧的侧面上形成凹部16j。这样一来,借助于使基底基板4的背面一侧的一部分配合到该凹部16j内,就变成为可以牢固地固定基底基板4的构造。在这里,为了把基底基板4配合到凹部16j内,基底基板4的背面一侧的一部分,因被刻蚀掉一半而变薄。得益于这样的构造,由于可以提高上述弯曲强度,故可以抑制或防止基底基板4的剥离或器件帽16的破坏。在采用本实施形态10的构造的情况下,虽然也可以不在沟16b上设置倒角部分16b4、16b5,但是,得益于设置倒角部分16b4、16b5,可以进一步提高弯曲强度。此外,在该情况下,也可以在其倒角部分16b4、16b5的地方设置帽檐部分16i。

以上,虽然根据实施形态具体地说明了由本发明人发明的发明,但是,本发明并不限定于上述实施形态,不言而喻,在不背离本发明的要旨的范围内可以有种种的变更。

例如,适配器的支持部分的形状或个数并不限定于上述实施形态,可以有种种的变更。

此外,芯片除去焊丝键合方式的连接之外,也可以采用使用突点电极的连接方式。

在以上的说明中,虽然主要对在内置本身为把以由本发明人进行的发明为其背景的利用领域的闪速存储器(RRPROM)的存储卡中应用的情况进行了说明,但是,并不限定于此,例如也可以在例如内置SRAM(静态随机存取存储器)、FRAM(铁电随机存取存储器)或MRAM(磁性随机存取存储器)等之类的别的存储器电路的存储卡中应用。

Claims (11)

1.一种半导体器件,在将装载有半导体芯片的基板的器件装载面覆盖起来的树脂制壳体的一部分上,设置可以与用于加大上述树脂制壳体平面尺寸的金属制辅助器具的凹部进行配合的截面凸状的安装部分,其特征在于:

上述截面凸状的安装部分的状态,在上述壳体的表面一侧和背面一侧是非对称的。

2.根据权利要求1所述的半导体器件,其特征在于:

上述树脂制壳体的表面一侧的上述截面凸状的安装部分的宽度,比位于上述树脂制壳体的表面相反一侧的上述截面凸状的安装部分的宽度宽。

3.根据权利要求1所述的半导体器件,其特征在于:

在被上述截面凸状的安装部分挟持起来的部分中设置沟部,以便钩住上述金属制辅助器具的爪部,在装卸自由的状态下把上述金属制辅助器具固定到上述树脂制壳体上。

4.根据权利要求1所述的半导体器件,其特征在于:

在上述半导体芯片中形成有存储器电路。

5.根据权利要求1所述的半导体器件,其特征在于:

在壳体的厚度方向上设置一个上述截面凸状的安装部分。

6.根据权利要求1所述的半导体器件,其特征在于:

在上述截面凸状的安装部分中,配合上述金属制辅助器具凹部的方向的长度,大于上述截面凸状的安装部分的厚度。

7.根据权利要求3所述的半导体器件,其特征在于:

上述爪部设置于在金属制辅助器具上形成的支持部分的顶端。

8.根据权利要求7所述的半导体器件,其特征在于:

上述支持部分具有弹力。

9.根据权利要求7所述的半导体器件,其特征在于:

上述支持部分用板簧形成。

10.根据权利要求1所述的半导体器件,其特征在于:

上述截面凸状的安装部分,在上述树脂制壳体中,在配合上述辅助器具的面一侧的两个拐角部分处设置。

11.根据权利要求1所述的半导体器件,其特征在于:

被上述截面凸状的安装部分挟持起来的部分,比该安装部分的厚度相对地厚。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP103535/2001 | 2001-04-02 | ||

| JP2001103535 | 2001-04-02 | ||

| JP103535/01 | 2001-04-02 |

Related Child Applications (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2006100818716A Division CN100501767C (zh) | 2001-04-02 | 2001-12-28 | 存储卡 |

| CNA2006100818701A Division CN101004944A (zh) | 2001-04-02 | 2001-12-28 | 存储卡 |

| CNA2006100818720A Division CN1866277A (zh) | 2001-04-02 | 2001-12-28 | 存储卡 |

| CNB2006100818699A Division CN100435170C (zh) | 2001-04-02 | 2001-12-28 | 存储卡 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1439144A CN1439144A (zh) | 2003-08-27 |

| CN1267996C true CN1267996C (zh) | 2006-08-02 |

Family

ID=18956580

Family Applications (5)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2006100818699A Expired - Fee Related CN100435170C (zh) | 2001-04-02 | 2001-12-28 | 存储卡 |

| CNA2006100818701A Pending CN101004944A (zh) | 2001-04-02 | 2001-12-28 | 存储卡 |

| CNA2006100818720A Pending CN1866277A (zh) | 2001-04-02 | 2001-12-28 | 存储卡 |

| CNB018083439A Expired - Fee Related CN1267996C (zh) | 2001-04-02 | 2001-12-28 | 半导体器件及其制造方法 |

| CNB2006100818716A Expired - Fee Related CN100501767C (zh) | 2001-04-02 | 2001-12-28 | 存储卡 |

Family Applications Before (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2006100818699A Expired - Fee Related CN100435170C (zh) | 2001-04-02 | 2001-12-28 | 存储卡 |

| CNA2006100818701A Pending CN101004944A (zh) | 2001-04-02 | 2001-12-28 | 存储卡 |

| CNA2006100818720A Pending CN1866277A (zh) | 2001-04-02 | 2001-12-28 | 存储卡 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2006100818716A Expired - Fee Related CN100501767C (zh) | 2001-04-02 | 2001-12-28 | 存储卡 |

Country Status (9)

| Country | Link |

|---|---|

| US (8) | US6858925B2 (zh) |

| EP (2) | EP1376452B1 (zh) |

| JP (2) | JP3943502B2 (zh) |

| KR (1) | KR100551658B1 (zh) |

| CN (5) | CN100435170C (zh) |

| AT (1) | ATE360859T1 (zh) |

| DE (1) | DE60128151T2 (zh) |

| TW (1) | TWI234273B (zh) |

| WO (1) | WO2002082364A1 (zh) |

Families Citing this family (70)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3822768B2 (ja) * | 1999-12-03 | 2006-09-20 | 株式会社ルネサステクノロジ | Icカードの製造方法 |

| WO2002082364A1 (fr) * | 2001-04-02 | 2002-10-17 | Hitachi, Ltd. | Dispositif semi-conducteur et son procédé de production |

| JP3850812B2 (ja) * | 2003-05-23 | 2006-11-29 | 三和電気工業株式会社 | メモリカード用アダプタ |

| JP2003258033A (ja) * | 2002-03-06 | 2003-09-12 | Seiko Epson Corp | 電子デバイス及びその製造方法並びに電子機器 |

| EP1576589A4 (en) * | 2002-11-18 | 2006-06-07 | Storcard Inc | SECURE TRANSACTION CARD WITH HIGH VOLUME OF STORAGE |

| US6952027B2 (en) * | 2002-11-29 | 2005-10-04 | Kabushiki Kaisha Toshiba | Semiconductor integrated circuit device and electronic card using the same |

| CN1311398C (zh) * | 2003-06-04 | 2007-04-18 | 三和电气工业株式会社 | 存储器卡用适配器 |

| KR20100107057A (ko) * | 2003-07-03 | 2010-10-04 | 르네사스 일렉트로닉스 가부시키가이샤 | 반도체 카드 디바이스 |

| JP4347018B2 (ja) * | 2003-10-24 | 2009-10-21 | モレックス インコーポレイテド | メモリーカード用互換装置およびメモリーカードモジュール |

| US20050155787A1 (en) * | 2004-01-20 | 2005-07-21 | Pierre Liu | Transparent small memory card |

| JP4651332B2 (ja) * | 2004-04-26 | 2011-03-16 | ルネサスエレクトロニクス株式会社 | メモリカード |

| TWI257583B (en) * | 2004-07-28 | 2006-07-01 | C One Technology Corp | Expandable reduced-size memory card and corresponding extended memory card |

| KR100599341B1 (ko) | 2004-07-30 | 2006-08-14 | (주)테라빛 | 실장효율이 높은 메모리 카드를 제조하는 방법 |

| US20060027906A1 (en) * | 2004-08-03 | 2006-02-09 | Sheng-Chih Hsu | Exclusive memory structure applicable for multi media card and secure digital card |

| US7055751B2 (en) * | 2004-08-09 | 2006-06-06 | Chong-Ia Precision Industry Co. Ltd. | Extension piece for length-reduced memory card |

| FR2875625B1 (fr) * | 2004-09-20 | 2006-12-08 | Gemplus Sa | Support adaptateur de carte a puce deverrouillable et procede de fabrication du support |

| JP2006092094A (ja) * | 2004-09-22 | 2006-04-06 | Sony Corp | メモリカード |

| JP4506389B2 (ja) * | 2004-09-30 | 2010-07-21 | ソニー株式会社 | カード型周辺装置 |

| JP2006128459A (ja) * | 2004-10-29 | 2006-05-18 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| KR100574996B1 (ko) * | 2004-11-25 | 2006-05-02 | 삼성전자주식회사 | 반도체 패키지 및 이를 이용한 메모리 카드, 및 이의제조에 이용되는 몰드 |

| JP2006155521A (ja) * | 2004-12-01 | 2006-06-15 | Oki Electric Ind Co Ltd | Icカード |

| CN1864979A (zh) * | 2005-05-10 | 2006-11-22 | 刘钦栋 | 记忆卡封装方法 |

| TWI249772B (en) * | 2005-06-07 | 2006-02-21 | Siliconware Precision Industries Co Ltd | Semiconductor device for accommodating large chip, fabrication method thereof, and carrier used in the semiconductor device |

| US7345848B2 (en) * | 2005-11-14 | 2008-03-18 | Sun-Light Electronic Technologies Inc. | Packaging structure of mini SD memory card |

| JP4815212B2 (ja) * | 2005-12-26 | 2011-11-16 | 株式会社ディスコ | メモリーカードの製造方法 |

| JP2007179176A (ja) * | 2005-12-27 | 2007-07-12 | Disco Abrasive Syst Ltd | 配線基板及びメモリーカードの製造方法 |

| US8599571B2 (en) * | 2006-04-21 | 2013-12-03 | Panasonic Corporation | Memory card |

| KR100828956B1 (ko) * | 2006-06-27 | 2008-05-13 | 하나 마이크론(주) | Usb 메모리 패키지 및 그 제조 방법 |

| WO2008017063A2 (en) * | 2006-08-03 | 2008-02-07 | Inphase Technologies, Inc. | Miniature single actuator scanner for angle multiplexing with circularizing and pitch correction capability |

| US7705475B2 (en) * | 2006-08-03 | 2010-04-27 | Stats Chippac Ltd. | Integrated circuit package system |

| JP2010503025A (ja) | 2006-08-28 | 2010-01-28 | インフェイズ テクノロジーズ インコーポレイテッド | ホログラフィックデータシステムにおける位相共役を改良する新規なタイプのフーリエ変換(ft)レンズ(204)が提供されるこのタイプのftレンズは、独特に大きいアイソプラナティックパッチを有するこれは、組み立て許容範囲の緩和、非対称の読み取り/書き込みアーキテクチャー、および媒体における傾斜したプレートの収差に対する補償を可能にする |

| JP2010505214A (ja) * | 2006-09-29 | 2010-02-18 | インフェイズ テクノロジーズ インコーポレイテッド | ホログラフィック記憶スキャナのための磁場位置フィードバック |

| US7950586B2 (en) * | 2006-10-26 | 2011-05-31 | Sandisk Il Ltd. | SIM card handle |

| US20080102895A1 (en) * | 2006-10-26 | 2008-05-01 | Sandisk Il Ltd. | Method Of Extracting A Smart Card From A Smart Card Socket |

| WO2008121158A1 (en) * | 2007-04-02 | 2008-10-09 | Inphase Technologies, Inc. | Non-ft plane angular filters |

| US8141782B2 (en) * | 2007-07-10 | 2012-03-27 | Inphase Technologies, Inc. | Dual-use media card connector for backwards compatible holographic media card |

| CA2692870A1 (en) * | 2007-07-10 | 2009-01-15 | Inphase Technologies, Inc. | Enabling holographic media backwards compatibility with dual-use media card connector |

| US7872483B2 (en) * | 2007-12-12 | 2011-01-18 | Samsung Electronics Co., Ltd. | Circuit board having bypass pad |

| TWI358911B (en) * | 2007-12-24 | 2012-02-21 | Ind Tech Res Inst | Receiver with discrete-time down-conversion and fi |

| TWI347097B (en) * | 2007-12-31 | 2011-08-11 | Ind Tech Res Inst | Circuit with programmable signal bandwidth and method thereof |

| KR20100041514A (ko) * | 2008-10-14 | 2010-04-22 | 삼성전자주식회사 | 검사시간을 단축할 수 있는 솔리드 스테이트 드라이브 장치및 그 검사방법 |

| KR20100041515A (ko) * | 2008-10-14 | 2010-04-22 | 삼성전자주식회사 | 제거 가능한 보조 검사단자를 갖는 솔리드 스테이트 드라이브의 검사방법 |

| JP2011048756A (ja) | 2009-08-28 | 2011-03-10 | Toshiba Corp | メモリモジュール |

| US8561910B2 (en) | 2009-10-22 | 2013-10-22 | Intellipaper, Llc | Memory programming methods and memory programming devices |

| US8469271B2 (en) | 2009-10-22 | 2013-06-25 | Intellipaper, Llc | Electronic storage devices, programming methods, and device manufacturing methods |

| US8469280B2 (en) | 2009-10-22 | 2013-06-25 | Intellipaper, Llc | Programming devices and programming methods |

| WO2011127328A2 (en) | 2010-04-07 | 2011-10-13 | Intellipaper, Llc | Electronic assemblies and methods of forming electronic assemblies |

| USD667830S1 (en) * | 2011-11-29 | 2012-09-25 | Samsung Electronics Co., Ltd. | SD memory card |

| USD669479S1 (en) * | 2012-01-13 | 2012-10-23 | Research In Motion Limited | Device smart card |

| USD669478S1 (en) * | 2012-01-13 | 2012-10-23 | Research In Motion Limited | Device smart card |

| US20130258576A1 (en) * | 2012-03-29 | 2013-10-03 | Gadi Ben-Gad | Memory Card |

| US9136621B1 (en) * | 2012-08-14 | 2015-09-15 | Ciena Corporation | Guides and tab arrangement to retain a card having an edge connector and method of use |

| US9722653B2 (en) | 2012-11-08 | 2017-08-01 | Samsung Electronics Co., Ltd. | Memory card adapter |

| KR101893032B1 (ko) | 2012-11-08 | 2018-10-04 | 삼성전자주식회사 | 메모리 카드 어댑터 |

| USD707682S1 (en) * | 2012-12-05 | 2014-06-24 | Logomotion, S.R.O. | Memory card |

| JP5942078B2 (ja) * | 2013-01-28 | 2016-06-29 | 本多通信工業株式会社 | カード用コネクタ |

| US9647997B2 (en) | 2013-03-13 | 2017-05-09 | Nagrastar, Llc | USB interface for performing transport I/O |

| US9888283B2 (en) | 2013-03-13 | 2018-02-06 | Nagrastar Llc | Systems and methods for performing transport I/O |

| USD758372S1 (en) * | 2013-03-13 | 2016-06-07 | Nagrastar Llc | Smart card interface |

| USD729808S1 (en) * | 2013-03-13 | 2015-05-19 | Nagrastar Llc | Smart card interface |

| USD759022S1 (en) | 2013-03-13 | 2016-06-14 | Nagrastar Llc | Smart card interface |

| EP2982225A4 (en) * | 2013-04-05 | 2017-05-17 | PNY Technologies, Inc. | Reduced length memory card |

| USD734756S1 (en) * | 2014-04-04 | 2015-07-21 | Pny Technologies, Inc. | Reduced length memory card |

| USD732038S1 (en) * | 2014-05-04 | 2015-06-16 | Pierce Schiller | Memory card component |

| USD780763S1 (en) | 2015-03-20 | 2017-03-07 | Nagrastar Llc | Smart card interface |

| USD864968S1 (en) | 2015-04-30 | 2019-10-29 | Echostar Technologies L.L.C. | Smart card interface |

| KR102409892B1 (ko) * | 2015-08-20 | 2022-06-15 | 삼성전자주식회사 | 메모리 카드 어댑터 및 메모리 장치 |

| US11093811B2 (en) | 2017-06-05 | 2021-08-17 | Kioxia Corporation | Memory card with multiple modes, and host device corresponding to the memory card |

| US11166363B2 (en) * | 2019-01-11 | 2021-11-02 | Tactotek Oy | Electrical node, method for manufacturing electrical node and multilayer structure comprising electrical node |

| US11653463B2 (en) * | 2020-05-20 | 2023-05-16 | Western Digital Technologies, Inc. | Removable memory card with efficient card lock mechanism and pads layout |

Family Cites Families (70)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE368082C (de) * | 1913-11-19 | 1923-02-20 | George Bloesy | Verfahren zur Herstellung von hydraulischen Kalken und Zementen aus den Rueckstaenden von Feuerungsanlagen aller Art |

| CA1204213A (en) * | 1982-09-09 | 1986-05-06 | Masahiro Takeda | Memory card having static electricity protection |

| US4727246A (en) * | 1984-08-31 | 1988-02-23 | Casio Computer Co., Ltd. | IC card |

| JPS62183396A (ja) | 1986-02-07 | 1987-08-11 | 株式会社日立製作所 | 外部記憶カ−ド |

| JPS636872U (zh) | 1986-06-27 | 1988-01-18 | ||

| JPS639586A (ja) * | 1986-06-30 | 1988-01-16 | 株式会社東芝 | メモリカ−ド |

| JPS63212595A (ja) | 1987-03-02 | 1988-09-05 | 三菱電機株式会社 | 半導体モジユ−ル製造用基板 |

| JPH01184192A (ja) | 1988-01-20 | 1989-07-21 | Matsushita Electric Ind Co Ltd | Icカード用モジュールの製造方法 |

| JPH0719859B2 (ja) | 1988-12-12 | 1995-03-06 | 松下電器産業株式会社 | Icカード用モジュールの製造方法 |

| JPH02158394A (ja) | 1988-12-13 | 1990-06-18 | Fujitsu Ltd | Icカード用半導体icデバイス |

| JPH02301155A (ja) | 1989-05-16 | 1990-12-13 | Citizen Watch Co Ltd | Icモジュールの固定方法 |

| JPH03114788A (ja) | 1989-09-29 | 1991-05-15 | Citizen Watch Co Ltd | Icカード構造 |

| JPH03158297A (ja) | 1989-11-15 | 1991-07-08 | Sharp Corp | Icカード |

| JP2560895B2 (ja) | 1990-07-25 | 1996-12-04 | 三菱電機株式会社 | Icカードの製造方法およびicカード |

| DE4105869C2 (de) | 1991-02-25 | 2000-05-18 | Edgar Schneider | IC-Karte und Verfahren zu ihrer Herstellung |

| JP2672924B2 (ja) * | 1992-07-30 | 1997-11-05 | 三菱電機株式会社 | 非接触icカードとその製造方法及びテスト方法 |

| US5341141A (en) * | 1993-03-09 | 1994-08-23 | Hughes Missile Systems Company | Three dimensional imaging radar |

| JPH0668865U (ja) | 1993-03-11 | 1994-09-27 | セイコーエプソン株式会社 | Icカード |

| JPH06318390A (ja) * | 1993-03-11 | 1994-11-15 | Toshiba Corp | Icメモリカード |

| JPH0737049A (ja) | 1993-07-23 | 1995-02-07 | Toshiba Corp | 外部記憶装置 |

| US7137011B1 (en) * | 1993-09-01 | 2006-11-14 | Sandisk Corporation | Removable mother/daughter peripheral card |

| JPH07117385A (ja) | 1993-09-01 | 1995-05-09 | Toshiba Corp | 薄型icカードおよび薄型icカードの製造方法 |

| US5887145A (en) * | 1993-09-01 | 1999-03-23 | Sandisk Corporation | Removable mother/daughter peripheral card |

| JPH07210645A (ja) * | 1994-01-24 | 1995-08-11 | Sony Corp | メモリカード |

| JPH07214957A (ja) * | 1994-01-31 | 1995-08-15 | Mitsubishi Electric Corp | Icカード |

| USD368082S (en) | 1994-05-07 | 1996-03-19 | Sony Corporation | Memory card |

| JP3256374B2 (ja) * | 1994-05-27 | 2002-02-12 | 本田技研工業株式会社 | マルチビーム・レーダ装置 |

| JP3660382B2 (ja) | 1995-02-03 | 2005-06-15 | 株式会社東芝 | 情報記憶装置およびそれに用いるコネクタ部 |

| WO1996032696A1 (fr) * | 1995-04-13 | 1996-10-17 | Dai Nippon Printing Co., Ltd. | Carte et module de circuit integre |

| US5663825A (en) * | 1995-06-07 | 1997-09-02 | Martin Marietta Corporation | Stabilized step/stare scanning device |

| JPH09147545A (ja) * | 1995-09-19 | 1997-06-06 | Ricoh Co Ltd | メモリカードおよび情報処理装置 |

| JPH09147068A (ja) * | 1995-11-17 | 1997-06-06 | Toshiba Corp | Icカード読取書込装置 |

| JPH09171863A (ja) * | 1995-12-19 | 1997-06-30 | Mitsubishi Electric Corp | Icカード用アダプタ及び該アダプタとicカードとの接続構造 |

| DE19606789C2 (de) * | 1996-02-23 | 1998-07-09 | Orga Kartensysteme Gmbh | Kunststoffkarte mit aus dieser heraustrennbarer Minichipkarte |

| JPH09286187A (ja) | 1996-04-22 | 1997-11-04 | Toppan Printing Co Ltd | Icカード、icカード製造用中間体およびicカードの製造方法 |

| JPH09315061A (ja) * | 1996-06-03 | 1997-12-09 | Minolta Co Ltd | Icカードおよびicカード装着装置 |

| DE19626791C2 (de) * | 1996-07-03 | 2002-10-31 | Gemplus Gmbh | Chipkarte sowie Verfahren zur Herstellung einer Chipkarte |

| JPH1095031A (ja) | 1996-09-24 | 1998-04-14 | Dainippon Printing Co Ltd | 情報カードの成形金型及び成形方法並びに情報カード |

| DE19713641A1 (de) * | 1997-04-02 | 1998-10-08 | Ods Gmbh & Co Kg | Minichipkarte sowie Verfahren zu ihrer Herstellung |

| KR100255108B1 (en) | 1997-06-18 | 2000-05-01 | Samsung Electronics Co Ltd | Chip card |

| JPH1131207A (ja) * | 1997-07-11 | 1999-02-02 | Toppan Printing Co Ltd | 非接触型icカードとその非常時読出方法 |

| US5987357A (en) * | 1997-07-30 | 1999-11-16 | Intermedics Inc. | Stackable microelectronic components with self-addressing scheme |

| TW407364B (en) * | 1998-03-26 | 2000-10-01 | Toshiba Corp | Memory apparatus, card type memory apparatus, and electronic apparatus |

| JP2000011130A (ja) | 1998-03-26 | 2000-01-14 | Toshiba Corp | 記憶装置、カ―ド型記憶装置、および電子装置 |

| US6040622A (en) | 1998-06-11 | 2000-03-21 | Sandisk Corporation | Semiconductor package using terminals formed on a conductive layer of a circuit board |

| US6193163B1 (en) * | 1998-08-31 | 2001-02-27 | The Standard Register Company | Smart card with replaceable chip |

| US6279114B1 (en) * | 1998-11-04 | 2001-08-21 | Sandisk Corporation | Voltage negotiation in a single host multiple cards system |

| JP2000148953A (ja) | 1998-11-16 | 2000-05-30 | Hitachi Ltd | メモリカード |

| JP3391375B2 (ja) * | 1999-03-02 | 2003-03-31 | 日本電気株式会社 | Icカードを備えた携帯電話機用バッテリ |

| FI107973B (fi) * | 1999-03-11 | 2001-10-31 | Nokia Mobile Phones Ltd | Menetelmä ja välineet lisäkorttien käyttämiseksi matkaviestimessä |

| JP2000276573A (ja) * | 1999-03-23 | 2000-10-06 | Hitachi Ferrite Electronics Ltd | メモリーカード及びメモリーカードアダプタ |

| JP3590543B2 (ja) | 1999-04-09 | 2004-11-17 | 新日本製鐵株式会社 | 高炉への含鉄粉吹き込み方法 |

| JP2000305662A (ja) * | 1999-04-23 | 2000-11-02 | Jst Mfg Co Ltd | カード接続用アダプタ |

| DE19922063A1 (de) * | 1999-05-14 | 2000-11-23 | Bosch Gmbh Robert | Adapterkarte und Kommunikationsvorrichtung |

| DE19929912A1 (de) * | 1999-06-29 | 2001-01-18 | Orga Kartensysteme Gmbh | Trägerelement für einen IC-Baustein |

| JP2001043700A (ja) * | 1999-08-02 | 2001-02-16 | Fujitsu Ltd | 半導体記憶装置 |

| FI109447B (fi) * | 1999-08-10 | 2002-07-31 | Nokia Corp | Korttisovitin |

| JP2001067303A (ja) * | 1999-08-24 | 2001-03-16 | Toshiba Corp | カード利用装置及び同装置におけるカード利用方法 |

| JP3822768B2 (ja) | 1999-12-03 | 2006-09-20 | 株式会社ルネサステクノロジ | Icカードの製造方法 |

| JP2001184475A (ja) | 1999-12-27 | 2001-07-06 | Hitachi Ltd | メモリカード |

| JP3768761B2 (ja) | 2000-01-31 | 2006-04-19 | 株式会社日立製作所 | 半導体装置およびその製造方法 |

| KR100335717B1 (ko) | 2000-02-18 | 2002-05-08 | 윤종용 | 고용량 메모리 카드 |

| JP2001297307A (ja) * | 2000-04-12 | 2001-10-26 | Sony Corp | アダプタおよび電子カードモジュール |

| KR100335716B1 (ko) | 2000-05-23 | 2002-05-08 | 윤종용 | 메모리 카드 |

| US7107378B1 (en) * | 2000-09-01 | 2006-09-12 | Sandisk Corporation | Cooperative interconnection and operation of a non-volatile memory card and an input-output card |

| US6624005B1 (en) | 2000-09-06 | 2003-09-23 | Amkor Technology, Inc. | Semiconductor memory cards and method of making same |

| US6462273B1 (en) | 2001-03-16 | 2002-10-08 | Micron Technology, Inc. | Semiconductor card and method of fabrication |

| WO2002082364A1 (fr) * | 2001-04-02 | 2002-10-17 | Hitachi, Ltd. | Dispositif semi-conducteur et son procédé de production |

| US6774851B1 (en) * | 2001-09-28 | 2004-08-10 | Her Majesty In Right Of Canada, As Represented By The Minister Of Industry | Antenna with variable phase shift |

| US20080100510A1 (en) * | 2006-10-27 | 2008-05-01 | Bonthron Andrew J | Method and apparatus for microwave and millimeter-wave imaging |

-

2001

- 2001-12-28 WO PCT/JP2001/011640 patent/WO2002082364A1/ja active IP Right Grant

- 2001-12-28 DE DE60128151T patent/DE60128151T2/de not_active Expired - Lifetime

- 2001-12-28 AT AT01274083T patent/ATE360859T1/de not_active IP Right Cessation

- 2001-12-28 CN CNB2006100818699A patent/CN100435170C/zh not_active Expired - Fee Related

- 2001-12-28 CN CNA2006100818701A patent/CN101004944A/zh active Pending

- 2001-12-28 KR KR1020027014021A patent/KR100551658B1/ko not_active IP Right Cessation

- 2001-12-28 CN CNA2006100818720A patent/CN1866277A/zh active Pending

- 2001-12-28 EP EP01274083A patent/EP1376452B1/en not_active Expired - Lifetime

- 2001-12-28 JP JP2002580253A patent/JP3943502B2/ja not_active Expired - Fee Related

- 2001-12-28 US US10/240,187 patent/US6858925B2/en not_active Expired - Lifetime

- 2001-12-28 EP EP07003853A patent/EP1788512A1/en not_active Withdrawn

- 2001-12-28 CN CNB018083439A patent/CN1267996C/zh not_active Expired - Fee Related

- 2001-12-28 CN CNB2006100818716A patent/CN100501767C/zh not_active Expired - Fee Related

-

2002

- 2002-02-08 TW TW091102479A patent/TWI234273B/zh not_active IP Right Cessation

- 2002-10-10 US US10/267,784 patent/US7053471B2/en not_active Expired - Fee Related

-

2003

- 2003-02-12 US US10/364,345 patent/US20030117785A1/en not_active Abandoned

-

2005

- 2005-08-16 US US11/203,969 patent/US7233058B2/en not_active Expired - Fee Related

- 2005-08-16 US US11/204,047 patent/US7239011B2/en not_active Expired - Fee Related

-

2006

- 2006-05-10 US US11/431,072 patent/US7294918B2/en not_active Expired - Fee Related

- 2006-05-10 US US11/431,074 patent/US7271475B2/en not_active Expired - Fee Related

-

2009

- 2009-02-19 JP JP2009036042A patent/JP2009151815A/ja active Pending

- 2009-07-23 US US12/508,089 patent/US20090283885A1/en not_active Abandoned

Also Published As

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1267996C (zh) | 半导体器件及其制造方法 | |

| CN1155084C (zh) | 引线框架及其制造方法、半导体装置及其制造方法 | |

| CN1118380C (zh) | 装有电路芯片的卡及电路芯片组件 | |

| CN1324701C (zh) | 具有窄间距化的内引线的半导体装置 | |

| CN1190839C (zh) | 连接端凸点架及其制造方法 | |

| CN1514499A (zh) | 压电振荡器以及使用压电振荡器的便携式电话装置以及使用压电振荡器的电子设备 | |

| CN1512445A (zh) | Ic卡及其制造方法 | |

| CN1834997A (zh) | 一种用于存储卡的适配器和一种存储卡 | |

| CN1641873A (zh) | 多芯片封装、其中使用的半导体器件及其制造方法 | |

| CN1519948A (zh) | 半导体晶片,固态成像器件和光学器件模块及二者的制造方法 | |

| CN1237610C (zh) | 板状体及半导体装置的制造方法 | |

| CN1167127C (zh) | 半导体器件 | |

| CN1351376A (zh) | 半导体模块及其制造方法 | |

| CN1918783A (zh) | 压电振荡器及其制造方法 | |

| JP3838571B2 (ja) | 固体撮像装置の製造方法 | |

| CN1196576A (zh) | 塑料封装的半导体器件及其制造方法 | |

| CN1610194A (zh) | 集成电路卡 | |

| CN1469461A (zh) | 半导体器件和制造半导体器件的方法 | |

| CN1925320A (zh) | 表面安装式压电振动器及其制造方法、振荡器、电子设备以及无线电波时计 | |

| US9368424B2 (en) | Method of fabricating a semiconductor device used in a stacked-type semiconductor device | |

| CN1201381C (zh) | 半导体器件的制造方法、冲压模具、导轨 | |

| CN1203343C (zh) | 平台的制造方法,光模块及其制造方法以及光传输装置 | |

| CN1245854C (zh) | 安装底板及其制造方法以及电子电路元件的安装方法 | |

| CN1839473A (zh) | 半导体封装体及其制造方法 | |

| JP2005209805A (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C41 | Transfer of patent application or patent right or utility model | ||

| TR01 | Transfer of patent right |

Effective date of registration: 20160729 Address after: Tokyo, Japan Patentee after: Renesas Electronics Corporation Address before: Tokyo, Japan Patentee before: Hitachi Ltd. Patentee before: Hitachi Superlarge-Scale Integrated Circuit System Co., Ltd. |

|

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20060802 Termination date: 20171228 |