CN1417841A - 半导体器件及其制造方法 - Google Patents

半导体器件及其制造方法 Download PDFInfo

- Publication number

- CN1417841A CN1417841A CN02148256A CN02148256A CN1417841A CN 1417841 A CN1417841 A CN 1417841A CN 02148256 A CN02148256 A CN 02148256A CN 02148256 A CN02148256 A CN 02148256A CN 1417841 A CN1417841 A CN 1417841A

- Authority

- CN

- China

- Prior art keywords

- substrate

- adhesive member

- peel ply

- film

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 116

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 25

- 239000000758 substrate Substances 0.000 claims abstract description 406

- 239000000853 adhesive Substances 0.000 claims abstract description 324

- 230000001070 adhesive effect Effects 0.000 claims abstract description 324

- 239000010408 film Substances 0.000 claims abstract description 214

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims abstract description 38

- 229910052710 silicon Inorganic materials 0.000 claims abstract description 38

- 239000010703 silicon Substances 0.000 claims abstract description 38

- 239000002985 plastic film Substances 0.000 claims abstract description 35

- 229920006255 plastic film Polymers 0.000 claims abstract description 34

- 239000010409 thin film Substances 0.000 claims abstract description 23

- 238000006243 chemical reaction Methods 0.000 claims abstract description 12

- 239000000463 material Substances 0.000 claims description 150

- 238000000034 method Methods 0.000 claims description 73

- 239000004973 liquid crystal related substance Substances 0.000 claims description 38

- 239000002904 solvent Substances 0.000 claims description 29

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 28

- 230000015572 biosynthetic process Effects 0.000 claims description 27

- 239000004033 plastic Substances 0.000 claims description 23

- 229920003023 plastic Polymers 0.000 claims description 23

- 239000011521 glass Substances 0.000 claims description 22

- 239000000203 mixture Substances 0.000 claims description 18

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 17

- 229910052751 metal Inorganic materials 0.000 claims description 16

- 239000010453 quartz Substances 0.000 claims description 16

- 239000002184 metal Substances 0.000 claims description 15

- 239000012528 membrane Substances 0.000 claims description 14

- OBNDGIHQAIXEAO-UHFFFAOYSA-N [O].[Si] Chemical compound [O].[Si] OBNDGIHQAIXEAO-UHFFFAOYSA-N 0.000 claims description 11

- 239000011261 inert gas Substances 0.000 claims description 8

- 210000002858 crystal cell Anatomy 0.000 claims description 7

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical group N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 6

- -1 memory element Substances 0.000 claims description 4

- 238000004090 dissolution Methods 0.000 claims description 3

- 230000009467 reduction Effects 0.000 abstract description 5

- 239000000701 coagulant Substances 0.000 abstract description 2

- 239000012535 impurity Substances 0.000 description 53

- 230000008569 process Effects 0.000 description 41

- 238000005530 etching Methods 0.000 description 40

- 239000007789 gas Substances 0.000 description 20

- 230000014509 gene expression Effects 0.000 description 19

- 238000010438 heat treatment Methods 0.000 description 18

- 239000011347 resin Substances 0.000 description 18

- 229920005989 resin Polymers 0.000 description 18

- 229910052760 oxygen Inorganic materials 0.000 description 16

- 229910052721 tungsten Inorganic materials 0.000 description 15

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 14

- 238000005516 engineering process Methods 0.000 description 14

- 229910017083 AlN Inorganic materials 0.000 description 13

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 13

- 150000002894 organic compounds Chemical class 0.000 description 13

- 239000001301 oxygen Substances 0.000 description 13

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 12

- 239000011248 coating agent Substances 0.000 description 12

- 238000000576 coating method Methods 0.000 description 12

- 239000011159 matrix material Substances 0.000 description 12

- 239000010937 tungsten Substances 0.000 description 12

- 229910052739 hydrogen Inorganic materials 0.000 description 11

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 11

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 10

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 10

- 230000004888 barrier function Effects 0.000 description 10

- 239000013078 crystal Substances 0.000 description 10

- 238000002425 crystallisation Methods 0.000 description 10

- 230000008025 crystallization Effects 0.000 description 10

- 150000002500 ions Chemical class 0.000 description 10

- 229910052814 silicon oxide Inorganic materials 0.000 description 10

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 10

- 229910021417 amorphous silicon Inorganic materials 0.000 description 9

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 9

- 238000012545 processing Methods 0.000 description 9

- 239000000956 alloy Substances 0.000 description 8

- 238000010276 construction Methods 0.000 description 8

- 239000001257 hydrogen Substances 0.000 description 8

- 229910052757 nitrogen Inorganic materials 0.000 description 8

- 238000000926 separation method Methods 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 7

- 229910052786 argon Inorganic materials 0.000 description 7

- 150000001875 compounds Chemical class 0.000 description 7

- 238000009413 insulation Methods 0.000 description 7

- 229910052698 phosphorus Inorganic materials 0.000 description 7

- 239000011574 phosphorus Substances 0.000 description 7

- 230000005855 radiation Effects 0.000 description 7

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 6

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 6

- 238000001994 activation Methods 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 6

- 238000007639 printing Methods 0.000 description 6

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 5

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 5

- 230000004913 activation Effects 0.000 description 5

- 239000000919 ceramic Substances 0.000 description 5

- 239000004020 conductor Substances 0.000 description 5

- 230000005284 excitation Effects 0.000 description 5

- 238000000605 extraction Methods 0.000 description 5

- 229960002050 hydrofluoric acid Drugs 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- 230000003287 optical effect Effects 0.000 description 5

- 239000004417 polycarbonate Substances 0.000 description 5

- 229920000515 polycarbonate Polymers 0.000 description 5

- 238000007789 sealing Methods 0.000 description 5

- 238000005452 bending Methods 0.000 description 4

- 238000010790 dilution Methods 0.000 description 4

- 239000012895 dilution Substances 0.000 description 4

- 230000005684 electric field Effects 0.000 description 4

- 239000003822 epoxy resin Substances 0.000 description 4

- 238000005984 hydrogenation reaction Methods 0.000 description 4

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 229910010272 inorganic material Inorganic materials 0.000 description 4

- 239000011147 inorganic material Substances 0.000 description 4

- 238000005259 measurement Methods 0.000 description 4

- 238000006396 nitration reaction Methods 0.000 description 4

- 230000003647 oxidation Effects 0.000 description 4

- 238000007254 oxidation reaction Methods 0.000 description 4

- 229920000647 polyepoxide Polymers 0.000 description 4

- 239000010935 stainless steel Substances 0.000 description 4

- 229910001220 stainless steel Inorganic materials 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- NIXOWILDQLNWCW-UHFFFAOYSA-M Acrylate Chemical compound [O-]C(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-M 0.000 description 3

- 239000004925 Acrylic resin Substances 0.000 description 3

- 229920000178 Acrylic resin Polymers 0.000 description 3

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- 239000012298 atmosphere Substances 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 238000005253 cladding Methods 0.000 description 3

- 230000006835 compression Effects 0.000 description 3

- 238000007906 compression Methods 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 238000009616 inductively coupled plasma Methods 0.000 description 3

- 230000008595 infiltration Effects 0.000 description 3

- 238000001764 infiltration Methods 0.000 description 3

- 230000003434 inspiratory effect Effects 0.000 description 3

- 239000012212 insulator Substances 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000003960 organic solvent Substances 0.000 description 3

- 239000000123 paper Substances 0.000 description 3

- 239000002245 particle Substances 0.000 description 3

- 238000000053 physical method Methods 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 229920005591 polysilicon Polymers 0.000 description 3

- 229920001296 polysiloxane Polymers 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 239000011787 zinc oxide Substances 0.000 description 3

- 229910000632 Alusil Inorganic materials 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 2

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 2

- 239000004696 Poly ether ether ketone Substances 0.000 description 2

- 239000004697 Polyetherimide Substances 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 239000002800 charge carrier Substances 0.000 description 2

- 230000002950 deficient Effects 0.000 description 2

- 239000008393 encapsulating agent Substances 0.000 description 2

- 229920002457 flexible plastic Polymers 0.000 description 2

- 150000002431 hydrogen Chemical class 0.000 description 2

- 238000005286 illumination Methods 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- 239000004615 ingredient Substances 0.000 description 2

- 238000009434 installation Methods 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 238000004020 luminiscence type Methods 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 238000000465 moulding Methods 0.000 description 2

- 238000012856 packing Methods 0.000 description 2

- 229920002492 poly(sulfone) Polymers 0.000 description 2

- 229920001230 polyarylate Polymers 0.000 description 2

- 229920001707 polybutylene terephthalate Polymers 0.000 description 2

- 229920002530 polyetherether ketone Polymers 0.000 description 2

- 229920001601 polyetherimide Polymers 0.000 description 2

- 229920005644 polyethylene terephthalate glycol copolymer Polymers 0.000 description 2

- 238000004151 rapid thermal annealing Methods 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- 239000007921 spray Substances 0.000 description 2

- 239000004575 stone Substances 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 108091064702 1 family Proteins 0.000 description 1

- 206010058490 Hyperoxia Diseases 0.000 description 1

- 206010021033 Hypomenorrhoea Diseases 0.000 description 1

- 229910000846 In alloy Inorganic materials 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- 240000001439 Opuntia Species 0.000 description 1

- 229910002668 Pd-Cu Inorganic materials 0.000 description 1

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 239000004809 Teflon Substances 0.000 description 1

- 229920006362 Teflon® Polymers 0.000 description 1

- 229910001069 Ti alloy Inorganic materials 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- MQRWBMAEBQOWAF-UHFFFAOYSA-N acetic acid;nickel Chemical compound [Ni].CC(O)=O.CC(O)=O MQRWBMAEBQOWAF-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000002776 aggregation Effects 0.000 description 1

- 238000004220 aggregation Methods 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- UQZIWOQVLUASCR-UHFFFAOYSA-N alumane;titanium Chemical compound [AlH3].[Ti] UQZIWOQVLUASCR-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 210000004027 cell Anatomy 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 230000000052 comparative effect Effects 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 238000006356 dehydrogenation reaction Methods 0.000 description 1

- 230000000881 depressing effect Effects 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 239000000975 dye Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000001962 electrophoresis Methods 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 239000000945 filler Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- 230000000222 hyperoxic effect Effects 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 229910003437 indium oxide Inorganic materials 0.000 description 1

- MRNHPUHPBOKKQT-UHFFFAOYSA-N indium;tin;hydrate Chemical compound O.[In].[Sn] MRNHPUHPBOKKQT-UHFFFAOYSA-N 0.000 description 1

- 230000000977 initiatory effect Effects 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 230000002045 lasting effect Effects 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 239000000696 magnetic material Substances 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 230000013011 mating Effects 0.000 description 1

- 229910001092 metal group alloy Inorganic materials 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910052752 metalloid Inorganic materials 0.000 description 1

- 150000002738 metalloids Chemical class 0.000 description 1

- 230000005012 migration Effects 0.000 description 1

- 238000013508 migration Methods 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- 229940078494 nickel acetate Drugs 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 238000013021 overheating Methods 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 239000012466 permeate Substances 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 239000011112 polyethylene naphthalate Substances 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000012797 qualification Methods 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 239000003232 water-soluble binding agent Substances 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- OYQCBJZGELKKPM-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O-2].[Zn+2].[O-2].[In+3] OYQCBJZGELKKPM-UHFFFAOYSA-N 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76264—SOI together with lateral isolation, e.g. using local oxidation of silicon, or dielectric or polycristalline material refilled trench or air gap isolation regions, e.g. completely isolated semiconductor islands

- H01L21/76275—Vertical isolation by bonding techniques

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1218—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition or structure of the substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1262—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate

- H01L27/1266—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate the substrate on which the devices are formed not being the final device substrate, e.g. using a temporary substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78603—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the insulating substrate or support

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

- H10K71/50—Forming devices by joining two substrates together, e.g. lamination techniques

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

Abstract

提供一种总体上既轻且薄并且具有柔性(可弯曲)的半导体器件,它具有半导体元件(薄膜晶体管、薄膜二极管、硅PIN结的光电转换元件或硅电阻元件),以及制造所述半导体器件的方法。在本发明中,并非在塑料膜上形成元件。相反,诸如衬底的平板被用作模板,利用作为第二粘合构件(16)的凝结剂(一般为粘合剂)填充衬底(第三衬底(17))和包括元件的层(剥离层(13))之间的间隙,并且在粘合剂凝结后剥去用作模板的衬底,从而单独用凝结的粘合剂(第二粘合构件(16))固定包括元件的层(剥离层(13))。以这种方式,本发明使膜变薄并且重量减轻。

Description

技术领域

本发明涉及具有由薄膜晶体管(在下文中被称为TFT)构成的电路的半导体器件以及制造所述半导体器件的方法。例如,本发明涉及以液晶模块为代表的电光器件;以电致发光显示器件为代表的发光器件;以及其上安装了这种器件作为其一部分的电子装置。

应该注意,在本说明书中,术语“半导体器件”表示一般能够利用半导体特性来工作的器件,并且电致发光器件、发光器件、半导体电路以及电子部件都是半导体器件。

背景技术

近年来,利用在具有绝缘表面的衬底上形成的半导体薄膜来构成薄膜晶体管(TFT)的技术受人关注。薄膜晶体管被广泛地应用于诸如IC、电光器件等的电子器件,并且特别迫切需要将其开发作为图像显示装置的开关元件。

尽管在利用这种图像显示装置的应用方面,期待着各种应用,但是它在便携式装置中的应用特别受人关注。目前,尽管采用了许多玻璃衬底和石英衬底,但都有易断裂且笨重的缺陷。此外,玻璃衬底和石英衬底在进行批量生产方面难以做得更大,并且它们也不适于那样做。因此,已经开始进行在具有柔性的衬底(有代表性的是在柔性塑料薄膜上)形成TFT元件的尝试。

但是,由于塑料膜的耐热性差,它无法帮助降低处理过程的最高温度。结果,目前形成的TFT与那些在玻璃衬底上形成的TFT相比就没有那么好的电特性。所以,目前尚未实现利用塑料膜获得高性能的液晶显示器件和发光元件。

若可以在诸如塑料膜的柔性衬底上形成具有有机发光器件(OLED)的液晶显示器件或发光元件,则可以得到即薄且轻的器件并可用于具有曲面、陈列陈列橱窗等的显示器中。这种器件的应用不限于用作便携式装置,同时这种器件的应用范围显著地宽广。

此外,由于塑料膜对光的透明度低于玻璃衬底对光的透明度,因此它不仅依赖于材料质量和透光的塑料膜的厚度,而且存在透明度变得稍差的问题。

发明内容

本发明的一个目的是提供由具有薄的膜厚度、轻的重量和柔性(可弯曲)的半导体元件(薄膜晶体管、存储元件、薄膜二极管、光电转换元件以及由硅的PIN结构成的硅电阻元件)形成的半导体部件及其生产方法。

在本发明中,并非在塑料膜上形成元件。相反,本发明的特征在于:将平板状的衬底用作模板,衬底和包括元件的层之间的间隙用凝结剂填充(一般为粘合剂),以及在粘合剂凝结后剥去用作模板的衬底,从而单独用凝结的粘合剂(粘合构件)固定包括元件的层。粘合构件坚固地粘附于包括元件的层。

根据本说明书中公开的本发明的结构,提供一种半导体器件,其特征在于:粘合构件用作支撑体并且在与粘合构件接触的绝缘模上形成元件。

在上述结构中,所述元件是薄膜晶体管、具有OLED的发光元件、液晶元件、存储元件、薄膜二极管、硅PIN结的光电转换元件或硅电阻元件。

可适当地设置粘合构件的厚度。如果粘合构件比塑料膜薄,则半导体器件可以更薄、更轻以及更软。当粘合构件单独固定包括元件的层时,总厚度可为0.5mm(毫米)或更薄,例如最好为0.1mm到0.3mm或更薄。

可适当地选择粘合构件的材料。例如热可弯材料、光敏材料或光透射材料可被用作粘合构件。当来自发光显示装置的发光元件的光要通过粘合构件时,通过的光量可以较大,从而可以提高亮度。具有OLED的发光器件需要可通过阻挡来自外界的湿气和氧的渗入而起屏障作用的粘合构件,因为该器件无力抵御湿气和氧。

如果来自后灯的光要穿透粘合构件,最好为可透射的液晶显示装置选择高度透射光的粘合构件。可通过使粘合构件薄于塑料膜来增加通过的光量。

与采用由粘合构件粘接的塑料膜的情况比较,本发明可提高光的可用性,以改善亮度并增加通过的光量。这是因为本发明通过利用只由粘合构件构成的支撑体、仅允许光在空气和粘合构件之间的界面衍射,而不是因为折射率不同的原因使光在空气和塑料膜之间的界面以及塑料膜和粘合构件之间的界面衍射(尽管这还取决于材料)。

在上述结构中,可以形成与粘合构件接触的保护模。

在上述结构中,半导体器件的特征在于:粘合构件被粘贴在平面或曲面基底部件上,并且可得到即薄且轻的半导体器件。这种半导体器件的示例包括摄像机、数字照相机、护目镜型的显示器、用于汽车和机器(例如汽车导航系统和速度计)的指示器、个人计算机以及便携式信息终端。为了将粘合构件和基底部件粘在一起,可采用与粘合构件相同的材料或采用不同的粘合剂。可通过将粘合构件粘贴到塑料膜上并接着将该塑料膜粘贴到基底部件上来将粘合构件粘在基底部件上。

获得上述结构的工艺也是本发明的一个方面。所述工艺的特征在于:在第一衬底上形成要剥离的包括半导体元件的层;利用第一粘合构件将第二衬底粘合到要剥离的层上;剥离第一衬底;利用第二粘合构件将第三衬底粘合到剥离层上,从而将剥离层夹在第二衬底和第三衬底之间;通过用溶剂去除第一粘合构件或通过用光(紫外光、激光等)降低第一粘合构件的粘合力来剥离第二衬底;以及剥离第三衬底。换句话说,本说明书中公开的本发明的一个方面涉及一种制造半导体器件的方法,其中包括:在第一衬底上形成要剥离的包括半导体元件的层的第一步骤;利用第一粘合构件将第二衬底粘合到要剥离的层上,从而将这个要剥离的层夹在第一衬底和第二衬底之间的第二步骤;从该要剥离的层上分离第一衬底的第三步骤;利用第二粘合构件将第三衬底粘合到剥离层上,从而将这个剥离层夹在第二衬底和第三衬底之间的第四步骤;以及从该剥离层上分离第二衬底并从第二粘合构件分离第三衬底以形成利用第二粘合构件作为支撑体的剥离层的第五步骤。

在上述第五步骤中,在同一步骤中从剥离层分离了第二衬底和第三衬底这两个衬底。显然,第二衬底和第三衬底可在不同步骤中分离,它们中的哪一个首先分离不是固定的。

第一粘合构件由可用溶剂或光去除或减少粘合力的材料构成。第二粘合构件可具有与第一粘合构件不同的成分。

本发明的特征在于:为了剥离第三衬底,第二粘合构件粘合于剥离层的粘合力大于它到第三衬底的粘合力。因此,为了降低第二粘合构件到第三衬底的粘合力,玻璃衬底、石英衬底或金属衬底被用来作第一衬底和第二衬底,而塑料衬底被用来做第三衬底。或者,第三衬底可以是在其表面上形成了AlNXOY膜的塑料膜,以便降低第二粘合构件到第三衬底的粘合力。第二粘合构件在它与第二衬底接触时被固化。因此第二粘合构件的一侧是平的而第二粘合构件的另一侧紧紧地粘贴在剥离层上。

第二粘合构件因此最终被用作支撑体。因此本发明中器件的总厚度和总重量能够小于用塑料衬底作支撑体的情况。

剥离层指的是包括半导体元件的层。剥离层是包括一个或多个元件的层,所述一个或多个元件选自包括薄膜晶体管、具有OLED的发光元件、液晶元件、存储元件、薄膜二极管、硅PIN结的光电转换元件以及硅电阻元件的组。

当光穿过第二粘合构件时,第二粘合构件最好用可高度透射光的材料。例如,如果OLED发射的光或来自后灯的光要穿过第二粘合构件,则光的透射率可以通过调整第二粘合构件的厚度来改善。

还可能通过调整第二粘合构件的厚度来提供整个器件的柔性性。所以第二粘合构件可以粘合到各种基底部件上。基底部件可具有平面或曲面,或可以是可弯曲的,或可以是象膜一样的。基底部件的材料可具有任何成分,比如塑料、玻璃、金属或陶瓷。如果粘合构件被粘在曲面基底部件上,就得到曲面显示器并被用作仪表盘、陈列陈列橱窗等上的指示器。

尽管在上述制造工艺中将第二粘合构件单独用作支撑体,但第一粘合构件也可单独用作支撑体。在这种情况下,第一粘合构件和第二粘合构件的材料按需选择,例如,不溶于某溶剂的材料被用作第一粘合构件而可溶解于该溶剂的材料被用作第二粘合构件。在粘合了粘合构件之后,将它们浸入溶剂中,以剥离第二衬底和第三衬底,使第一粘合构件独自用作支撑体。当支撑体是第一粘合构件自身时,粘合构件与剥离层的最上层接触。尽管在上述制造工艺中将第二粘合构件单独用作支撑体,但第一粘合构件或第二粘合构件也可单独用作支撑体。在这种情况下,适当地选择第一粘合构件和第二粘合构件的材料。本说明书中公开的本发明的另一结构涉及一种制造半导体器件的方法,其中包括:在第一衬底上形成要剥离的包括半导体元件的层的第一步骤;利用第一粘合构件将第二衬底粘合到要剥离的层上,从而将这个要剥离的层夹在第一衬底和第二衬底之间的第二步骤;从该要剥离的层上分离第一衬底的第三步骤;利用第二粘合构件将第三衬底粘合到剥离层上,从而将该剥离层夹在第二衬底和第三衬底之间的第四步骤;以及从该剥离层上分离第三衬底并从该剥离层上分离第二衬底以形成用第一粘合构件和第二粘合构件作支撑体的剥离层的第五步骤。

在上述第五步骤中,在同一步骤中从剥离层分离了第二衬底和第三衬底这两个衬底。第二衬底和第三衬底可在不同步骤中分离,并且它们中的哪一个首先分离不是固定的。

在本发明的上述工艺中,第一粘合构件和第二粘合构件可用相同材料或不同材料构成,只要这些材料可以用溶剂或光去除。所希望的是,第一粘合构件到剥离层的粘合力大于它到第二衬底的粘合力,并且第二粘合构件到剥离层的粘合力大于它到第三衬底的粘合力。

例如,如果第二粘合构件由光敏粘合剂构成,则第三衬底可以通过在第五步骤中用光照射第二粘合构件来从第二粘合构件上分离。如果第一粘合构件由光敏粘合剂构成,则第二衬底可以通过在第五步骤中用光照射第一粘合构件来从第一粘合构件上分离。因此,若相同的光敏粘合剂被用来做第一粘合构件和第二粘合构件,则第二衬底和第三衬底可在同一步骤中从剥离层上分离。

在使用光敏粘合剂时,第一衬底最后是诸如玻璃衬底或石英衬底的可透射光衬底。

如果没有选择光敏粘合剂,则可以通过用在其表面上形成了AlNXOY膜的塑料膜作为第二衬底或第三衬底来降低粘合构件到衬底的粘合力,从而从剥离层上分离第二衬底或第三衬底。

通过本发明的上述工艺得到夹在第一粘合构件和第二粘合构件之间的剥离层。

当塑料膜被用作第二衬底并且在第一衬底上形成的元件被转到塑料膜上时,换句话说,当利用粘合构件将包括元件的层粘合到膜上并且膜被提起时,该膜可以弯曲但包括元件的层可能会因弯曲而断裂。通过在以下工序中将元件转移到塑料膜上来减小断裂的可能性:在玻璃衬底前利用粘合构件将衬底上形成的元件粘贴到非常硬的第二衬底上。接着利用粘合构件将塑料膜(第三衬底)粘贴到包括元件的层上,从包括元件的层上分离第二衬底。

本说明书中公开的本发明的另一方面涉及一种制造半导体器件的方法,其中包括:在第一衬底上形成要剥离的包括半导体元件的层的第一步骤;利用第一粘合构件将第二衬底粘合到要剥离的层上,从而将这个要剥离的层夹在第一衬底和第二衬底之间的第二步骤;从该要剥离的层上分离第一衬底的第三步骤;利用第二粘合构件将第三衬底粘合到剥离层上,从而将该剥离层夹在第二衬底和第三衬底之间的第四步骤;以及从该剥离层上分离第二衬底以形成用第二粘合构件和第三衬底作支撑体的剥离层的第五步骤。

在上述结构中,制造方法的特征在于:第一衬底和第二衬底的材料具有的刚度大于第三衬底的刚度。在本说明书中,刚度指的是抵抗弯曲或扭转造成的破裂的能力。

在上述结构中,第五步骤是在溶剂中溶解第一粘合构件以去除第一粘合构件并从剥离层上分离第二衬底的步骤,或者通过用光照射光敏粘合剂构成的第一粘合构件以便从剥离层上分离第二衬底的步骤。

通过象这样保持粘合的塑料膜(第三衬底),并不将之剥离,可得到具有由第三衬底和第二粘合构件构成的支撑体的半导体器件。

本说明书中公开的本发明的另一结构是一种半导体器件,其特征在于:塑料衬底和粘合构件构成支撑体,并且在与粘合构件接触的绝缘膜上形成元件。

在上述结构中,元件是薄膜晶体管、具有OLED的发光元件、液晶元件、存储元件、薄膜二极管、硅PIN结的光电转换元件或硅电阻元件。

在上述结构中,半导体器件的特征在于:塑料衬底被粘贴在平面或曲面基底部件上,并且可得到即薄且轻的半导体器件。这种半导体器件的示例包括摄像机、数字照相机、护目镜型的显示器、用于汽车和机器(例如汽车导航系统和速度计)的指示器、个人计算机以及便携式信息终端。

在上述工艺中,第三步骤用于通过剥离方法从要剥离的层上分离第一衬底,其中通过施加机械力并利用两层支撑体的膜应力剥离这两层。对如何分离第一衬底没有特别的限定,并且可以采用通过在剥离层和第一衬底之间提供分离层并用化学制剂(蚀刻剂)去除分离层来将衬底从剥离层分离的方法、或者通过在剥离层和第一衬底之间形成由非晶硅(或多晶硅)构成的分离层并用激光通过第一衬底照射分离层以释放包含在非晶硅中的氢并建立某种间隙来从剥离层上分离第一衬底的方法或者其它一些方法。如果利用激光剥离第一衬底,那么,最好是把热处理温度设定在410℃或更低来形成包含在剥离层中的元件、使得在剥离操作之前不释放氢。

利用两层之间的膜应力的剥离方法是最合乎需要的,这是因为它不会损坏剥离层并且它可以无误地剥离整个表面,而不论剥离层具有小面积或大面积。具体地说,在第一衬底上形成金属层或氮化层的第一材料层,通过溅射形成氧化层的第二材料层,在第二材料层上形成元件,以及施加机械力以便在界面上将第一材料层和第二材料层彼此分离。第一材料层和第二材料层的层叠不受剥离或其它工艺干扰的影响,但可以在第二材料层中的某个点或在界面处用物理方法、一般是施加机械力、比如通过用手拉它而容易并干净地将它们分离。

换句话说,第一材料层和第二材料层之间的粘合强度足够耐受热能但对引起剥离的动能耐受力差,这是因为就在剥离所述层之前在具有张应力的第一材料层和具有压缩应力的第二材料层之间存在应力失真。本发明人发现,剥离现象与膜的内应力之间关系密切因而把利用膜的内应力的剥离工艺称为应力剥离工艺。

当在半导体器件中采用利用第一材料层和第二材料层的上述剥离方法(其特征在于利用塑料衬底和粘合构件作为支撑体并在与粘合构件接触的绝缘膜上形成元件)时,与粘合构件接触的绝缘膜作为第二材料层。绝缘膜最好是通过溅射形成的氧化膜并作为包含惰性气体成分的氧化层。惰性气体成分是从包括He、Ne、Ar、Kr和Xe的组中选择的一种或多种成分。由于包含了惰性气体成分,因而第二材料层可以使半导体器件具有柔性。

此外,本文所用的术语塑料衬底没有特殊的限定,只要它是具有柔柔性的塑料衬底即可;例如,它指的是由聚对苯二甲酸乙二醇酯(PET)、聚醚砜(PES)、聚萘二甲酸乙二酯(PEN)、聚碳酸脂(PC)、尼龙、聚醚酮醚(PEEK)、聚砜(PSF)、聚醚酰亚胺(PEI)、聚芳酯(PAR)、聚对苯二甲酸丁二酯(PBT)或聚酰亚胺构成的衬底。

已进行了了一项试验,以检查在塑料衬底(PC膜)和粘合构件之间形成的氮化硅膜、AIN膜和AINO膜中每种膜的粘合力。将氮化硅膜从塑料衬底上分离,同时它仍粘附在粘合构件上。另一方面,仅将AlN膜和AlNO膜从粘合构件上分离,同时它们仍粘附在塑料衬底上。

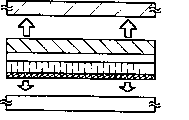

如图16A到16G所示,本发明的另一方面涉及一种制造半导体器件的方法,其中包括:在第一衬底10上形成要剥离的包括半导体元件的层13的第一步骤;利用第一粘合构件14将第二衬底15粘合到要剥离的层13上,从而将这个要剥离的层夹在第一衬底和第二衬底之间的第二步骤;从要剥离的层13上分离第一衬底10的第三步骤;利用第二粘合构件16将其中形成了保护模18的第三衬底17粘合到剥离层上,从而将该剥离层夹在第二衬底和第三衬底之间的第四步骤;以及从该剥离层上分离第二衬底并从第二粘合构件上分离第三衬底以形成用第二粘合构件16和保护模18作支撑体的剥离层的第五步骤。

在上述结构中,制造方法的特征在于:保护模是氮化硅膜或氧氮化硅膜。通过形成保护膜,可以有效地阻止来自外界的湿气和杂质以避免污染。

附图说明

附图中:

图1A到1G是显示实施模式1的工艺图;

图2A到2G是显示实施模式2的工艺图;

图3A到3G是显示实施模式3的工艺图;

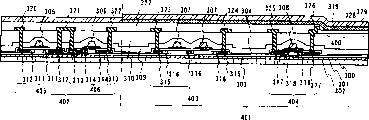

图4是具有元件的第一衬底的截面图;

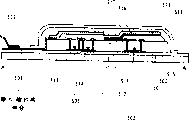

图5是具有OLED的发光器件的截面图;

图6A和6B分别是具有OLED的发光器件的顶视图及其截面图;

图7是具有OLED的发光器件的截面图;

图8是有源矩阵液晶显示器件的截面图;

图9是显示剥离之前n沟道TFT的V-I特性的曲线图;

图10是显示剥离之前p沟道TFT的V-I特性的曲线图;

图11是显示剥离之后n沟道TFT的V-I特性的曲线图;

图12是显示剥离之前p沟道TFT的V-I特性的曲线图;

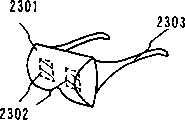

图13A到13F是显示电子设备的示例的简图;

图14是显示电子设备的示例的简图;

图15A到15C是显示电子设备的示例的简图;

图16A到16G是显示本发明的工艺图示例;

图17是示出显示板的外形图的照片;

图18是示出发光的显示板的照片。

具体实施方式

下面将对本发明的实施模式进行描述。

[实施模式1]

以下是对利用本发明的典型剥离过程以及半导体器件制造方法的简述。描述将参考图1A到1G。

在图1A中,标号10表示第一衬底,11表示氮化层或金属层的第一材料层,12表示氧化层的第二材料层,以及13表示要剥离的层。

图1A中的第一衬底10可以是玻璃衬底、石英衬底、陶瓷衬底等。也可以使用一般为硅衬底的半导体衬底或一般为不锈钢衬底的金属衬底。

首先,在衬底10上形成第一材料层11,如图1A所示。第一材料层11一旦形成就可能具有压缩应力或张应力。但是,重要的是将这样的材料用于第一材料层11:它不受由用于形成要剥离的层的热处理或激光照射引起的剥离或其它干扰的影响、并且在要剥离的层形成之后该层具有1到1×1010dyne/cm2(达因/平方厘米)的张应力。其典型示例是从由W、WN、TiN和TiW组成的组中选择的成分的单层、或者主要包含上述成分的合金材料或化合物材料的单层、或者上述成分的叠层结构。通过溅射形成第一材料层11。

接下来,在第一材料层11上形成第二材料层12。重要的是将这样的材料用于第二材料层12:它不受由用来形成要剥离的层的热处理或激光照射引起的剥离或其它干扰的影响、并且在要剥离的层形成之后该层具有1到1×1010dyne/cm2的张应力。第二材料层12的典型示例是氧化硅、氮氧化硅和金属氧化物的单层或叠层结构。可以通过溅射形成第二材料层12。在通过溅射形成第二材料层12时,一般为氩气的惰性气体被引进到反应室中、使得在第二材料层12中包含极少量的惰性成分。

第一材料层11和第二材料层12被分别设置为具有范围在1nm(纳米)和100nm之间的适当厚度,以便调整第一材料层11的内应力和第二材料层12的内应力。

图1A到1G显示了一个示例,其中形成的第一材料层11与衬底10接触以便简化工艺。但是,可以在衬底10和第一材料层11之间形成用作缓冲层的绝缘层或金属层,以便改善第一材料层11到衬底10的粘合力。

接着,在第二材料层12上形成要剥离的层13(图1A)。要剥离的层13是包含各种元件(薄膜晶体管、具有OLED的发光元件、液晶元件、存储元件、薄膜二极管、硅的PIN结的光电转换元件、硅电阻元件)的层。当所述元件是具有液晶的元件时,要剥离的层13包括对面的衬底。要剥离的层13可以通过在第一衬底10能够耐受的温度下的热处理来形成。在本发明中,并非通过用于形成要剥离的层13的热处理来剥离薄膜,尽管第二材料层12的内应力不同于第一材料层11的内应力。

下述工艺用于部分降低第一材料层11和第二材料层12之间的粘合力。用于部分降低粘合力的处理是激光照射,其中用光沿着要剥离区域的周边部分照射第二材料层或第一材料层,或沿着要剥离区域的周边从外部施加的局部压力、以损坏第二材料层内部的一部分或界面的一部分。具体地说,用金刚石笔等垂直压下硬针、并且边移动所述层边施加负荷。最好使用划线器装置并且将下压量设在0.1到2mm,以便边移动所述层边施加压力。以这种方式在剥离之前提供促进剥离现象的部分、即引发机制是重要的。由于选择性(部分地)降低粘合力的预处理,避免了剥离失败并且提高了产量。

接下来,利用第一粘合构件14将第二衬底15粘合到要剥离的层13(图1B)。反应固化粘合剂、热固化粘合剂、诸如UV固化粘合剂的光固化粘合剂、厌氧粘合剂和其它各种类型的固化粘合剂可以被用作第一粘合构件14。这些粘合剂可溶于溶剂或者可以是光敏的且在用光照射时粘合力降低。这些粘合剂可具有任何成分并且可以是例如基于环氧树脂的、基于丙烯酸酯的或基于硅酮的。例如通过涂敷将粘合剂制成粘合构件。在后续步骤中去除第一粘合构件。这里,将可溶于溶剂的粘合剂材料选作第一粘合构件。

第二衬底15可以是玻璃衬底、石英衬底、陶瓷衬底、塑料衬底等。也可以使用一般为硅衬底的半导体衬底或一般为不锈钢衬底的金属衬底。偶尔在光敏粘合构件被用作第一粘合构件或第二粘合构件的情况下,作为第一衬底和第二衬底之一,最好使用具有透光的衬底。

接下来,将其上形成了第一材料层11的第一衬底10按图1C中箭头所示的方向、用物理方法从部分降低了粘合力的区域的那一侧开始(图1C)撕开。由于第二材料层12具有压缩应力而第一材料层11具有张应力,因此可用相对小的力(如用手、通过喷嘴喷射的气压、超声波等)撕开第一衬底。

在第一材料层12上形成的要剥离的层13可以用这种方式从第一衬底10上分离。图1D中显示了剥离后的状态。

随后,利用由不同于第一粘合构件14的材料构成的第二粘合构件16将第三衬底17粘合到第二材料层12(和剥离层13)。重要的是第二粘合构件16到第二材料层12(和剥离层13)的粘合力大于它到第三衬底17的粘合力。

反应固化粘合剂、热固化粘合剂、诸如UV固化粘合剂的光固化粘合剂、厌氧粘合剂和其它各种类型的固化粘合剂可以被用作第二粘合构件16。这些粘合剂可溶于溶剂或者可以是光敏的因而粘合力在用光照射时降低。这些粘合剂可以具有任何成分并且可以是基于环氧树脂的、基于丙烯酸酯的或基于硅酮的。例如通过涂敷将粘合剂制成粘合构件。第二粘合构件在后续步骤中成为剥离层的支撑体。这里,UV固化粘合剂被用作第二粘合构件16。

第三衬底17可以是玻璃衬底、石英衬底、陶瓷衬底、塑料衬底等。也可以使用一般为硅衬底的半导体衬底或一般为不锈钢衬底的金属衬底。这里,为了降低第二粘合材料到第三衬底的粘合力,在其表面上形成了AlNXOY膜的塑料膜被用作第三衬底17。

利用例如氮化铝(AlN)靶在通过将氩气、氮气和氧气混合得到的气氛中进行溅射在塑料膜上形成AlNXOY膜。AlNXOY膜包括几个或更多氮气压百分比就足够了,最好为2.5到47.5氮气压百分比(atm%)。可以通过调整溅射条件来按需调整氮浓度(衬底温度、原料气的类型和流速、成膜压力等)。

接下来,将所述各层浸入溶剂中以便分离第二衬底15和第三衬底17(图1F)。第一粘合构件易于被去除,因为它是由可溶于溶剂中的粘合剂材料构成的,从而将第二衬底15从剥离层13上分离。另一方面,溶剂渗透第三衬底17和第二粘合构件16之间的界面并减弱了界面处的粘合力,从而将第三衬底17从第二材料层12上分离。尽管在这里所示的示例中在同一步骤中分离第二衬底15和第三衬底17,但并不存在特定限制。这些衬底可以在不同步骤中分离并且首先分离它们中的哪一个并不固定。

这样形成剥离层13中包括的元件、使得其输入/输出端暴露在剥离层的最上层(即最靠近第二衬底侧的层)。因此,需要在分离第二衬底的步骤完成之后再去除剥离层上的第一粘合构件,从而暴露输入/输出端。

通过上述步骤制造具有剥离层13的半导体器件,其中第二粘合构件16被用作支撑体(图1g)。这样得到的半导体器件即薄且轻,并且具有柔性,因为支撑体只由第二粘合构件16构成。

在这里示意的示例中,通过上述步骤来完成半导体器件。上述步骤可被用于部分地完成半导体器件。例如,元件形成步骤可被添加到上述步骤中、以便在上述步骤之后形成包括TFT的电路的剥离层进而可在元件形成步骤中利用所获得的用第二粘合构件作支撑体的剥离层,以完成各种不同类型的半导体器件,一般为具有OLED的发光器件或液晶显示器件。

例如,可以通过以下步骤来制造有源矩阵发光器件:配置像素电极以形成矩阵图案;通过上述步骤形成具有连接到像素电极的TFT的第二粘合构件;以及形成用像素电极作负极或正极的OLED。这样得到的发光器件即薄且轻,因为支撑体仅由第二粘合构件构成。

还可能制造具有OLED的无源发光器件。

同样,可以通过以下步骤来制造有源矩阵液晶显示器:配置像素电极以形成矩阵图案;通过上述步骤形成具有连接到像素电极的TFT的第二粘合构件;之后是相对衬底粘贴步骤和液晶注入步骤。具体地说,密封构件等被用于将相对衬底粘贴到具有连接到像素电极的TFT的粘合构件,同时用诸如垫片的间隙保持构件在相对衬底和粘合构件支撑体之间保持一定的距离。接着在相对衬底和像素电极之间装入液晶材料以完成液晶显示器件。这样得到的液晶显示器件即薄且轻,因为支撑体仅由第二粘合构件和相对衬底构成。

[实施模式2]

实施模式1显示了其中第二粘合构件单独用作支撑体的示例。在本实施模式中,显示了用第一粘合构件和第二粘合构件作支撑体的示例。图2A到图2E基本与图1A到1E相同。因此,这里将省略细节描述并且将只对实施模式1和实施模式2之间的不同之处进行描述。

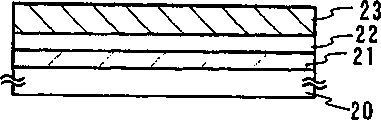

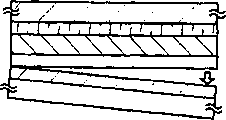

在图2A到2G中,标号20表示第一衬底,21表示是氮化层或金属层的第二材料层,22表示是氧化层的第二材料层,23表示要剥离的层,24表示第二粘合构件,25表示第二衬底,26表示第二粘合构件以及27表示第三衬底。

首先,根据第一实施模式1,以相同的程序得到图2E的状态。

这里,反应固化粘合剂、热固化粘合剂、诸如UV固化粘合剂的光固化粘合剂、厌氧粘合剂和其它各种类型的固化粘合剂可以被用作第一粘合构件24。这些粘合剂可溶于溶剂或者可以是光敏的因而在用光照射时粘合力降低。这些粘合剂可以具有任何成分并且可以是基于环氧树脂的、基于丙烯酸酯的或基于硅酮的。例如通过涂敷而将粘合剂制成粘合构件。在后续步骤中第一粘合构件成为支撑体。这里,用紫外线照射时粘合力会降低的热固化粘合剂被用作第一粘合构件。重要的是第一粘合构件24到剥离层23的粘合力大于它到第二衬底25的粘合力。

为了降低第一粘合构件到第二衬底的粘合力,可将表面上形成了AlNXOY膜的塑料膜用作第二衬底。

第二粘合构件26的材料可以与第一粘合构件24的材料相同。这里,粘合力在用紫外线照射时会降低的热固化粘合剂被用作第二粘合构件。第二粘合构件在后续步骤中也用作剥离层的支撑体。重要的是第二粘合构件26到第二材料层22(和剥离层23)的粘合力大于它到第三衬底27的粘合力。

为了降低第二粘合构件到第三衬底的粘合力,可将表面上形成了AlNXOY膜的塑料膜用作第三衬底。

通过进行实施模式1的过程得到图2E的状态。接着用紫外线照射粘合构件,以降低第一粘合构件24到第二衬底25的粘合力以及第二粘合构件26到第三衬底27的粘合力,从而将第二衬底和第三衬底分离(图2F)。尽管在这里所示的示例中在同一步骤中分离第二衬底25和第三衬底27,但并不存在特定限制。这些衬底可以在不同步骤中分离并且首先分离它们中的哪一个并不固定。本实施模式还可以与实施模式1进行组合。

尽管在这里所示的示例中使用了通过紫外线照射降低粘合力的热固化粘合剂,但也可以使用其它粘合剂材料。例如,UV固化粘合剂可被用作第一粘合构件和第二粘合构件。在这种情况下,在其表面上形成了AlNXOY膜的塑料膜被用作第二衬底并通过由UV固化粘合剂构成的第一粘合构件粘合,在其表面上形成了AlNXOY膜的塑料膜被用作第三衬底并通过由UV固化粘合剂构成的第二粘合构件粘合。之后,这些层被浸入溶剂中并且溶剂渗透到第三衬底和第二粘合构件之间的界面,从而将第二材料层与第三衬底分离。类似地将第一粘合构件与第二衬底分离。

这样形成包括在剥离层23中的元件、使得其输入/输出端暴露在剥离层的最上层(即最靠近第二衬底侧的层)。因此,需要选择性地在分离第二衬底的步骤之后去除覆盖输入/输出端部分的第一粘合构件,从而暴露输入/输出端部分。

通过图2G中显示的上述步骤制造了具有剥离层23的半导体器件,其中第一粘合构件24和第二粘合构件26用作支撑体。注意,剥离层23被夹在第一粘合构件24和第二粘合构件26之间。这样得到的半导体器件既薄且轻,并且具有柔性,因为支撑体仅由第一粘合构件24和第二粘合构件26构成。

在这里显示的示例中,通过上述步骤完成半导体器件。上述步骤可被用于部分地完成半导体器件。例如,可以将元件形成步骤添加到上述步骤中,以便按照上述步骤形成包括包含TFT的电路的剥离层,并且这样形成的将第一粘合构件和第二粘合构件作为支撑体的剥离层可被用于元件形成步骤中,以完成各种不同类型的半导体器件,一般为具有OLED的发光器件或液晶显示器件。

本实施模式可以与实施模式1自由组合。

[实施模式3]

实施模式1显示了其中第二粘合构件单独用作支撑体的示例。在本实施模式中,显示了用第二粘合构件和第三衬底作支撑体的示例。图3A到3E基本与图1A到1E相同。所以这里将省略细节描述,并且将只对实施模式1和实施模式3之间的不同之处进行描述。

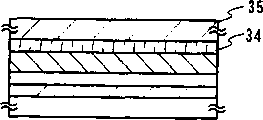

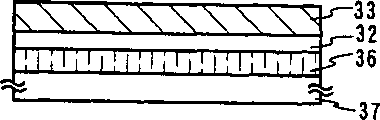

在图3A到3G中,标号30表示第一衬底,31表示是氮化层或金属层的第一材料层,32表示是氧化层的第二材料层,33表示要剥离的层,34表示第一粘合构件,35表示第二衬底,36表示第二粘合构件以及37表示第三衬底。

首先,根据实施模式1,以相同的过程得到图3E的状态。

第一衬底30可以是玻璃衬底、石英衬底、陶瓷衬底等。还可以使用一般为硅衬底的半导体衬底或一般为不锈钢衬底的金属衬底。这里使用厚度为0.7mm的玻璃衬底(#1737)。

这里,把比第一衬底30更厚和更高硬度的石英衬底(厚度1.1mm)用作第二衬底35。如果用塑料膜作第二衬底,则当在第一衬底上形成的元件被转移到塑料膜上时,换句话说,当利用第一粘合构件34将剥离层33粘合到该膜上并且该膜被提起时,担心膜会弯曲并且剥离层33可能因为弯曲导致断裂。因此,通过以下工序降低断裂的可能性:利用第一粘合构件34将在第一衬底30上形成的剥离层33粘贴到非常硬的第二衬底35上;剥离第一衬底30;利用第二粘合构件36将塑料膜(第三衬底37)粘贴到包括元件的层上;然后分离第二衬底35。

这里的第三衬底37是塑料膜。

这里,挑选溶于溶剂的粘合剂材料用作第一粘合构件34。

这里用作第二粘合构件36的材料对第三衬底和剥离层都是高粘合力的。

遵照实施模式1的程序得到图3E的状态。然后,将这些层浸入溶剂中以单独分离第二衬底35(图3F)。由溶于溶剂的粘合剂材料构成的第一粘合构件易于被去除,从而从剥离层33上分离第二衬底35。

这样形成包含在剥离层33中的元件、使得其输入/输出端暴露在剥离层的最上层(即最靠近第二衬底侧的层)。因此,需要在分离第二衬底的步骤完成之后去除剥离层表面上的第一粘合构件,以便暴露输入/输出端部分。

在这里显示的示例中,第一粘合构件34由一种溶于溶剂的粘合剂构成,并且将其浸入溶剂中以分离第二衬底。但是,不存在特殊限制,例如,可以通过用紫外线照射由热固化粘合剂(在紫外线照射下其粘合力降低)构成的第一粘合构件来分离第二衬底,如实施模式2所示。

通过如图3G中显示的上述步骤制造了具有剥离层33的半导体器件,其中第二粘合构件36和第三衬底37用作支撑体。作为第二材料层的氧化层被插入在第二粘合构件36和剥离层33之间。这样得到的半导体器件整体上是柔性的,因为通过溅射形成第二材料层32并且第二材料层32中包括极少量的惰性气体成分。

在这里显示的示例中,通过上述步骤完成半导体器件。上述步骤可被用于部分地完成半导体器件。例如,可以将元件形成步骤添加到上述步骤中,从而按照上述步骤形成包括包含TFT的电路的剥离层,并且这样获得的将第二粘合构件和第三衬底用作支撑体的剥离层可被用于元件形成步骤中,以完成各种不同类型的半导体器件,一般为具有OLED的发光器件或液晶显示器件。

本实施模式可以与实施模式1或实施模式2自由组合。

将通过以下实施例对上述结构的本发明进行更详细的描述。

[实施例1]

这里,将对制造具有OLED的发光器件的方法进行详细描述,其中同时在同一衬底上形成像素部分(n沟道TFT和p沟道TFT)和在像素部件的周围配置的驱动电路的TFT(n沟道TFT和p沟道TFT)(图4)。

首先,通过等离子CVD在厚度为0.7mm的耐热玻璃衬底(第一衬底101)上形成厚度为100nm的氧氮化硅膜(未示出)。氧氮化硅膜用于保护衬底不受后续的干蚀刻影响并用于防止蚀刻室的污染,并且不是特别必需的。

尽管在本实施例中将玻璃衬底用作第一衬底101,但不存在特定限制并且它可以是石英衬底、半导体衬底、陶瓷衬底或金属衬底。

接着,通过溅射在氧氮化硅膜上形成厚度为50nm的钨膜,作为第一材料层102。通过溅射形成的钨膜在衬底周边的厚度波动。因此,通过单独形成用于衬底周边的干蚀刻的抗蚀剂来形成钨膜图案。尽管这里形成了图案,但它并非特别必须的。第一材料层102并非限定于钨膜,也可使用其它材料,例如氮化钨或氮化钛。第一材料层102的厚度可以按需设置在10到200nm的范围内。

在钨膜上通过溅射形成厚度为200nm的氧化硅膜,作为第二材料层103。尽管这里使用通过溅射形成的氧化硅膜,但也可以使用其它材料,例如氧化物,作为替代。第二材料层103的厚度可以按需设置在50到400nm的范围内。象这样在第一衬底上形成第一材料层102(钨膜)和第二材料层103(氧化硅膜),在后续步骤中在第二材料层上形成元件,然后施加机械力,以便在界面上将第一材料层和第二材料层彼此分离。最好在形成第二材料层103期间通过溅射形成诸如氩气的惰性气体流,以便在第二材料层103中包含极少量的惰性气体成分。

接着,通过在400℃温度下的等离子CVD利用SiH4、NH3和N2O作原料气在氧化硅膜上形成氧氮化硅膜(氧氮化硅膜的成分比例为:Si=32%,O=27%,N=24%,H=17%),作为基底绝缘膜的下层。氧氮化硅膜的厚度为50nm(最好为10到200nm)。膜表面用臭氧水清洗,然后用稀释的氟酸(稀释到1/100)去除表面上的氧化膜。接下来,通过在400℃温度下的等离子CVD利用SiH4和N2O作原料气形成氧氮化硅膜(氧氮化硅膜的成分比例为:Si=32%,O=59%,N=7%,H=2%),作为基底绝缘膜的上层。氧氮化硅膜的厚度为100nm(最好为50到200nm)并且覆盖在下层之上,以形成层叠结构。没有将所述层叠结构暴露于空气之中,通过在300℃温度下的等离子CVD利用SiH4作原料气在所述层叠结构上形成具有非晶态结构的半导体膜(这里为非晶硅膜)。半导体膜的厚度为54nm(最好为25到80nm)。

本实施例中的基底绝缘膜104具有两层结构。但是,基底绝缘膜可以是主要包含硅的单层或多于两层的绝缘膜。半导体膜的材料没有限制,但最好是通过已知方法(溅射、LPCVD、等离子CVD等)由硅或硅锗合金(SiXGe1-X(X=0.0001到0.02))构成的半导体膜。所用的等离子CVD装置可以是逐晶片进行处理的装置或成批处理的装置。可在同一室中连续形成基底绝缘膜和半导体膜,以避免与空气接触。

清洗具有非晶态结构的半导体膜的表面,然后利用臭氧水在该表面上形成大约2nm厚的非常薄的氧化膜。接着,用极少量的杂质成分(硼或磷)对半导体膜掺杂,以控制TFT的阈值。这里,通过离子掺杂的方法用硼对非晶硅膜进行掺杂,其中在没有质量分离的情况下利用等离子激发乙硼烷(B2H6)。掺杂条件包括将加速电压设置到15kV,通过用氢将乙硼烷稀释到1%得到30sccm的气体流速,而用量为2×1012/cm2。

接下来,利用旋涂器涂敷包含按重量计为10ppm的镍的乙酸镍溶剂。镍可通过溅射而不是涂敷喷涂到整个表面。

半导体膜经过热处理而结晶并得到具有晶体结构的半导体膜。在电炉或利用强光照射来实现热处理。当采用电炉中的热处理时,温度被设置为500到650℃,并且处理持续4到24小时。这里,在热处理去氢(500℃下持续1小时)之后通过热处理进行晶化(550℃下持续4小时)得到具有晶体结构的硅膜。尽管这里利用电炉通过热处理晶化半导体膜,但也可以通过能够在短时间内实现晶化的退火装置进行晶化。本实施例采用了一种晶化技术,其中镍被用作加速硅的晶化的金属成分。但也可以采用其它已知的诸如固相生长和激光晶化的晶化技术。

通过稀释的氟酸等去除具有晶体结构的硅膜表面上的氧化膜。然后,为了提高晶化速度并修正晶粒中存留的缺陷,在空气中或氧气环境中用激光(波长为308nm的XeCl)照射硅膜。激光可以是波长为400nm或更短的准分子激光,或者可以是YAG激光器的二次谐波或三次谐波。采用具有重复频率为10到1000Hz的脉冲激光。由光学系统聚集激光,以便具有100到400mJ/cm2的能量密度,并以90%到95%的重叠比率扫描硅膜表面。这里,在空气中用重复频率为30Hz、能量密度为470mJ/cm2的激光照射所述膜。由于是在空气或氧气环境中进行激光照射的,因此在表面上形成了氧化膜。这里显示的示例中使用了脉冲激光器,但也可以采用连续波激光器。最好采用连续波固态激光器以及基波的二次到四次谐波,以便在对非晶体半导体膜进行晶化时得到大粒度晶体。一般采用Nd∶YVO4激光器(基波:1064nm)的二次谐波(532nm)和三次谐波(355nm)。当利用连续波激光器时,从10W功率连续波YVO4激光器发出的激光被非线性光学部件转换成谐波。或者,通过将YVO4晶体和非线性光学部件设置在谐振器中得到谐波。谐波最好由光学系统成形为照射表面上的长方形或椭圆形的激光,然后对照射对象进行照射。这时所需的能量密度大约为0.01到100MW/cm2。(最好为0.1到10MW/cm2)。照射期间,半导体膜以10到2000cm/s的速度相对于激光移动。

用稀释的氟酸去除通过激光照射形成的氧化膜,然后用臭氧水处理该表面120秒,以形成总厚度为1到5nm的氧化膜作为阻挡层。这里利用臭氧水形成阻挡层,但也可以通过在氧气环境中通过紫外线照射氧化具有晶体结构的半导体膜的表面来形成,或通过氧等离子体处理氧化具有晶体结构的半导体膜的表面来形成,或通过利用等离子CVD、溅射或蒸发形成大约1到10nm厚的氧化膜。在本说明书中,阻挡层指的是这样的层:它具有允许金属成分在吸气步骤中通过的质量和厚度并在去除作为吸气点的层的步骤中作为蚀刻终止层。

接下来,通过溅射在阻挡层上形成包含氩的非晶硅膜,用作吸气点,非晶硅膜的厚度为50到400nm,这里为150nm。这里形成非晶硅膜的条件包括将成膜压力设置为0.3Pa,气体(Ar)流速为50sccm,成膜功率为3kW,以及衬底温度为150℃。在上述条件下形成的非晶硅膜中所包含的氩的原子浓度为3×1020到6×1020/cm3并且其中的氧的原子浓度为1×1019到3×1019/cm3。之后,在550℃电炉中进行4小时的热处理用于吸气,以减少具有晶体结构的半导体膜中的镍浓度。可以使用灯退火装置代替电炉。

利用阻挡层作为蚀刻终止层,选择性地去除吸气点、即包含氩的非晶硅膜。然后,通过稀释的氟酸选择性地去除阻挡层。镍在吸气期间倾向于向具有高氧浓度的区域移动,因而需要在吸气后去除成为氧化膜的阻挡层。

接下来,利用臭氧水在得到的包含晶体结构的硅膜(也被称为多晶硅膜)的表面上形成薄氧化层。然后形成抗蚀剂掩膜并且对硅膜进行蚀刻以形成彼此分离的岛状半导体层并具有所需形状。形成半导体层之后去除抗蚀剂掩膜。

用包含氟酸的蚀刻剂去除氧化膜,并且同时清洗硅膜表面。接着形成主要包含硅的绝缘膜用作栅绝缘膜105。这里的栅绝缘膜是通过等离子CVD形成的厚度为115nm的氧氮化硅膜(成分比例:Si=32%,O=59%,N=7%,H=2%)。

接下来,在栅绝缘膜上形成厚度为20到100nm的第一导电膜和厚度为100到400nm的第二导电膜的叠层结构。在本实施例中,在栅绝缘膜105上形成厚度为50nm的氮化钽膜然后在其上覆盖厚度为370nm的钨膜。按下述程序形成导电膜图案,以形成栅极和导线。

第一导电膜和第二导电膜的导电材料是选自由Ta、W、Ti、Mo、Al和Cu、或者主要包含上述元素的合金或化合物组成的组中选择的成分。第一导电膜和第二导电膜可以是半导体膜,一般为多晶硅膜,其中用磷或其它杂质元素进行掺杂或者可以是Ag-Pd-Cu合金膜。本发明并不限于两层导电膜。例如,可以采用以下列顺序层叠的包括50nm厚的钨膜、500nm厚的铝硅合金(Al-Si)膜和30nm厚的氮化钛膜的三层结构。当采用三层结构时,可以用氮化钨代替第一导电膜的钨,用铝钛合金(Al-Ti)膜代替第二导电膜的铝硅合金(Al-Si)膜,以及用钛膜代替第三导电膜的氮化钛膜。或者,可以使用单层导电膜。

最好将ICP(感应耦合等离子体)蚀刻用于第一导电膜和第二导电膜的蚀刻(第一蚀刻处理和第二蚀刻处理)。通过利用ICP蚀刻并调整蚀刻条件(加到线圈电极的电功率量、加到衬底侧电极的电功率量、衬底侧电极的温度等),可以按需蚀刻并使膜成锥形。在形成了抗蚀剂掩膜之后进行第一蚀刻处理。第一蚀刻条件包括在1Pa(帕斯卡)压强下对线圈电极施加700W的RF(13.56MHz)功率,采用CF4、Cl2和O2作为蚀刻气体,以及设置其中的气体流速比例为25∶25∶10(sccm)。衬底侧(样本阶段)还接收150W(13.56MHz)的RF功率,以提供基本上为负的自偏压。衬底侧电极的面积(大小)为12.5cm×12.5cm,并且线圈电极是直径25cm的盘(这里是在其上设置线圈的石英盘)。在这些第一蚀刻条件下蚀刻W膜,从而在边缘周围形成锥形。之后,从第一蚀刻条件切换到第二蚀刻条件,并不去除抗蚀剂掩膜。第二蚀刻条件包括采用CF4和Cl2作为蚀刻气体,设置其中的气体流速比例为30∶30(sccm),并在1Pa压强下对线圈电极施加500W的RF(13.56MHz)功率,以产生等离子体进行约30分钟的蚀刻。衬底侧(样本阶段)还接收20W(13.56MHz)的RF功率,以提供基本上为负的自偏压。在使用CF4和Cl2的混合的第二蚀刻条件下,W膜和TaN膜被蚀刻到几乎相同的程度。所述第一蚀刻条件和第二蚀刻条件构成第一蚀刻处理。

接下来在不去除抗蚀剂掩膜的情况下进行第一掺杂处理。第一掺杂处理采用离子掺杂或离子注入。一般来说,磷(P)或砷(As)被用作提供n型电导性的杂质元素。这里使用离子掺杂,把通过利用氢将磷化氢(PH3)稀释到5%而得到的气体的流速设定为40sccm,把用量设定为2×1015原子/cm2,而把加速电压设定为80Kev。在这种情况下,第一导电层用作对抗提供n型电导性的杂质元素的掩膜并且以自定位的方式形成第一杂质区。第一杂质区用提供n型电导性的杂质元素掺杂,掺杂浓度为1×1020到1×1021/cm3。这里与第一杂质区具有相同浓度范围的区域被称为n+区。

接着是第二蚀刻处理,其中抗蚀剂掩膜固定不动。第三蚀刻条件包括利用CF4和Cl2作蚀刻气体,设置其中的气体流速比例为30∶30(sccm),并在1Pa压强下对线圈电极施加500W的RF(13.56MHz)功率,以产生等离子体进行约60分钟的蚀刻。衬底侧(样本阶段)还接收20W(13.56MHz)的RF功率,以提供基本为负的自偏压。之后,在不去除抗蚀剂掩膜的情况下从第三蚀刻条件切换到第四蚀刻条件。第四蚀刻条件包括采用CF4、Cl2和O2作为蚀刻气体,设置其中的气体流速比例为20∶20∶20(sccm),并在1Pa压强下对线圈电极施加500W的RF(13.56MHz)功率,以产生等离子体进行约20分钟的蚀刻。衬底侧(样本阶段)还接收20W(13.56MHz)的RF功率,以提供基本为负的自偏压。第三蚀刻条件和第四蚀刻条件构成第二蚀刻处理。在这个阶段,形成具有作为下层的第一导电层和作为上层的第二导电层的栅极106到109和导线。

接下来,去除抗蚀剂掩膜以便进行第二掺杂处理。第二掺杂处理采用离子掺杂或离子注入。这里使用离子掺杂,把通过利用氢将磷化氢(PH3)稀释到5%而得到的气体的流速设定为30sccm,把用量设定为1.5×1014原子/cm2,而加速电压设定为90KeV。在这种情况下,第一导电层和第二导电层用作对抗提供n型电导性的杂质元素的掩膜并且以自定位方式形成第二杂质区。第二杂质区用提供n型电导性的杂质元素掺杂,掺杂浓度为1×1016到1×1017/cm3。这里与第二杂质区具有相同浓度范围的区域被称为n-区。

在本实施例中,首先进行第一蚀刻处理,然后依次是第一掺杂处理、第二蚀刻处理和第二掺杂处理。但是,显然处理顺序并不限于此。例如,第一蚀刻处理后面可以依次进行第二蚀刻处理、第二掺杂处理和第一掺杂处理,或者第一蚀刻处理后面可以依次进行第二蚀刻处理、第一掺杂处理和第二掺杂处理。

接下来,形成抗蚀剂掩膜以便进行第三掺杂处理。抗蚀剂掩膜覆盖形成n沟道TFT的半导体层。通过第三掺杂处理,在半导体层中形成用提供n型电导性的杂质元素掺杂的第三杂质区,以形成p沟道TFT和半导体层,从而在像素部分和驱动电路中形成电容存储器。第三杂质区中提供P型电导性的杂质元素的浓度为1×1018到1×1020/cm3。第三杂质区已经在以上步骤中用磷(P)掺杂了,但用提供P型电导性的杂质元素进行掺杂,掺杂浓度足够大以得到P型电导性。这里,与第三杂质区具有相同浓度范围的区域被称为p-区。

在不去除上述抗蚀剂掩膜的情况下进行第三掺杂处理。通过第三掺杂处理,在半导体层中形成用提供P型电导性的杂质元素掺杂的第四杂质区,以形成P沟道TFT和半导体层,从而在像素部分和驱动电路中形成电容存储器。第四杂质区中提供P型电导性的杂质元素的浓度为1×1020到1×1021/cm3。第四杂质区已经在以上步骤中用磷(P)掺杂了,但用提供P型电导性的杂质元素进行掺杂,掺杂浓度是磷浓度的1.5到3倍,以得到P型电导性。这里,与第四杂质区具有相同浓度范围的区域称为p+区。

通过上述步骤在各个半导体层中形成具有n型或P型电导性的杂质区。在像素部分和驱动电路中,在形成p沟道TFT的半导体层中形成p-区112和p+区113,而在形成n沟道TFT的半导体层中形成n-区111和n+区110。

下一步骤是用于掺杂半导体层的杂质元素的活化处理。活化步骤采用:快速热退火(RTA),其中利用灯光源、来自背面的YAG激光器或准分子激光器的照射;或者利用炉子的热处理;或者这些方法的组合。这里为进行活化处理而使用电炉并且在550℃下氮气气氛中进行4小时的热处理。

接下来,形成几乎覆盖整个表面的第一中间层绝缘膜114。本实施例中的第一中间层绝缘膜是通过等离子CVD形成的50nm厚的氧化硅膜。第一中间层绝缘膜并不限于氧化硅膜,并且也可以使用单层或其中包括硅的绝缘膜的层叠结构。

在本实施例显示的示例中,在上述活化之后形成第一中间层绝缘膜。但是也可以在活化之前形成绝缘膜。

在第一中间层绝缘膜上形成厚度为100nm包含氢的氮化硅膜,作为第二中间层绝缘膜(未示出)。之后,对半导体层进行热处理(300到550℃下持续1到12小时),以便将半导体层氢化。这个步骤是为了利用第二中间层绝缘膜中包含的氢来动摇半导体层中的粘合。对半导体层进行氢化,与氧化硅膜的第一中间层绝缘膜的存在无关。其它可采用的氢化方法包括等离子氢化(利用由等离子体激活的氢)。

接下来,在由有机绝缘材料构成的第二中间层绝缘膜上形成第三中间层绝缘膜115。在本实施例中,形成厚度为1.05μm的丙烯酸树脂膜。然后形成到达用作栅电极或栅极导线的导电层的接触孔以及到达杂质区的接触孔。在本实施例中,连续进行几次蚀刻处理。同时,在本实施例中,第二中间层绝缘膜被用作蚀刻第三中间层绝缘膜的蚀刻终止层,然后第一中间层绝缘膜被用作蚀刻第二中间层绝缘膜的蚀刻终止层,然后蚀刻第一中间层绝缘膜。

之后,用Al、Ti、Mo或W形成电极116到122,具体地说,形成源极导线、电源线、引出电极、连接电极等。这里通过将Ti膜(100nm厚)、包含硅的Al膜(350nm厚)和另一Ti膜(50nm厚)的层叠结构构成图案来得到所述电极和导线。进而按需形成源电极、源极导线、连接电极、引出电极、电源线等。在栅极导线的末端形成与被中间层绝缘膜覆盖的栅极导线接触的引出电极,并且其它导线在其末端也具有输入/输出端部分,这些输入/输出端部分具有多个用于连接到外部电路和外部电源的电极。

以上述方式形成具有CMOS电路的驱动电路202和具有多个像素的像素部分201,其中驱动电路202中n沟道TFT 205和p沟道TFT206以互补方式组合,而像素部分的每个像素具有n沟道TFT 203和p沟道TFT 204。

在驱动电路中,n沟道TFT(第一n沟道TFT)的半导体层205具有:沟道形成区;第二杂质区(n-区)111,它部分地重叠于形成栅极的导电层,其中绝缘膜夹在所述区和所述层之间;以及第一杂质区(n+区)110,所述第一杂质区之一用作源区,而另一个第一杂质区用作漏区。

在驱动电路中,p沟道TFT(第一p沟道TFT)的半导体层206具有:沟道形成区;第三杂质区(p-区)112,它部分地重叠于形成栅极的导电层,其中绝缘膜夹在所述区和所述层之间;以及第四杂质区(p+区)113,所述第四杂质区之一用作源区,而另一个第四杂质区用作漏区。

这些TFT的组合(第一n沟道TFT和第一p沟道TFT)被适当地用于形成移位寄存器电路,缓存电路、电平移动电路、锁存电路,以构成驱动电路。

在像素部分201,即其中把大量像素排列成矩阵的整个区,每个像素具有多个n沟道TFT或p沟道TFT。这些TFT可以大致被分为电连接到后续步骤中形成的OLED的TFT和其它TFT。电连接到后续步骤中形成的OLED的TFT(也被称为电流控制TFT)控制流入OLED的电流,并且可以是n沟道TFT或p沟道TFT。在本实施例中,电连接到后续步骤中形成的OLED的TFT是p沟道TFT(第二p沟道TFT)204。在本实施例中,各个像素具有一个不同于第二p沟道TFT的TFT,并且具有作为开关TFT的n沟道TFT(第二n沟道TFT)203。第二n沟道TFT的漏区通过连接电极连接到第二p沟道TFT的栅极。在第二p沟道TFT的漏区中形成电连接到后面形成的OLED的正极或负极的连接电极122。

形成电极图案,然后通过在150℃下进行12分钟的热处理去除抗蚀剂。然后,形成像素电极123,使得它与连接电极接触并覆盖连接电极,所述连接电极与第二p沟道TFT的漏区接触。在本实施例中,像素电极用作OLED的正极,并且OLED发出的光通过像素电极。因此,将透明导电膜用作像素电极。具有大的逸出功的导电膜(一般为导电氧化膜)被用作正极。导电氧化膜由氧化铟、氧化锡或氧化锌,或者它们的化合物构成。在本实施例中,利用溅射通过形成透明导电膜的ITO(氧化铟和氧化锡的合金)得到110nm厚的像素电极,并在像素部分形成它的图案,以形成矩阵图案并具有所需形状。其它可以采用的透明导电膜的示例包括氧化铟-氧化锌合金(In2O3-ZnO)膜和氧化锌(ZnO)膜。在形成像素电极的同时,可以这样形成由透明导电膜构成的电极焊盘并将其形成图案、使得它们与输入/输出端部分接触并与输入/输出端部分的电极重叠。

在形成像素电极的图案完成后,通过在250℃下进行1小时的热处理去除抗蚀剂。

图4显示了通过上述步骤完成了制造过程之后的器件。这时开始对第一衬底101上形成的TFT进行电测量。图9中显示了在沟道宽度W与沟道长度L的比率设置为50μm∶50μm时n沟道TFT的V-I特性。图10显示了在沟道宽度W与沟道长度L的比率设置为50μm∶50μm时p沟道TFT的V-I特性。

接下来,在像素电极123的每一端上形成覆盖123每一端的被称为触排(bank)的绝缘体。触排由包含硅的绝缘膜或树脂膜构成,在本实施例中,形成厚度为1μm的光敏丙烯酸树脂膜并将其构成所需形状的图案。然后,在250℃下进行1小时的热处理。

接下来准备厚度为1.1mm的高硬度衬底(第二衬底),这里为石英衬底,并利用溶于溶剂的粘合剂(第一粘合构件)或在用光(包括紫外线)照射时粘合力减小的光敏粘合剂(第一粘合构件)将其粘合到形成TFT的一侧。TFT因而被夹在石英衬底(第二衬底)和玻璃衬底(第一衬底)之间。高硬度衬底的应用防止了在后续剥离步骤期间包括TFT的层中的断裂。在本实施例中,可溶于水的粘合剂被用作第一粘合构件。其它可用的粘合剂的示例包括溶于基于乙醇的有机溶剂的粘合剂以及光敏粘合剂。在粘合衬底之前,重要的是提供便利于后续剥离步骤期间的剥离现象的引发机制。通过选择性地(部分)降低粘合力作为预处理,避免了剥离失败并提高了产量。预处理例如由以下步骤组成:在用针垂直下压薄膜的同时进行激光扫描或刮涂薄膜,以便施加负荷并沿着待剥离区的周边移动该膜。在本实施例中,使用划线器装置并且将下压量设定为0.1到2mm,从而用0.5kg/cm2的压力刮涂薄膜。

最好是从要进行预处理的区附近的区域开始剥离。

接下来,用物理方法撕开其上形成了第一材料层(钨膜)的第一衬底。这样,包括TFT的层被转移到第二衬底上并且暴露的表面是第二材料层(通过溅射形成的氧化硅膜)。第一材料层和第二材料层之间的粘合力足够大,以耐受热处理温度,但对机械力的耐受却很弱。所以,可以用相对小的力(例如用手、通过喷嘴喷出的气体的压力、超声波等)撕开第一衬底。因为通过上述预处理使粘合力部分变得很弱,因此需要更小的力撕开第一衬底。

如果采用相同尺寸的第一衬底和第二衬底使工作困难,则第二衬底的尺寸可以略小于第一衬底。如果在一片第一衬底上形成多个像素部分,则第一衬底可以被切为若干块,每块具有一个像素部分。

接下来,利用第二粘合构件将第三衬底粘合到暴露的第二材料层,从而将TFT夹在石英衬底(第二衬底)和第三衬底之间。任何衬底都可被用作第三衬底。

第二粘合构件是由非水溶性UV固化环氧树脂构成的粘合剂。表面形成了AlNXOY膜的(0.3mm厚)聚碳酸脂(PC)膜被用作第三衬底。最好将这样一种材料选作第二粘合构件:它到第二材料层的粘合力至少大于它到AlNXOY膜的粘合力。这样,可以在后续步骤中剥离第三衬底,以便单独用第二粘合构件作支撑体。

在器件通过上述步骤结束制造过程时,用千分尺测量夹在第二衬底(1.1mm)和第三衬底(0.3mm)之间的层的总厚度(总厚度包括一对衬底的厚度)。其测量的厚度为1.6到1.9mm。

将TFT夹在中间的衬底对被整个地浸入装满水的槽中,以溶解水溶性粘合构件(第一粘合构件)以及剥离第二衬底。水溶性粘合构件(第一粘合构件)的溶解速度可以通过紫外线或激光照射而提高。同时,浸泡在水中可从界面处将第三衬底从第二粘合构件上分离,以便剥离第三衬底。尽管第二衬底和第三衬底在同一步骤中进行剥离,但它们也可在不同步骤中进行剥离。

剥离之后进行热处理,以蒸发湿气。可以在剥离了第二衬底之后进行完全去除水溶性粘合构件(第一粘合构件)的处理。

这样得到的是包括TFT的层,其中单独用第二粘合构件作支撑体。现在,再次进行TFT的电测量。图11中显示了在沟道宽度W与沟道长度L的比率设定为50μm∶50μm时n沟道TFT的V-I特性。图12显示在沟道宽度W与沟道长度L的比率设定为50μm∶50μm时p沟道TFT的V-I特性。

从图9到12可以知道,TFT特性几乎没变。因此,可以说后面这些过程所进行的转移和粘贴没有影响TFT。尽管可以直接在塑料衬底上形成TFT,但衬底的低耐热性使300℃或更高温度下的热处理难以进行,并且难以形成具有如图9到12之一所示的极佳特性的TFT。通过如本实施例所示在耐热衬底上形成TFT并剥离耐热衬底,可以获得具有如图9到12之一所示的极佳特性的TFT。

在器件通过上述步骤结束制造过程时,用千分尺测量包括TFT的层的总厚度(包括第二粘合构件的厚度),并且单独利用第二粘合构件作支撑体。其测量的厚度为140到230μm。由此证明,总厚度可以比PC膜(0.3mm)薄。尽管如此之薄,但仍可以测量TFT特性,因此可以说第二粘合构件自身就是一个充分的支撑体并且所述器件可以作为半导体器件驱动。

接着,在像素电极(其末端被触排覆盖)上形成EL层并且在其上形成OLED的负极。

EL层(用于发光并用于移动载流子来引起发光的层)具有发光层和电荷传输层和电荷注入层的自由组合。例如,低分子量有机EL材料或高分子量有机EL材料被用于形成EL层。EL层可以是由通过单态激励(荧光)(单态化合物)发光的发光材料构成的薄膜或者可以是由通过三态激励(磷光)(三态化合物)发光的发光材料构成的薄膜。诸如碳化硅的无机材料可以用作电荷传输层和电荷注入层。可以采用已知的有机EL材料和无机材料。

据说负极的优选材料是具有小的逸出功的金属(一般是属于周期表中1族或2族的金属元素)或这类金属的合金。逸出功愈小,发光效率愈高。因此,将包括碱金属之一的Li(锂)的合金材料用作负极材料特别合乎需要。负极还用作所有像素共用的导线,并且在输入端部分中通过连接导线具有端子电极。

接下来,最好用有机树脂、保护膜、密封衬底或密封外壳密封至少具有负极、有机化合物层和正极的OLED,以便将所述OLED与外界完全隔开、从而防止诸如湿气和氧气的外部物质的渗入,这种渗入将由于EL层的氧化加速退化。但是,并非必需在FPC必将连接到其上的输入/输出端部分提供保护膜等。

利用各向异性导电材料将FPC(柔性印刷电路)固定在输入/输出端部分的电极上。各向异性导电材料由树脂和直径在几十到几百μm的导电微粒构成,并且所述导电微粒的表面镀Au等成分。导电微粒利用在FPC中形成的导线电连接到输入/输出端部分的电极。

如果需要,可以设置诸如由起偏振光片和相差光片构成的圆偏振片的光学膜,并可安装IC芯片。

通过上述步骤完成了连接FPC的模块型发光器件。在本实施例的发光器件中,OLED发出的光仅穿过第二粘合构件到达观察者的眼睛。所以,第二粘合构件需要用透光材料构成。

或者,像素电极可用作负极,并且EL层和正极可以层叠在负极上,从而在本实施例中以与发光方向相反的方向发光。在这种情况下,正极由透光材料构成。

在本实施例所示的示例中,在制造过程进行到第二粘合构件单独用作支撑体时形成OLED。但是,也可以在剥离第一衬底之前密封OLED,然后粘合第二衬底、剥离第一衬底、粘合第三衬底以及剥离第二衬底和第三衬底。在形成OLED之后剥离衬底的情况下,最好用有机溶剂作溶剂并采用溶于有机溶剂的粘合剂,而不是用水作溶剂并采用水溶性粘合剂。

在先于剥离衬底形成OLED的情况下,如果适当地选择第二粘合构件,则可能单独剥离第二衬底而保留第三衬底。在这种情况下,可以在塑料衬底上形成具有OLED的发光器件。

[实施例2]

在此实施例中,对通过部分地不同于实施例1的步骤制造具有OLED的发光器件的示例进行描述。

根据实施例1获得完成第一蚀刻过程的状态。尽管在实施例1中,第一掺杂过程、第二蚀刻过程和第二掺杂过程依次在第一蚀刻过程之后进行,但在本实施例中,第二蚀刻过程是在第一蚀刻过程完成之后进行的。并且在去除抗蚀剂掩膜之后,通过新的掺杂工艺进行低密度掺杂,以形成第五杂质区(n--区)。接着形成新的抗蚀剂掩膜,并利用与第二掺杂过程相同的剂量总量选择性地进行掺杂,从而利用与第一掺杂过程相同的剂量总量进行掺杂。

下面参考图5描述通过本实施例的步骤形成的TFT。

在本实施例中,通过新的掺杂工艺进行低密度掺杂而形成第五杂质区(n--区)。栅极305到308用作进行整个表面掺杂的掩膜。利用离子掺杂或离子注入作为掺杂工艺。离子掺杂工艺的条件是剂量总量为1.5×1014原子/平方厘米、加速电压为60到100keV。可以使用磷(P)或砷(As)作为提供n型导电性的杂质元素。以自定位方式形成第五杂质元素区。将1×1016到1×1017/cm3的n型杂质元素加到第五杂质区。在本实施例中,与第五杂质区相同密度的区被称为n--区。

接着形成新的抗蚀剂掩膜。在这种情况下,由于开关TFT 403的断开(OFF)电流值被降低,因而形成覆盖半导体层的沟道形成区的掩膜,所述半导体层形成像素部分401或所述部分的开关TFT 403。另外,形成掩膜来保护形成驱动电路的p沟道TFT 406的半导体层的沟道形成区或其周边区。此外,形成掩膜来覆盖形成像素部分401的电流控制TFT 404的半导体层的沟道形成区或其周边区。

利用上述抗蚀剂掩膜通过利用与第二掺杂过程相同的剂量总量选择性地掺杂,以形成与栅极305的一部分重叠的第二杂质区311。

在不去除上述抗蚀剂掩膜的情况下,通过利用与第一掺杂过程相同的剂量总量选择性地进行掺杂,以形成第一杂质区312和315。在开关TFT 403处,由抗蚀剂覆盖的区域成为第五杂质区316。

在上述步骤中,对将作为n沟道TFT的活化层的半导体层进行掺杂。

接下来,在去除上述抗蚀剂掩膜之后,如实施例1,形成抗蚀剂掩膜,并连续进行第三和第四掺杂过程。

在上述步骤中,在各个半导体层上形成n型或p型导电类型的杂质区。在像素部分401和驱动电路402,分别在半导体层上形成p-区314和318、p+区313和317,以形成p沟道型TFT,在半导体层上形成n-区311和n+区312,以形成驱动电路402的n沟道型TFT,以及在半导体层上分别形成n+区315和n--区316,以形成像素部分401的n沟道型TFT。

根据实施例1执行加到每个半导体层的杂质元素的活化过程。接下来,根据实施例1执行第一中间层绝缘膜309的形成过程、第二中间层绝缘膜(未示出)的形成过程、半导体层的氢化过程以及第三中间层绝缘膜310的形成过程。

随后形成与连接电极326接触并重叠的像素电极319。连接电极与由p沟道TFT构成的电流控制TFT的漏区接触。在本实施例中,像素电极用作OLED的正极,并且它是透明导电膜,以便将来自OLED的光传递到像素电极。

接下来形成到达栅极或导电层并将形成栅极导线的接触孔以及到达各杂质区的接触孔。在本实施例中顺序执行多个蚀刻过程。通过利用第二中间层绝缘膜作为蚀刻终止层进行第三中间层绝缘膜的蚀刻之后,通过利用第一中间层绝缘膜作为蚀刻终止层进行第二中间层绝缘膜的蚀刻,由此对第一中间层绝缘膜进行蚀刻。

之后,利用Al、Ti、Mo、W等形成电极320到326,具体地说,形成源极导线、电流源线、引出(drawing)电极和连接电极。在本实施例中,可以将由Ti膜(厚度为100nm)、包括硅的Al膜(厚度为350nm)和Ti膜(厚度50nm)组成的层叠结构用作这些电极和导线的材料,并形成图案。就这样适当地形成源电极或源极导线、连接电极、引出电极、电源线等。在栅极导线的边缘形成用于与被中间层绝缘膜覆盖的栅极导线接触的引出电极。在各导线的另一边缘处形成输入/输出端部分,在这些输入/输出端部分形成用于连接到外部电路或外部电源的电极。为与先前形成的像素电极319接触并重叠而形成的连接电极326与电流控制TFT 404的漏区接触。

如上所述,可以在一个像素中形成多个具有n沟道TFT 405、具有p沟道TFT 406的驱动电路,以及通过互补地组合这些TFT而形成的CMOS电路,以及具有n沟道TFT 403或p沟道TFT 404的像素部分401。

当完成了图案的形成时,通过象实施例1那样去除抗蚀剂来进行热处理,接着形成被称为触排的绝缘体327,从而在两端覆盖像素电极319的端部。可以用绝缘膜或树脂膜形成触排。

根据实施模式1或2,可以得到包括TFT的层,其中与第二材料层310接触的粘合构件300被用作支撑介质。

接下来,根据实施例1,在端部由触排覆盖的像素电极上形成EL层328和OLED的负极329。

在图5中说明了经过这些步骤之后的状态。

以下的步骤是用有机树脂、保护膜、密封衬底或密封外壳密封至少具有负极、有机化合物层和正极的OLED,从而掉将OLED与外界隔开。由此通过将OLED与外界完全隔开来防止使EL层退化的诸如水和氧气的物质浸入OLED。

接下来,通过利用各向异性导电材料将FPC(柔性印刷电路)粘贴到输入/输出端部分的电极上。

通过上述步骤完成连接FPC的模块型发光器件。在本实施例的发光器件中,观察者可以看到OLED发出的仅穿过第二粘合构件的光,所以,最好将具有性的材料用作第二粘合构件。

[实施例3]

显示了通过实施例1或2获得的模块型发光器件(也被称作EL模块)的顶面视图和横截面图。

图6A是EL模块的顶面视图而图6B是沿着图6A的A-A’线截取的横截面图。图6A显示了在粘合构件500上形成的基底绝缘膜501(例如第二粘合构件等),并在其上形成像素部分502、源侧驱动电路504以及栅侧驱动电路503。这些像素部分和驱动电路可以根据上述实施例1或2得到。

标号518是有机树脂而519是保护膜。像素部分和驱动电路部分被有机树脂518覆盖,而有机树脂518被保护膜519覆盖。另外,可以利用粘合构件、通过覆盖材料密封有机树脂。可以在进行剥离之前作为支撑介质粘合覆盖材料。

另外,标号508表示用于传递要输入到源侧驱动电路504和栅侧驱动电路503的信号的导线,并且它从成为外部输入端的FPC(柔性印刷电路)509接收视频信号和时钟信号。另外,这里图中仅示出FPC,但也可以将印刷布线板(PWB)粘贴在这个FPC上。本说明书中的发光器件假定不仅包括发光器件本身,还包括其上粘附了FPC和PWB的情况。

对图6B所示的横截面结构进行描述。在粘合构件500上形成基底绝缘膜501。在绝缘膜501上形成像素部分502和栅极驱动电路503。像素部分由电流控制TFT 511和多个包括电连接到电流控制TFT511的像素电极512的像素构成。另外,通过利用组合了n沟道TFT 513和p沟道TFT 514的CMOS电路形成栅极驱动电路503。

可以根据实施例1的n沟道TFT和实施例1的p沟道TFT制造TFT(包括511、513和514)。

在根据实施例2在同一衬底上形成了像素部分502、源侧驱动电路504和栅侧驱动电路503之后,根据实施模式1或2,只有粘合构件500被用作支撑介质。

像素电极512起发光元件(OLED)的正极的作用。在像素电极512的两端部分形成触排515。在像素电极512上形成发光元件的有机化合物层516和负极517。

作为有机化合物层516,应该理解,可以通过自由组合发光层、电荷传输层或电荷注入层来形成有机化合物层(用于实现发光以及因此实现载流子的移动的层)。例如,可以使用低分子量系列有机化合物材料和高分子量系列有机化合物材料。此外,作为有机化合物层516,可以使用包括通过单态激励发光的发光材料(单态化合物)的薄膜或者包括通过三态激励发光(磷光)的发光材料(三态化合物)的薄膜。此外,可能将诸如碳化硅的无机材料用作电荷传输层和电荷注入层。可以采用已知材料作为这些有机和无机材料。

负极517用作所有像素共用的导线,并且通过连接导线508电连接到FPC 509。此外,包含在像素部分502和栅侧驱动电路503中的元件都被负极517、有机树脂508和保护膜519覆盖。

另外,在可能的范围内,最好将对可见光透明或半透明的材料用作有机树脂518。此外,在可能的范围内,有机树脂518最好是不使诸如湿气和氧气的杂质透过的材料。

同时,在已经用有机树脂518覆盖了发光元件之后,最好至少在有机树脂518的表面(暴露面)上形成保护膜519,如图6A和6B所示。可以在包括衬底背面的整个表面上形成保护膜。在这种情况下,需要小心地形成保护膜,使得不会在提供外部输入端(FPC)的位置上形成保护膜。可以利用掩膜来防止在这个位置上形成保护膜。在CVD装置中,可以将诸如由特氟隆(注册商标)构成的带用作掩蔽带来覆盖外部输入端部分,以防止保护膜的成膜。氧化硅膜、DLC膜或AlNXOY膜可以被用作保护膜519。

用保护膜519密封按上述构造的发光元件,以便完全地将发光元件与外部隔离,从而防止通过氧化加速有机化合物层退化的诸如水或氧气的材料从外部进入。同时,具有导热性的膜能够消散产生的热。从而得到具有改善了可靠性的发光器件。

可以考虑另一种配置,其中像素电极被用作负极,而共同形成有机化合物层和正极,从而以与图6B所示的相反方向发光。图7显示了这种配置的示例。该配置的顶视图与图6A的顶视图相同,因此将只参考横截面图进行描述。

将对图7的横截面图所示的结构进行描述。在粘合构件600上形成绝缘膜610,并在绝缘膜610上形成像素部分602和栅侧驱动电路603。像素部分602由多个像素构成,所述多个像素包括电流控制TFT 611和电连接到电流控制TFT 611的漏极的像素电极612。另外,根据实施模式,只有粘合构件600被用作支撑介质。通过利用组合了n沟道TFT 613和p沟道TFT 614的CMOS电路形成栅侧驱动电路603。

可以用与实施例1的n沟道TFT和实施例1的p沟道TFT相同的方式制造TFT(611、613、514等)。

像素电极612起发光元件(OLED)的负极的作用。在像素电极612的两端形成触排615,并且在像素电极612上形成发光元件的有机化合物层616和正极617。

正极617还用作连接到所有像素的共用导线元件,并且通过连接导线608电连接到FPC 609。包含在像素部分602和栅侧驱动电路603中的所有元件都被负极617、有机树脂618和保护膜619覆盖。用粘合剂将覆盖构件620粘合到元件层。在所述覆盖构件中形成凹槽,并在其中放置干燥剂621。

在图7所示的配置中,像素电极被用作负极、同时以组合的方式形成有机化合物层和正极、使得以图7中箭头的方向发光。

尽管已经通过示例对顶部栅极TFT进行了描述,但是,本发明可以不拘于TFT结构来实现。例如,本发明可以应用于底部栅极(反相交错结构)TFT和交错结构TFT。

[实施例4]

本实施例是半透射型(half-transmission type)显示器件的示例,其中由具有透光的导电膜和具有反射特性的金属材料构成像素电极,如图8所示。

在液晶显示器件中,可以根据实施例1或2形成用作像素电极n沟道TFT。形成覆盖TFT的中间层绝缘层的步骤和在此步骤之前执行的步骤都与实施例1中的那些步骤一样,因此不再重复对它们的描述。与TFT的源区或漏区接触的两个电极之一由具有反射性的金属材料构成,以形成像素电极(反射部分)702。之后形成由具有透光的导电膜构成的像素电极(透射部分)701,从而与像素电极702重叠。可以将氧化铟锡(ITO)、氧化铟锌(In2O3-ZnO)或氧化锌(ZnO)用作具有透光的导电膜。

按上述步骤在第一衬底上形成像素TFT。在根据实施模式1或2剥离了第一衬底之后,形成包括其中只有粘合构件700用作支撑介质的TFT的层。

形成校直膜并对其进行磨光处理。在本实施例中,在形成校直膜之前,形成诸如丙烯酸树脂膜的有机树脂膜图案,从而在所需的位置形成柱状衬垫(未示出)来分隔衬底。柱状衬垫可以由喷在整个衬底表面的球形衬垫代替。

接下来制备用作支撑介质的相对(opposite)衬底。相对衬底具有滤色片,其中为像素配置了有色层和光屏蔽层。光屏蔽层也被放置在驱动电路部分。形成平面化膜来覆盖有色层和光屏蔽层。在平面化膜上,在像素部分中用透明导电膜形成相对电极。在相对衬底的整个表面上形成校直膜并对其进行磨光处理。

用密封材料将其中形成了像素部分和驱动电路部分的粘合构件和相对衬底粘在一起。在密封材料中混合填充物,通过该填充物和柱状衬垫以均匀间隔将两层衬底粘合在一起。接着,在两衬底之间,注入液晶材料并用密封化合物(未示出)完全密封。在得到的液晶模块上配置后灯704和光导板705。之后用封盖706覆盖液晶模块。诸如图8中以截面部分示意的有源矩阵液晶显示器件由此完成。封盖和液晶显示模块利用粘合剂和有机树脂彼此粘合。当塑料衬底和相对衬底彼此粘合时,相对衬底和框之间有一定的间隙,从而可以用有机树脂填充相对衬底四周进行粘合。由于显示器件是半透射型的,所以将起偏振光片703粘贴在粘合构件700和相对衬底上。

当提供够量外部光线时,显示器件以下述方式作为反射型显示器被驱动:当后灯处于断开状态时,通过控制相对衬底上配置的反电极和像素电极(反射部分)702之间的液晶来执行显示。当外部光量不够时,接通后灯并通过控制相对衬底上配置的反电极和像素电极(透射部分)701之间的液晶来执行显示。

但是,如果所用的液晶是TN液晶或STN液晶,在液晶的扭绞角在反射型和透射型之间变化。所以,需要优化起偏振光片和相差片。例如,需要单独提供旋光度补偿机制,用于调整液晶的扭绞角(例如利用高分子量液晶的起偏振光片)。

[实施例5]

通过实施本发明而形成的驱动电路和像素部分可被用于各种模块(有源矩阵液晶模块、有源矩阵EL模块和有源矩阵EC模块)。也就是说,通过实施本发明完成了所有的电子部件。

下面可以作为这种电子部件给出:摄像机;数字照相机;头盔显示器(护目镜型显示器);汽车导航系统;投影仪;汽车用立体声系统;个人计算机;便携式信息终端(移动计算机、移动电话或电子书籍等)等。图13到15中显示了这些示例。

图13A是包括以下部件的个人计算机:主体2001;图像输入部分2002;显示部分2003;以及键盘2004等。

图13B是包括以下部件的摄像机:主体2101;显示部分2102;语音输入部分2103;操作开关2104;电池2105;以及图像接收部分2106等。

图13C是包括以下部件的移动计算机:主体2201;摄像机部分2202;图像接收部分2203;操作开关2204;以及显示部分2205等。

图13D是包括以下部件的护目镜型显示器:主体2301;显示部分2302;以及支臂部分2303等。

图13E是利用其中记录了节目的记录媒体(以下称为记录媒体)的重放机,它包括:主体2401;显示部分2402;扬声器部分2403;记录媒体2404;以及操作开关2405等。该装置利用用于记录媒体的DVD(数字通用盘)、CD等,并可以执行音乐欣赏、电影欣赏、游戏以及用于因特网。

图13F是包括以下部件的数字照相机:主体2501;显示部分2502;取景器2503;操作开关2504;以及图像接收部分(图中未示出)等。

图14是显示司机的座位区的图。声音再现装置,具体地说是在仪表盘中配置汽车音响和汽车导航。汽车音响的主体2701包括显示部分2702、操作开关2703和2704。通过将本发明应用到显示部分2702,可以得到既薄且轻的汽车音响。并且通过将本发明应用到汽车导航系统的显示部分2801,可以得到既薄且轻的汽车导航系统。

在操作把手部分2602中,显示部分2603以数字方式显示在仪表盘2601中形成的速度表仪表的读数。通过将本发明应用到显示部分2702,可以得到既薄且轻的机器显示装置。

另外,可以形成粘贴在仪表盘部分2601的曲面上的显示部分2605。通过将本发明应用到显示部分2605,可以得到既薄且轻的机器的显示部分或图像显示装置。

此外,可以形成粘贴在前玻璃2604的曲面上的显示部分2600。在将本发明应用到显示部分2600的情况下,可使用具有透光的材料。可以得到既薄且轻的机器显示装置或图像显示装置。在本实施例中,尽管使用的是前玻璃,但也可以得到其它窗玻璃。

在本实施例中,尽管显示的是装在车上的音响和汽车导航,但本实施例也可以被用于其它显示装置或固定类型的音响和导航装置。

图15A是包括以下部件的移动电话:主体2901;声音输出部分2902;声音输入部分2903;显示部分2904;操作开关2905;天线2906;以及图像输入部分(CCD,图像传感器等)2907等。

图15B是包括以下部件的便携式书(电子书):主体3001;显示部分3002和3003;记录媒体3004;操作开关3005和天线3006等。

图15C是包括以下部件的显示器:主体3101;支撑部分3102;以及显示部分3103等。

另外,图15C中显示的显示器具有小到中间规格或大规格屏幕,例如5到20英寸的规格。此外,为了制造具有这些尺寸的显示部分,最好利用边长一米的衬底通过排式印刷来进行批量生产。

如上所述,本发明的可适用范围非常宽,并且本发明可以应用于各种领域的电子设备。注意,本实施例的电子装置可以通过利用实施例1到4中构造的任何组合来获得。

[实施例6]

在此实施例中,利用电泳显示装置作为实施例5所示的显示部分的示例进行说明。一般,电泳显示装置被应用到图15B所示的便携式书(电子书)的显示部分3002或显示部分3003。

电泳显示装置也被称为电子纸。其优点为与纸一样的可读性、与其它显示器件相比的低功耗,以及薄且轻的外形。

电泳显示装置可以采用各种形式,诸如包括带正电荷的第一微粒和带负电荷的第二微粒的多个微型包囊被分散在溶剂或溶质中。通过对微型包囊施加电场,微型包囊中的微粒以彼此相反的方向被移去、从而发出聚积在一侧的微粒颜色。另外,第一微粒和第二微粒包括染料。没有电场微粒不能被移去。此外,第一微粒和第二微粒的颜色彼此不同(包括无色)。

这样,电泳显示装置使用所谓的电介质迁移效应,其中高电介质不变材料向高电场区移动。电泳显示装置不必具有反射板和液晶显示器件所必需的相对衬底,从而厚度和重量减少一半。

分散在溶剂中的微型包囊指的是电子墨水。电子墨水可以被印刷在玻璃、塑料、织物和纸的表面上。此外,通过利用具有滤色片和颜料的微粒有可能得到彩色显示器。

可以通过在两个电极之间提供适当的上述多个微型包囊完成有源矩阵型的显示装置。如果将电场应用到微型包囊上,则该装置可以显示图像。

微型包囊中的第一微粒和第二微粒可以通过从以下材料中选择的材料和化合材料中的一种来形成:导电材料、绝缘材料、半导体材料、磁性材料、液晶材料、铁电材料、电致发光材料、电致变色材料和磁性电泳材料。

本实施例可以自由地与实施模式1到3和实施例1到5进行组合。

[实施例7]

图17和18是利用本发明形成的有源矩阵型的有机发光元件的照片图。

图17是显示根据实施模式3形成的薄的有机发光模块的弯曲状态的外部视图的照片图。图17中所示的模块具有被聚碳酸酯塑料衬底夹在中间的结构。在一对塑料衬底之间,形成负极、正极、具有夹在负极和正极之间的有机化合物的多层的发光元件以及用于驱动发光器件的TFT。另一衬底用粘合剂固定在TFT的基底膜(通过溅射形成的氧化硅膜)上,同时另一衬底也用粘合剂固定在发光元件的负极上。

通过形成多个发光元件的矩阵来构成显示区。在显示器件的周边设置用于驱动这些发光元件的驱动电路。在本实施例中,制造发出绿光的元件,用于显示发光。图18是发光的显示图。

在本实施例中,一对塑料衬底被用于固定发光元件,但并非限于这种塑料衬底。如果机械强度和发光元件的密封足够,则不需要其中某一衬底或两个衬底都不需要。

本实施例可以自由地与实施模式1到3和实施例1到6中的任何模式和实施例进行组合。

根据本发明,得到具有元件(薄膜晶体管、具有OLED的发光元件、液晶元件、存储元件、薄膜二极管、硅PIN结的光电转换元件或硅电阻元件)的既轻且薄、柔性(可弯曲)的半导体器件以及一种制造这种半导体器件的方法。

Claims (30)

1.一种半导体器件,其中,将粘合构件用作支撑体并且在与所述粘合构件接触的绝缘膜上形成元件。

2.如权利要求1所述的器件,其特征在于:所述元件选自由薄膜晶体管、具有OLED的发光元件、液晶元件、存储元件、薄膜二极管、硅PIN结的光电转换元件以及硅电阻元件组成的组。

3.如权利要求1所述的器件,其特征在于:所述粘合构件被粘贴在平面基底构件和曲面基底构件之一上。

4.如权利要求1所述的器件,其特征在于:形成与所述粘合构件接触的保护膜。

5.如权利要求1所述的器件,其特征在于:所述半导体器件选自包括摄像机、数字照相机、护目镜型显示器、汽车导航系统、个人计算机以及便携式信息终端组成的组。

6.一种制造半导体器件的方法,它包括:

在第一衬底上形成包括半导体元件的剥离层;

利用第一粘合构件将第二衬底粘合到所述剥离层上,从而将所述剥离层夹在所述第一衬底和所述第二衬底之间;

从所述剥离层上分离所述第一衬底;

利用第二粘合构件将第三衬底粘合到所述剥离层上,从而将所述剥离层夹在所述第二衬底和所述第三衬底之间;以及

从所述剥离层上分离所述第二衬底并从所述第二粘合构件上分离所述第三衬底,以形成用所述第二粘合构件作支撑体的所述剥离层。

7.如权利要求6所述的方法,其特征在于:通过用溶剂溶解所述第一粘合构件来去除所述部件,从而从所述剥离层上分离所述第二衬底。

8.如权利要求6所述的方法,其特征在于:所述第二粘合构件以大于粘合到所述第三衬底的粘合力粘合到所述剥离层。

9.如权利要求6所述的方法,其特征在于:所述第一粘合构件是光敏粘合构件,因而通过用光照射所述构件来从所述剥离层上分离所述第二衬底。

10.如权利要求6所述的方法,其特征在于:所述第二粘合构件是光敏粘合构件,因而通过用光照射所述构件来从所述第二粘合构件上分离所述第三衬底。

11.如权利要求6所述的方法,其特征在于:玻璃衬底、石英衬底以及金属衬底之一被用作所述第一衬底和所述第二衬底,而所述第三衬底是塑料衬底。

12.如权利要求6所述的方法,其特征在于:所述第三衬底是其表面上形成了AlNXOY膜的塑料膜。

13.一种制造半导体器件的方法,它包括:

在第一衬底上形成包括半导体元件的剥离层;

利用第一粘合构件将第二衬底粘合到所述剥离层上,从而将所述剥离层夹在所述第一衬底和所述第二衬底之间;

从所述剥离层上分离所述第一衬底;

利用第二粘合构件将第三衬底粘合到所述剥离层上,从而将所述剥离层夹在所述第二衬底和所述第三衬底之间;以及

从所述剥离层上分离所述第三衬底并从所述剥离层上分离所述第二衬底,以形成用所述第一和第二粘合构件作支撑体的所述剥离层。

14.如权利要求13所述的方法,其特征在于:所述第一粘合构件以大于其粘合到所述第二衬底的粘合力粘合到所述剥离层。

15.如权利要求13所述的方法,其特征在于:所述第二粘合构件是光敏粘合构件,因而通过用光照射所述构件来从所述第二粘合构件上分离所述第三衬底。

16.如权利要求13所述的方法,其特征在于:所述第一粘合构件是光敏粘合构件,因而通过用光照射所述构件来从所述第一粘合构件上分离所述第二衬底。

17.如权利要求13所述的方法,其特征在于:玻璃衬底和石英衬底之一被用作所述第一衬底。

18.如权利要求13所述的方法,其特征在于:所述第二衬底是其表面上形成了AlNXOY膜的塑料膜。

19.如权利要求13所述的方法,其特征在于:所述第三衬底是其表面上形成了AlNXOY膜的塑料膜。

20.一种制造半导体器件的方法,它包括:

在第一衬底上形成包括半导体元件的剥离层;

利用第一粘合构件将第二衬底粘合到所述剥离层上,从而将所述剥离层夹在所述第一衬底和所述第二衬底之间;

从所述剥离层上分离所述第一衬底;

利用第二粘合构件将第三衬底粘合到所述剥离层上,从而将所述剥离层夹在所述第二衬底和所述第三衬底之间;以及

从所述剥离层上分离所述第二衬底,以便形成用所述第二粘合构件和所述第三衬底作支撑体的所述剥离层。

21.如权利要求20所述的方法,其特征在于:所述第一粘合构件和所述第二衬底的材料具有的硬度大于所述第三衬底的硬度。

22.如权利要求20所述的方法,其特征在于:通过用溶剂溶解所述第一粘合构件来去除所述构件,从而从所述剥离层上分离所述第二衬底。

23.如权利要求20所述的方法,其特征在于:所述第一粘合构件是光敏粘合构件,因而通过用光照射所述构件来从所述剥离层上分离所述第二衬底。

24.一种半导体器件,其中,塑料衬底和粘合构件用作支撑体,并且在绝缘膜上形成与所述粘合构件接触的元件。

25.如权利要求24所述的器件,其特征在于:所述元件选自由薄膜晶体管、具有OLED的发光元件、具有液晶的液晶元件、存储元件、薄膜二极管、硅PIN结的光电转换元件以及硅电阻元件组成的组。

26.如权利要求24所述的器件,其特征在于:所述塑料衬底被粘贴在平面或曲面基底构件之一上。

27.如权利要求24所述的器件,其特征在于:与所述粘合构件接触的绝缘膜是包括惰性气体成分的氧化层。

28.如权利要求24所述的器件,其特征在于:所述半导体器件选自由摄像机、数字照相机、护目镜型显示器、汽车导航系统、个人计算机以及便携式信息终端组成的组。

29.一种制造半导体器件的方法,它包括:

在第一衬底上形成包括半导体元件的剥离层;

利用第一粘合构件将第二衬底粘合到所述剥离层上,从而将所述剥离层夹在所述第一衬底和所述第二衬底之间;

从所述剥离层上分离所述第一衬底;

利用第二粘合构件将其中形成了保护膜的第三衬底粘合到所述剥离层上,从而将所述剥离层夹在所述第二衬底和所述第三衬底之间;以及

从所述剥离层上分离所述第二衬底并从所述第二粘合构件上分离所述第三衬底,以形成用所述第二粘合构件和所述保护膜作支撑体的所述剥离层。

30.如权利要求29所述的方法,其特征在于:所述保护膜是氮化硅膜或氧氮化硅膜。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP333565/2001 | 2001-10-30 | ||

| JP333565/01 | 2001-10-30 | ||

| JP2001333565 | 2001-10-30 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2006101598018A Division CN1945856B (zh) | 2001-10-30 | 2002-10-30 | 半导体器件及其制造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1417841A true CN1417841A (zh) | 2003-05-14 |

| CN1288710C CN1288710C (zh) | 2006-12-06 |

Family

ID=19148809

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB02148256XA Expired - Lifetime CN1288710C (zh) | 2001-10-30 | 2002-10-30 | 半导体器件及其制造方法 |

| CN2006101598018A Expired - Fee Related CN1945856B (zh) | 2001-10-30 | 2002-10-30 | 半导体器件及其制造方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2006101598018A Expired - Fee Related CN1945856B (zh) | 2001-10-30 | 2002-10-30 | 半导体器件及其制造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (7) | US7332381B2 (zh) |

| JP (2) | JP4015003B2 (zh) |

| KR (2) | KR100944886B1 (zh) |

| CN (2) | CN1288710C (zh) |

| TW (1) | TW594947B (zh) |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7492028B2 (en) | 2005-02-18 | 2009-02-17 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and manufacturing method of the same, and a semiconductor device |

| CN102176306A (zh) * | 2003-11-25 | 2011-09-07 | 伊英克公司 | 电光显示器及驱动方法 |

| CN103091888A (zh) * | 2012-09-26 | 2013-05-08 | 友达光电股份有限公司 | 制作显示面板的方法 |

| CN103875309A (zh) * | 2011-10-12 | 2014-06-18 | 旭硝子株式会社 | 带密合性树脂层的电子器件的制造方法 |

| CN105432147A (zh) * | 2013-07-31 | 2016-03-23 | 旭硝子株式会社 | 电子设备的制造方法 |

| CN106163798A (zh) * | 2014-04-10 | 2016-11-23 | 旭硝子株式会社 | 玻璃层叠体及其制造方法、电子器件的制造方法 |

| CN106575168A (zh) * | 2015-08-05 | 2017-04-19 | 深圳市柔宇科技有限公司 | 触摸膜、有机发光二极管显示面板及触摸膜的制备方法 |

| CN107256929A (zh) * | 2012-05-04 | 2017-10-17 | 株式会社半导体能源研究所 | 发光装置的制造方法 |

| CN108475027A (zh) * | 2016-01-18 | 2018-08-31 | Asml荷兰有限公司 | 射束测量系统、光刻系统和方法 |

Families Citing this family (176)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3066944B2 (ja) * | 1993-12-27 | 2000-07-17 | キヤノン株式会社 | 光電変換装置、その駆動方法及びそれを有するシステム |

| US8415208B2 (en) * | 2001-07-16 | 2013-04-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and peeling off method and method of manufacturing semiconductor device |

| JP2003109773A (ja) * | 2001-07-27 | 2003-04-11 | Semiconductor Energy Lab Co Ltd | 発光装置、半導体装置およびそれらの作製方法 |

| JP5057619B2 (ja) | 2001-08-01 | 2012-10-24 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| TW554398B (en) * | 2001-08-10 | 2003-09-21 | Semiconductor Energy Lab | Method of peeling off and method of manufacturing semiconductor device |

| US7351300B2 (en) | 2001-08-22 | 2008-04-01 | Semiconductor Energy Laboratory Co., Ltd. | Peeling method and method of manufacturing semiconductor device |

| KR100944886B1 (ko) * | 2001-10-30 | 2010-03-03 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치의 제조 방법 |

| TWI264121B (en) | 2001-11-30 | 2006-10-11 | Semiconductor Energy Lab | A display device, a method of manufacturing a semiconductor device, and a method of manufacturing a display device |

| US6953735B2 (en) | 2001-12-28 | 2005-10-11 | Semiconductor Energy Laboratory Co., Ltd. | Method for fabricating a semiconductor device by transferring a layer to a support with curvature |

| US6949389B2 (en) * | 2002-05-02 | 2005-09-27 | Osram Opto Semiconductors Gmbh | Encapsulation for organic light emitting diodes devices |

| DE60325669D1 (de) * | 2002-05-17 | 2009-02-26 | Semiconductor Energy Lab | Verfahren zum Transferieren eines Objekts und Verfahren zur Herstellung eines Halbleiterbauelements |

| US6840424B2 (en) * | 2002-10-08 | 2005-01-11 | Chien-Min Sung | Compression bonding tools and associated bonding methods |

| JP2004140267A (ja) | 2002-10-18 | 2004-05-13 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP4693411B2 (ja) * | 2002-10-30 | 2011-06-01 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| AU2003275615A1 (en) | 2002-11-01 | 2004-05-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing semiconductor device |

| US6881975B2 (en) * | 2002-12-17 | 2005-04-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of manufacturing the same |

| JP4554152B2 (ja) * | 2002-12-19 | 2010-09-29 | 株式会社半導体エネルギー研究所 | 半導体チップの作製方法 |

| JP4101643B2 (ja) * | 2002-12-26 | 2008-06-18 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4373085B2 (ja) * | 2002-12-27 | 2009-11-25 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法、剥離方法及び転写方法 |

| US7652359B2 (en) | 2002-12-27 | 2010-01-26 | Semiconductor Energy Laboratory Co., Ltd. | Article having display device |

| KR101033797B1 (ko) | 2003-01-15 | 2011-05-13 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 박리 방법 및 그 박리 방법을 사용한 표시 장치의 제작 방법 |

| US7436050B2 (en) | 2003-01-22 | 2008-10-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having a flexible printed circuit |

| JP2004247373A (ja) * | 2003-02-12 | 2004-09-02 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US7973313B2 (en) | 2003-02-24 | 2011-07-05 | Semiconductor Energy Laboratory Co., Ltd. | Thin film integrated circuit device, IC label, container comprising the thin film integrated circuit, manufacturing method of the thin film integrated circuit device, manufacturing method of the container, and management method of product having the container |

| JP2004259796A (ja) * | 2003-02-25 | 2004-09-16 | Sony Corp | 薄膜デバイスの製造方法および薄膜デバイス |

| JP4526771B2 (ja) * | 2003-03-14 | 2010-08-18 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US20060180342A1 (en) * | 2003-03-28 | 2006-08-17 | Minoru Takaya | Multilayer substrate and method for producing same |

| EP1629531A2 (en) * | 2003-04-02 | 2006-03-01 | Koninklijke Philips Electronics N.V. | Method of manufacturing a flexible electronic device and flexible device |

| US7566001B2 (en) | 2003-08-29 | 2009-07-28 | Semiconductor Energy Laboratory Co., Ltd. | IC card |

| US8040042B2 (en) * | 2003-09-08 | 2011-10-18 | Sumitomo Metal Mining Co., Ltd. | Transparent electroconductive layered structure, organic electroluminescent device using the same layered structure, method for producing the same layered structure, and method for producing the same device |

| EP1528594B1 (en) * | 2003-10-28 | 2019-05-29 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US8048251B2 (en) | 2003-10-28 | 2011-11-01 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing optical film |

| JP4507560B2 (ja) * | 2003-10-30 | 2010-07-21 | 日本電気株式会社 | 薄膜デバイス基板の製造方法 |

| US7443378B2 (en) * | 2003-11-17 | 2008-10-28 | Lg Electronics Inc. | Driving apparatus of electronic ink display device and method therefor |

| JP4689249B2 (ja) * | 2003-11-28 | 2011-05-25 | 株式会社半導体エネルギー研究所 | 表示装置の作製方法 |

| US7601236B2 (en) * | 2003-11-28 | 2009-10-13 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing display device |

| US7768405B2 (en) * | 2003-12-12 | 2010-08-03 | Semiconductor Energy Laboratory Co., Ltd | Semiconductor device and manufacturing method thereof |

| US7586171B2 (en) * | 2004-04-14 | 2009-09-08 | Yong Cao | Organic electronic device comprising conductive members and processes for forming and using the organic electronic device |