CN1679110A - 差分浮栅非挥发性存储器 - Google Patents

差分浮栅非挥发性存储器 Download PDFInfo

- Publication number

- CN1679110A CN1679110A CN03820492.4A CN03820492A CN1679110A CN 1679110 A CN1679110 A CN 1679110A CN 03820492 A CN03820492 A CN 03820492A CN 1679110 A CN1679110 A CN 1679110A

- Authority

- CN

- China

- Prior art keywords

- floating boom

- pfet

- storer

- transistor

- coupled

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3468—Prevention of overerasure or overprogramming, e.g. by verifying whilst erasing or writing

- G11C16/3486—Circuits or methods to prevent overprogramming of nonvolatile memory cells, e.g. by detecting onset or cessation of current flow in cells and using the detector output to terminate programming

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0441—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing multiple floating gate devices, e.g. separate read-and-write FAMOS transistors with connected floating gates

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

- G11C16/28—Sensing or reading circuits; Data output circuits using differential sensing or reference cells, e.g. dummy cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3468—Prevention of overerasure or overprogramming, e.g. by verifying whilst erasing or writing

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2216/00—Indexing scheme relating to G11C16/00 and subgroups, for features not directly covered by these groups

- G11C2216/02—Structural aspects of erasable programmable read-only memories

- G11C2216/10—Floating gate memory cells with a single polysilicon layer

Abstract

本发明涉及利用差分pFET浮栅晶体管来存储信息的差分浮栅非挥发性存储器和存储器阵列的若干设计。本发明也提供建构所述存储器和存储器阵列的方法以及与所述存储器和存储器阵列有关的操作和测试方法。

Description

相关案例

本申请案是以发明者Shail Srinivas、Chad A.Lindhorst、Yanjun Ma、TerryHaas、Kambiz Rahimi和Christopher J.Diorio的名义于2002年7月5日申请的共同代决的第10/190,337号美国专利申请案的部分接续申请案并在此共同让渡。

技术领域

本发明针对非挥发性存储器(NVM)。特别针对用pFET(p通道场效晶体管)浮栅装置以差分构造建构的NVM。

背景技术

许多CMOS(互补型金属氧化物半导体)集成电路都需要少量的芯片上非挥发性存储器(NVM)。典型应用包括存储安全设定、RFID(射频识别)数据、系统构造、序列号、校准和微调设定等。考虑到成本和产量原因,理想的NVM应为具有零额外处理遮罩的最新技术的逻辑CMOS。不幸地是,主要的存储器制造商都关注于开发能生产不断增加的存储密度(如,256Mb闪存)的定制NVM制程,而几乎都忽略了对相对少量的NVM的应用(数百字)的需求。因此,要求少量非挥发性存储的CMOS设计人员就必须(1)使用如芯片上熔丝等技术;(2)支付成本并承担关于使用高密度嵌入式NVM的产品降级的费用;(3)采用芯片外存储;或(4)使用由相关备用电池供电的SRAM(静态随机存取存储器)存储。

在高度集成的CMOS应用中需要少量NVM的设计人员会面临某些令人不悦的取舍问题。显而易见的方法是使用具有嵌入式NVM的CMOS制程。不幸地是,嵌入式NVM制程不仅要负担更高的晶片成本,同时趋向成为较早一代的技术。更高成本归因于NVM制程一般需要额外的遮罩和制作步骤(如,为了得到第二多晶硅层)的事实。由于将NVM添加到逻辑制程会耗费时间和测试,所以才出现较早一代的技术,,因此NVM制程通常落后于最新技术一年。其结果可能是,为很少的NVM比特,使整个CMOS芯片成本更高且性能降低。

嵌入式NVM的一个替代方案是使用激光或电子编程的熔丝(或反熔丝)。需要一次编程的应用可发现此替代方案具有吸引力,但是如熔丝“愈合”和编程成本等重大技术难题依然是令人困扰的问题。此外,熔丝和反熔丝通常在最新技术CMOS制程中不可用。

另一选择是使用芯片外解决方案,诸如一个分离NVM芯片或芯片上SRAM的备用电池。不幸地是,此种解决方案需要额外的装置,且在芯片外NVM的情况下,数据暴露在潜在的黑客袭击(hacking)下。当然,益处是设计人员可用前沿技术建构芯片的其余部分,而不会引入NVM制程的间接费用。缺点是在PCB(印刷电路板)领域和零件数方面的更高成本。

CMOS设计人员所需要的是在最新技术逻辑CMOS方面的NVM能力。

发明内容

本发明涉及大量利用差分pFET浮栅晶体管来存储信息的差分浮栅非挥发性存储器和存储器阵列的设计。本发明也提供建构所述存储器和存储器阵列的方法以及与所述存储器和存储器阵列有关的操作和测试方法。

附图说明

并入本发明且成为本说明书一部分的附图图解了本发明的一个或多个实施例,并连同详细描述一起解释了本发明的原理和建构。

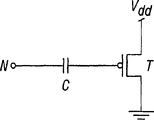

图1A为图1B浮栅MOSFET的漏极电流对比控制栅电源电压的曲线图。

图2A为根据本发明实施例的装置的正视横截面图。

图2B为图2A装置的MOS能带图。

图3为根据本发明实施例的存储器的电示意图。pFET M2用于通过信号“偏压”来设定该差分对偏流,而浮栅pFET M0和M1充当存储装置。短路的pFET T0和T1用以从浮栅中除去电荷从而和/或充当控制栅。如所属领域的技术人员将显而易见的是,可使用短路的nFET来替代地建构T0和T1。

图4为与栅极到漏极电压对比注入效率的曲线图,其中注入效率定义为栅电流除以源电流。

图5A为根据本发明一个替代实施例的存储器的电示意图,其包含一个无穿隧接合(tunneling junction)的差分存储器。可使用UV光或所属技术领域人员熟知的其它技术来擦除浮栅,且可使用注入对存储器进行一次编程。

图5B为根据图5A电路的替代实施例的存储器电示意图。

图6A为差分存储器电示意图,其具有选择晶体管(select transistor)以判定存储器之哪一侧将经受本发明实施例的注入。

图6B为根据图6A存储器的替代实施例的存储器电示意图,其包括一个根据本发明实施例的行选择开关。

图7为耦合到pFET电流源的差分存储器电路的电示意图,其具有在此情况下以根据本发明实施例的nFET建构的选择晶体管(S0、S1)(在此有时称作“序列选择开关”)。

图8为差分存储器电路的电示意图,其中在根据本发明实施例,电流被控制在浮栅注入晶体管的漏极。因为存在两个单独的电流控制,所以可在M0和M1中分别控制注入。

图9为根据本发明另一实施例的图8差分存储器电路的电示意图。在此版本中,对节点偏差0或节点偏差1施加正偏压并对其它节点施加0V将写入所述存储器。

图10为根据本发明实施例的存储器电路的电示意图,其包括与每一浮栅有关的pFET读取晶体管。

图11为根据类似图10的本发明实施例的存储器电路的电示意图,但是其包括行选择晶体管(M0、M1)以从差分读出放大器(sense amplifier)选择性隔离个别存储位置。

图12为根据本发明实施例的图11方框12内所含有的电路的替代部分的电示意图。

图13为建构双向穿隧的本发明实施例的电示意图。

图14为基于图13的本发明替代实施例的电示意图。在此版本中,通过电子注入写入存储器,并且pFET读取晶体管与每一浮栅相关联。电容性耦合的控制栅输入节点促进本文描述的边界读取(margin read)和写干扰减轻处理。

图15为本发明实施例的电示意图,其中一半的差分存储位置由一行存储器阵列的所有存储位置(memory location)共享的。此实施例对差分存储器的内存条(memory bank)尤其有用。

图16为通过添加一对浮栅晶体管(M2、M3)以监视穿隧处理的结束来修改图14版本的本发明实施例的电示意图。

图17为本发明实施例的电示意图,其使用反馈以在穿隧期间审慎地少量注入存储器,来预防存储器浮栅的过穿隧问题。

图18为展现图17存储器简化的本发明实施例的电示意图。所述Read not信号用于将存储器配置为读取模式。

图19和20为本发明实施例的电示意图,其说明了可在所述注入晶体管的漏极侧控制存储器电流。图20的实施例具有控制所述写入和读取电流的明确的nFET电流槽(current sink)M0。

图21为根据本发明实施例的pFET穿隧接合装置的布局图。

图22为沿图21的线22-22截取的横截面图。

图23为根据本发明实施例的n井整体(bulk)nFET穿隧接合装置的布局图。

图24为根据本发明实施例的MOSCAP型穿隧接合装置的横截面图。

图25为根据本发明实施例的差分存储器的电示意图。

图26为根据本发明另一实施例的替代差分存储器的电示意图。

图27为另一个差分存储器的电示意图。

图28为差分存储器的电示意图,其具有使其不同侧经独立写入的能力。

图29为另一替代差分存储器的电示意图。

图30为另一个替代差分存储器的电示意图。

图31为另一个替代差分存储器的电示意图。

图32为另一个替代差分存储器的电示意图。

图33为另一个替代差分存储器的电示意图。

图34为用于说明边界读取的第一方法的另一个替代差分存储器的电示意图。

图35为用于说明边界读取的第二方法的另一个替代差分存储器的电示意图。

图36为如那些本发明所涵盖的存储器的写入电流和写干扰电流对比写入电压的曲线图。

图37为设计用以降低写干扰的经修改的存储器的电示意图。

图38、39和40为具有各种类型差分存储器的差分存储器阵列的替代建构。

图41和42为外部注入电路的替代建构,其用以分开以相对高的浮栅制造的存储器,其反而可能阻止电子注入到浮栅上。

图43为说明根据本发明实施例存储器的阵列布局图。

图44为根据本发明实施例的示范性写入电路的电示意图。

图45为根据现有技术的示范性差分读出放大器电路的电示意图。

图46为根据现有技术UV可擦除的视窗存储装置的正视横截面图。

具体实施方式

本文以差分浮栅非挥发性存储器描述本发明的实施例。所属领域的技术人员将了解本发明的下列详细说明仅是说明性的,并且无意以任何方式限制。受益于此揭示内容的所属领域技术人员容易明了本发明的其它实施例。现在将详细参照如在本发明随附图式中所说明的本发明的建构。贯穿图式和下列详细说明使用相同的参考代号以指代相同或类似部分。

为清晰起见,并不在此展示和描述所有的所述建构的常规特征。当然应了解在任何所述实际建构的开发中,必须判定无数特定建构以便达到开发商的特定目标,诸如顺应应用和商业相关的约束,并且这些特定目标会依各建构和各开发商而改变。此外,应了解所述开发工作可能复杂而耗时,但对于受益于此揭示内容的所属领域技术人员其会成为工程的常规任务。

本发明一般用于非挥发性存储器,且具有如在嵌入式CMOS应用中可能发现的低密度嵌入式非挥发性存储器的特别应用。所述嵌入式CMOS应用包括(但不限于)存储:(1)芯片序列号(即,芯片标签);(2)ASIC(应用特定集成电路)中的配置信息;(3)射频识别(RFID)集成电路中的产品、封装和/或资产数据;(4)嵌入式微控制器的编码或数据;(5)模拟微调信息;(6)FPGA配置信息;和(7)如所属领域技术人员明了的许多其它应用。与常规的基于nFET的非挥发性存储器相比,使用pFET具有至少以下优点:电荷泵功率降低、编程/擦除循环持久性(由于氧化磨损减少)增加,和在逻辑CMOS制程中可用(由于存储器泄漏减少和事实上存储器仅使用nFET和pFET)。

任何可重新编程的NVM技术必须符合两个关键要求:(1)持久性和(2)保持性。持久性指的是擦除/写入循环的次数(NVM理想上可具有无限次读取循环)。保持性指的是存储器存储时间。在过去的二十年中,闪存和EEPROM技术的以致使产生一套商业上可接受的NVM设计标准。标准CMOS制程中的任何设计应该符合这些相同标准。所述两项标准是10年的保持性和10,000次(最小)的擦除/写入循环。

NVM装置通过改变晶体管或其它电路元件的物理属性来存储信息。在浮栅存储器(如,闪存或EEPROM)的情况下,所述物理属性是存储在硅MOSFET(金属氧化半导体场效晶体管)的电隔离(浮动)栅上的电子量。所有的NVM装置磨损,意味着在一定次数的擦除/写入循环后,所述存储器将不再符合其10年保持性的要求。在浮栅存储器的情况下,因为移动电子通过围绕电隔离栅的氧化绝缘体总是损害该绝缘氧化物。

浮栅存储器技术是以硅MOSFET的浮栅上的电子来存储信息。从浮栅添加或除去电子会改变MOSFET的阈值电压。图1A是用于图1B的浮栅MOSFET的漏极电流对比控制栅电源电压的曲线图。为了读取存储器,要测量浮栅MOSFET的通道电流。如观察图1A的左侧曲线,那么所存储的存储器是逻辑“1”;如果观察图1A的右侧曲线,那么所存储的存储器是逻辑“0”,或反过来也如此。在不存在控制栅时,浮栅的电压确定其相关晶体管的状态。对于pFET,低浮栅电压意味着晶体管更多为“on”(即,较高的源极-漏极电流),然而高浮栅电压意味着晶体管更多为“off”(即,较低的源极-漏极电流)。可基于浮栅晶体管的相对on/off状态而读取逻辑“1”或逻辑“0”。

NVM设计人员可使用n通道或p通道浮栅MOSFET作为存储器晶体管。自从20世纪80年代早期已使用n通道MOSFET,这是因为尺寸较小并且存在将nFET通道电子注入到浮栅上的直接方法。这个选择启动高度经修改的CMOS制程的高密度闪存和EEPROM。然而,在逻辑CMOS中,情况相反——pFET大大优于nFET,因为与nFET NVM相比pFET NVM具有较好的保持性,并且与nFET NVM相比pFET NVM允许更多的擦除/写入循环。

当然,使用pFET NVM也存在缺点。在专用制程中发现与nFET NVM相比pFET NVM具有较大尺寸,并且趋向具有较长的写入时间。对于小存储器(即,那些小于或等于大约60kbits的存储器),保持性和持久性利益和零制程遮罩增加显著胜过这些缺点。

图2A是用于根据本发明实施例的装置正视横截面图。图2B是用于图2A的装置的MOS能带图。图2A和2B说明pFET NVM为什么具有与nFETNVM相比较好的保持性。装置物理性展示对于从pFET的电子泄漏的能障是4.16eV,然而对于nFET仅为3.04eV。这个差别意味着在相同的氧化物厚度下,pFET存储器可以其较高的能障展现出显著小于nFET存储器的穿过栅氧化物的电子穿隧现象。在专用CMOS制程中,这个差异并没有实际影响,因为制程工程师仅需加厚所述栅氧化,直到存储器具有10年的保持性。所有目前商用基于nFET的NVM都使用80或更厚的氧化物。不幸地是,在现代逻辑CMOS中并不存在80的氧化物(0.35μm和更小的制程线宽)。从而,在逻辑CMOS中以70或较薄的栅氧化物构造的nFET NVM在正常的制程变化和温度变化上根本无法满足10年保持性的要求。解决方案是使用pFET NVM。如在现代双栅氧化物CMOS制程中可用的70pFET具有与专用制程中的82nFET相同的数据保持性。简而言之,保持性对于NVM很关键,并且在目前技术逻辑CMOS中pFET具有10年的保持性,然而nFET没有。

Diorio等人的题目为“Hole Impact Ionization Mechanism for Hot E1ectronInjection and Four Terminal pFET Semiconductor Structure for Long-TermLearning”的美国专利第5,990,512号描述了用于向并从浮栅pFET的栅传送电荷的方法。本发明的某些实施例使用浮栅pFET作为存储器存储晶体管,而512专利中所描述的撞击离子化热电子注入(IHEI)和穿隧方法用于写入存储器。本发明其它实施例运用直接穿隧代替IHEI。因为IHEI和穿隧并不要求特定装置制程,所以可使用与制造标准数字逻辑晶体管相同的IC制程建造浮栅装置。

差分存储器技术

通过采用差分存储器,而不是标准单端存储器,使根据本发明制作的存储器展现出增加的读取速度、降低的读取电流和功率消耗、降低的穿隧和注入效率的变化的敏感度、宽松的芯片上电流和电压参考的精确度的要求,以及降低的温度和电源电压敏感度。从而,使用差分式的基于pFET的存储器的组合方法可启动逻辑CMOS中的NVM。

图3是根据本发明实施例的存储器的电示意图。pFET M2用以通过信号“偏压”来设定差分对偏流Ib,且浮栅pFET M0和M1充当存储装置。短路的pFET T0和T1用以从浮栅除去电子和/或充当控制栅。如所属领域的技术人员将显而易见的,可使用短路的nFET或MOSCAP替代地建构T0和T1。(控制栅是电容器或电容性耦合到浮栅的节点。根据本发明,所述控制栅可以建构为电容器或短路的pFET等,而无需将另一层添加到半导体晶片)可通过存储在两个浮栅FG0和FG1上,而不是如基于nFET的NVM中常见的单一存储器元件的开-关状态上的电荷差,来确定差分存储器的逻辑状态。无论存储器元件存储的是逻辑0或逻辑1,两个晶体管都具有反相通道。常规差分读出放大器电路D1分别地读出M0与M1的漏极电流I0和I1,来确定存储器的状态。

基本存储器元件的擦除循环可以如下运作。可以通过使用Fowler-Nordheim穿隧以从两个浮栅除去电子的方式来擦除差分存储器。根据本发明的一个实施例,这可以通过使两者穿隧接合(T0和T1)到大约10V而完成。为了在pFET浮栅晶体管隧道到完全关闭状态之前停止所述擦除处理,所以将在擦除处理期间以常规方式监视漏极电流(I0和I1)。一旦特别存储器元件的漏极电流达到预定最小值后(如,根据本发明一个实施例的约10nA),穿隧完成(TunDone)信号就以常规方式产生。这个信号可以用来停止在那个浮栅上或在浮栅的区块上的穿隧处理。这个反馈处理确保当擦除时没有浮栅晶体管被完全关闭。

基本存储器元件的编程循环可以如下运作。为了将逻辑1编程到存储位置,可以使用晶体管M2对存储器元件施加偏流,而同时在晶体管M1上施加相对大的漏极到源极电压(通过向M1漏极施加低或负电压)。0.18μmCMOS制程中的典型值是Vdd=1.8V并且V_M1drain=-3.3V。晶体管M2和M1导电,并且使用如美国专利第5,990,512号所论述的IHEI制程将电子注入到浮栅FG1上。随后进行相同程序以写入逻辑0,除了是注入晶体管M0而不是M1以外。

所述注入制程是自限性的,意味着当电子注入到浮栅上时,晶体管自身会停止所述注入制程。不像nFET、pFET会自限其IHEI电流,因为注入会引起其浮栅电压降低。随着栅极电压降落,注入晶体管的漏极到栅极电压也会降低。因为IHEI会随着漏极到栅极电压的降低而按指数规律地降低(如,图4所说明的,其为栅极电流/电源电流对栅极到漏极电压的曲线图),所述晶体管自身停止IHEI制程。

或者,所属领域的技术人员现将认识到也可以创建一个可以用于终止注入制程的发信号电路,如,通过当注入晶体管的浮栅触达到预定电压时,通过晶体管M2来阻挡电流。

基本差分存储器元件的读取循环可以如下运作。为了读取差分存储器元件的内容,首先使用晶体管M2向存储器元件施加偏流。读取根据区别在两个半个差分存储器元件之间的较为导电路径的原理而操作。如果FG0具有比FG1低的电压,那么M0将会更为导电,并且大部分的偏流将按I0而穿过。如果FG1具有比FG0低的电压,那么保持互补情况。接着,常规差分读出放大器通过比较I0和I1来判定存储器元件是否保持逻辑1或逻辑0。因为所述存储器为差分的,所以当读取存储器时,可以在晶体管M2内使用任意小的偏流。从而,在读取操作期间,存储器可以使用任意低的功率。穿隧接合

图5A是本发明的替代实施例的存储器的电示意图,其中包含无穿隧接合的差分存储器,以从浮栅FG0和FG1除去电子。在此,可通过使用透过含有芯片C上的装置的封装P中的适当视窗W的诸如展示在浮栅上的UV光的电磁辐射,或所属领域的技术人员熟知的其它技术,根据本实施例来擦除封装P(如图46说明)的芯片C上的浮栅FG0和FG1,并且通过使用由电流源、电阻器、FET或电压源(本文通称为电流源)供电的注入来对存储器进行一次编程。以此方式可以节省与穿隧接合相关的布局面积。除去穿隧接合的选择适用于所有本发明的实施例,而将穿隧接合放入基板的相同或单独的n井内的选择也同样适用。如果穿隧接合形成在单独n井中,那么可以为擦除的目的而选择存储器的单一节点(即,单侧)。如果穿隧接合形成在相同的n井内,那么可以保留晶粒区域,并且同时擦除差分存储器的两侧。特别实施例中使用的精确构造将取决于设计人员。图5B说明了图5A存储器的替代实施例,其包括分别由选择线路Sel_0、Sel_1控制的选择晶体管S0、S1。在这个版本中并没有提供穿隧接合。

本文描述的装置可以为可擦除或可一次编程的。对于可一次编程的装置,并不要求穿隧接合(尽管其可包括作为一个设计选择)。那些要求擦除的本发明的实施例可以建构穿隧接合以使电子穿隧离开浮栅。可以许多不同方式建构穿隧接合。在一个实施例中,将单独的n井远离浮栅晶体管所位于的n井而放置。所述浮栅晶体管是一个pFET,其可用于IHEI、直接穿隧或另外用于跨越绝缘体将电子移动到浮栅的类似制程。根据本实施例,将浮栅放置在两个n井之间。所述穿隧接合可以是:(1)一个MOSCAP,诸如如图24中所展示的元件124,其建构为安置在n井中的n+区;(2)一个短路的nFET(具有相互连接的漏极和源极);(3)一个短路的pFET(具有相互连接的漏极、源极和井接触);或如现将对所属领域的技术人员显而易见的其它排置方式。参见图2A关于根据本发明一个实施例的存储器的一般布局。

现转向图21和22,图中说明了一个pFET穿隧接合。图21为pFET穿隧接合的布局(上)图,并且图22为沿图21的线22-22截取的横截面图。如可以看到,所述装置安置在n井100中,其中n井安置在基板102中。pFET穿隧接合装置104包括n+井接触区106和源极p+区108以及漏极p+区110,在可能的地方,所有这些都可以被页面内的逐个存储器元件所共享。浮栅112座落于形成在源极和漏极之间通道上,并且通过诸如二氧化硅的介电层114与通道分离。井接触、源极和漏极通过导体116而共同短路,所述导体116由任何适当的导电材料构成。

现转向图23,在所述横截面图中说明了nFET穿隧接合装置118。在本实施例里,将n井100安置在p基板102中。在n井100内是一对构成晶体管源极和漏极的n+区120和122。这些如上所述的通过导体116而彼此短路。如上所述,浮栅112座落于形成在源极和漏极之间的通道上,并且通过诸如二氧化硅的介电层114与通道分离。

现转向图24,在横截面图中说明了MOSCAP穿隧接合装置124。在本实施例中,将n井100安置在p基板102中。在n井100内是耦合到导体116的n+区126。本装置的其余细节如上文所述。

到差分存储器一侧的限制性注入

图6A为具有选择晶体管的差分存储器电示意图,所述选择晶体管判定存储器的哪一侧经受根据本发明实施例的注入。图6A的存储器超过图3存储器的优点,在于两个注入晶体管M0、M1的漏极在注入期间可被降低,并且可以通过施加选择信号到其对应的选择线路Sel_0、Sel_1,来启动对应的选择晶体管S0、S1,来选择一侧用于写入。可以将这个差分对的输入节点X连接到如图3中的偏压晶体管或任何其它类型的可选电流源电路。如在本文所展示的每一个实施例中,所述输入节点X可以是安置在实际存储器内的电流源,或通向安置在其它地方的另一电流源的导体。例如在阵列列中的存储器元件之中共享电流源可节省布局面积,但是由于在共享节点处的增加的电容可能降低速度。如果合乎设计,也可以通过使用适当的选择晶体管将电流引导到作为适当的节点X,而对于读出/写入操作之一使用元件内电流源,对于其它操作使用元件外电流源。在权利要求书中,术语“电流源”意思是表达可以从其中汲取电流的节点的概念,因而,例如,如果在存储器元件内存在供应有电流的节点,那么所述节点可以为电流源,即使其是由在存储器元件自身外部的晶体管供应电流也是如此。

行选择

现转向图6B,将行选择晶体管M2添加到图6A的基本构造上。耦合到M2栅极的Row_Sel线路的控制电流源C1是否耦合到节点X。因为多达一半的晶体管使其源极/漏极连接到节点,所以以此方式通过外部(列)电流源所观察到的电容降低。由于降低的电容,所以这种方法提供了较快的读取和写入。

图7为耦合到pFET电流源的差分存储器的电示意图,并且所述选择晶体管(S0、S1)根据本发明实施例与nFET一起建构。所述存储器通过将Vdd拉升(到大约5V)、通过设定其栅极电压到Vdd以开启选择晶体管(S0、S1)之一、并且通过设定其电压到接地以关闭另一个选择晶体管来进行编程。在“开”侧的浮栅晶体管(M0、M1)将经受IHEI,引起其栅极电压降落。在“关闭”侧的浮栅的晶体管(M0、M1)不具有任何通道电流,将其注入降低到可以忽略的级别,并且使其栅极电压仍然大致不变。

在替代实施例中,图7中的选择晶体管可以与pFET一起建构。还可以使用图7中的选择晶体管将阵列中的多个存储器元件从单一读出放大器D1分离。

图8为差分存储器电路的电示意图,其中在根据本发明实施例的浮栅注入晶体管的漏极处控制电流。因为存在两个单独的电流控制,所以在M0和M1中可用单独地控制IHEI。在本实施例中,电流“源”C0和C1可以是电流槽。电流“槽”可以沉降电流,而电流源可以供应电流。

图9为根据本发明实施例的图8版本电路的电示意图。在这个版本中,向偏差0或偏差1施加偏压,并且向其它信号施加0V将写入所述存储器。如果将偏差0设定为偏压电压并且将偏差1设定为0V,那么电流将流过M2和M0,引起M1中的IHEI并且降低FG0上的电压。在这种情况下,将没有电流流过M3和M1,因此在M1处的注入率会远小于在M0处的。而当将偏差1设定为偏压并且将偏差0设定为0V时,则会是相反情况。在读取期间,可将偏差0和偏差1两者设定为0V,来防止电流绕过读出放大器。

关于图6A、6B、7、8和9的存储器的读取操作类似于图3所述的。

通过将pFET读取晶体管(M2、M3)添加到如图10电路中的每个浮栅来分离编程和读取功能。图10为根据本发明实施例的示意图,其包括与每个浮栅相关的pFET读取晶体管。这项修改允许使晶体管的漏极电压(Vinj)低于接地,而在写入期间加速IHEI处理。这也会增加差分读出放大器设计上的弹性。

图11为类似图10的本发明实施例的示意图,但是其包括行选择晶体管(S2、S3,这些将通过“EN”信号选择性地激活),以从差分读出放大器隔离存储器元件。这项修改允许多个存储器元件共享单一差分读出放大器D1。视需要,选择晶体管(S2、S3)可以为nFET(如图中所示)或pFET。

图12为根据本发明一个实施例的图11的方框12内所含有的电路的替代部分的电示意图。在这个替晶代实施例中,选择晶体管(S2、S3)为pFET,且与pFET读取体管M2、M3呈不同排列。但是效果相同。

图13为建构双向穿隧的本发明实施例的电示意图。在本实施例中,使用双向Fowler-Nordheim(FN)穿隧而非FN穿隧和IHEI来进行编程/擦除。为提供单井CMOS制程中的双向式穿隧,添加控制栅极CG0、CG1(在本例中pFET具有短路的源极、漏极和井(这也是一款MOSCAP),其电容性耦合到浮栅,允许浮栅电压改变。为了编程存储器,将MOSCAP控制栅极之一设定为高电压(Vcg为大约10V),并且将穿隧接合设定为接地。通过使用相对于穿隧接合电容和任何寄生电容的大的控制栅极MOS电容器,通过电容性耦合和从该浮栅上的穿隧接合的电子隧道,使浮栅电压接近Vcg。为擦除存储器,使穿隧接合升高(到大约10V),且将控制栅极拉到接地。电子穿隧离开浮栅而到穿隧接合。图13中的控制栅极也可以适用于如在图3中说明的存储器,因为其可以向浮栅加偏压以最大化写入效率。在一个实施例中,可以将图13所示的MOSCAP安置在单独的n井中。或者,这两个MOSCAP也可以共享单一n井以节省面积。为了节省更多面积,以降低的MOSCAP电容为代价,其可以如存储器中的其它pFET(M0和M1)一样放置在相同的n井中。或者,给定足够电容的M0和M1可以接管CG0和CG1的功能,接着再将其忽略。

图14为基于图13的本发明替代实施例的电示意图。在这个版本中,将读出放大器添加到图13的存储器上,并且存储器是以注入而不是以双向穿隧方式写入。如果pFET最初为关,那么浮栅电压可通过电容性耦合而拉低,以推动注入处理的开始。同样,当穿隧完成后,可以通过将浮栅拉高、降低氧化物电压(即,减少穿隧电压和浮栅电压之间的差值)并且连同穿隧电流,来使用控制栅极结束穿隧处理。后面的这个实例要求读出(sensing)和反馈电路,如现在所属领域的技术人员可以容易地设计。在此所用的控制栅晶体管具有与图13中的控制栅晶体管相同的与其n井连接相关的选择。

图15为本发明实施例的电示意图,其中一半的差分存储器是由一行存储器中的所有存储器元件所分享。在图15中的实施例中,每个存储器元件中的差分对的右侧已经被包含以Sel0和FG0作为其栅极的晶体管的单一、共享右侧取代。在本实施例中,将共享存储器元件写入到逻辑0和逻辑1状态之间的一半处,并且每个未共享的存储器元件(在图的左侧)到0状态或1状态是取决于存储值。在读出期间,除一个外(这个是用作位选择),将为了所有x而将Sel1_x设定为Vdd。使用右侧作为中性参考,差分读出放大器将判定在图左侧的选择浮栅晶体管是否已被写到0状态或1状态。一项对这个存储器的可能修改是除去图上部所示的电流源。在这种情况下,将所有选择晶体管的源极连接到Vdd。虽然电路不再像真实差分对那样运作,但是差分读出放大器仍然会将参考电流(来自电路的FG0支脚)与数据电流(来自电路的FGx支脚)相比较。或者,可以存在两个共享的存储器元件(取代图中的Sel0和FG0装置),其中之一被写入到逻辑0状态,并且另一个被写入到逻辑1状态,使得在读取操作期间将逻辑0和逻辑1电流均分,以产生在逻辑0和逻辑1之间一半的值。或者,可以存在任何数目(高达N个)的读出放大器,以允许一次地读取在相同行内的多个存储器元件。在读出期间中,同时将复数个Sel1_x线路降到低电压,仅提供那些存储器元件并且允许多位读取。在构造中可能要求一个电流反射镜(current mirror)而不要求偏压晶体管,以为每个位制成所述参考电流的复本。

图16为本发明实施例电示意图,其通过添加一对浮栅晶体管(M2、M3)以监视穿隧处理的结束来修改图14的版本。通过施加适当的Tun_done_Vdd,所属领域的技术人员现在将了解由电路产生的TunDone0和TunDone1信号可用于启动和/或关闭该穿隧处理。这项设计特别适用于确保该穿隧不会完全关闭存储器中的任何pFET浮栅晶体管。

图17为本发明实施例的电示意图,其说明如何在穿隧期间使用反馈来将少量的IHEI明确地施加到存储器,以预防存储器的过穿隧。随着浮栅(FG0或FG1)的电压增加,增加的电流量就将流过注入晶体管(M2、M3)。最终结果是,当浮栅已经穿隧到其高电压时,由IHEI添加到浮栅的电子数量将等于并且与由穿隧除去的电子数量相对。在这种状态下,浮栅电压稳定。调节电路的谨慎的设计允许由设计人员确定最终浮栅电压。(主要取决于图中所示的Vtrip电压(Vtrip0、Vtrip1)这种方法可以确保存储器绝不会完全关闭,并且允许确保大致与穿隧速率失配、IHEI失配、装置失配和其它操作条件无关的擦除处理。

图18为呈现图17存储器的简化的本发明实施例的电示意图。所述Read_not信号用于将存储器配置为相对写入/擦除的读取模式。在写入/擦除期间,关闭Read_not晶体管M4,将存储器元件分离成两个半元件,并且简化写入/擦除。在读取期间,开启Read_not晶体管M4,并且两个电流源M2和M3结合以构成单一电流源,其供应图17中的I偏差_read的对等物。在注入期间,将S0和S1用作选择晶体管,并且在穿隧期间则用作电流控制器。(其承担图1中M3和M4的相同角色)

图19和20为本发明实施例的电示意图,其说明了可以在注入晶体管的漏极侧控制电流。图20的实施例具有控制写入和读取电流的明确nFET电流槽M2。SEL_0和SEL_1对图6A的存储器中的相同信号具有类似功能。用于这个存储器的差分读出放大器必须接受与用于上文呈现的存储器的放大器相比较呈反极性的电流。注意,如图10中,当读取和写入功能分离时,也可以施加这种形式的电流控制。

实例存储器

现转向图25,其说明了新颖存储器128。存储器128在节点130具有离出存储器元件偏流,其充当用于存储器128的电流源。存储器的左侧和右侧132和134各自分别包含选择晶体管(在这里是一个pFET)S0、S1,其分别地将该电流源节点130分别地耦合到浮栅电荷注入晶体管M0、M1的源极(在这里展示为pFET)。提供穿隧接合电路T0、T1(其为可选的并且可以如上文所述来构造)以分别地从浮栅FG_0和FG_1除去电子。M0、M1的漏极分别地耦合到节点136、138,并且这些各自分别地耦合到写入电路W0、W1,并且耦合到差分读出放大器电路143的差分输入140、142。为了读取这个存储器元件,可以通过在节点144发出Row_Sel信号,并且通过例如所说明的偏流电路146对节点130施加偏流,来选定含有存储器元件的行(一般为存储器元件的二维阵列的一行)。接着使用差分读出放大器电路143读取选定存储器元件的内容。通过在节点144发出选定所述行的Row_Sel信号并且对节点130施加偏流,来完成写入。通过使电子注入分别浮栅(FG_0或FG_1),来开启左侧写入电路W0或右侧写入电路W1,以将分别的0或1(或视构造而相反)写入到存储器128。以这种方式,将相同的晶体管用于读取和写入两者,并且如果需要,写入电路、差分读出放大器电路与电流源电路可以位于存储器元件的外部,并且由大量增加密度的不同存储器元件所共享,如所属领域的技术人员现在将完全了解。

现转向图26,其说明了存储器148,所述存储器148与图25的存储器128的不同之处在于由Row_Sel信号所控制的行选择晶体管被安置在电流源节点130和节点131之间,而其又会被耦合到选择晶体管S0、S1的源极。这项改进降低由其中并未发出Row_Sel的存储器元件的电流源电路146所观察到的电容。降低的电容可以改进性能,代价是每个存储器元件一个单一额外晶体管。所述存储器的操作基本上与图25的存储器的相同。

现转向图27,其说明了存储器150,所述存储器150与图25的存储器128的不同之处在于电流源电路152被安置在存储器150内并且耦合到电流源节点130。为读取存储器,如前文所述使用Row_Sel来选定行,对偏压晶体管的栅极(在这里是一个pFET)156的节点154施加电压偏压,并且通过差分读出放大器电路143来测量输出。通过使用Row_Sel来选定所述行、对节点154施加偏压并且开启两个写入电路W0、W1中之一,来执行写入。根据本版本,对于整个存储器阵列,施加到节点154的偏压信号可以是整体净值(global net)。将电流源晶体管156安置在存储器元件自身内,可以降低充电以完成读取和写入所需要的电容,因而,实现改进的性能。存在一个可能或不能展出各种存储器应用的困难的与本实施例相关的不利。从存储器元件匹配到存储器元件的电流源将不足,因为每个存储器元件将具有其本身的电流源晶体管156,并且其倾向于因装置而异导致较多变化的小面积装置。如果必要,在特别应用中可以通过运用已知的匹配技术而得以克服,而代价是增加电路复杂性和/或面积。

现转向图28,其说明了存储器160,所述存储器160与图25存储器128的不同之处在于省略了电流源节点130,而替代地提供了一对的独立电流源162、164(其可以是晶体管或其它适当的电流源装置或耦合到其它电流源的导体)。选择晶体管S2(在此为一pFET)具有耦合在节点166和168之间的源极和漏极,用于耦合和去耦合节点166和168。这样,视施加到选择晶体管S2的栅极的信号Diff_Sel_b状态而定,允许存储器元件同时耦合到电流源162和164两者,或是存储器右侧和存储器左侧仅耦合到其分别的电流源162、164。以这种方式,可以通过Diff_Sel_b信号去耦所述侧而独立地(且因而为单端地)且同时地写入该存储器元件的两侧。通过如前文所述使用Row_Sel信号选定行、启动电流源162和164、在选择晶体管S2的栅极上发Diff_Sel_b信号(以耦合存储器元件的右侧和左侧),并且通过差分感测放大器143读取存储器来完成读取。通过使用Row_Sel选定行、启动电流源162和164、在选择晶体管S2的栅极上解发Diff_Sel_b信号,并且使用写入电路W0和W1中之一或两个来将信息写入到存储器160,来完成写入。

在本应用中的开关S2很重要,因为其允许将差分存储器元件改变成两个单端存储器元件。通过闭合开关S2,所述存储器为差分式。应用包括差分读出,其中基于浮栅电压,可以将电流从存储器元件的一侧导向到存储器元件的另一侧。在这种模式下,尽管可能存在两个(如,在这个版本中为162、164),但是电路仍会像存在单一电流源一样操作。通过打开开关S2,存储器元件会被分成两个单独的半个元件。现在可以在一个时间写入存储器元件的一侧上,而在另一个时间写入存储器元件的另一侧上,或同时独立地写入存储器元件两侧上,而完全不影响另一侧。以除错模式从存储器的一侧一次性读出电流以便确定每个浮栅电压也是可能的。

现转向图29,其说明了存储器172和支持电路。这个存储器与图28中所说明不同之处如下。电流源162、164被耦合到选择晶体管S0和S1的源极(节点176和178)。同样耦合到那些节点的是差分读出放大器电路174。注入晶体管M0、M1的漏极被耦合到节点180,以及电流源182和写入电路184。为了读取存储器,发出Row_Sel以选定行、施加来自电流源182的偏流、关闭电流源162和164,并且通过差分读出放大器174来读取存储器状态。为了写入存储器,如前文所述通过Row_Sel信号选定行、关闭来自电流源182的偏流、通过电流源162与164中之一施加偏流,并且启动写入电路184来写入存储器。这个存储器可以同时写入右侧和左侧两者(开启电流源两者),并且相对于呈现在本文其它设计中使用两个而仅要求一个写入电路。

现转向图30,其说明了存储器186,所述存储器186类似于图29,但是具有稍微不同的支持电路。在这个版本中,将单一写入电路184耦合到节点180,而未将额外电流源耦合到所述节点,如图29实施例。使用电压输入差分读出放大器电路174′来读取存储器。为了读取存储器元件,如前文所述发出Row_Sel信号、将偏流施加在存储器元件两侧上,存储器的每一侧充当后随者的独立源极。通过差分读出放大器174′读取电压。为写入存储器,发出Row_Sel信号、开启电流源162、164之一或两个,并且启动写入电路184。

现转向图31,其说明了根据本发明的存储器190的另一个实施例。这个存储器具有一对的浮栅注入晶体管M0、M1,(如果需要)其浮栅可以如上文所述耦合到穿隧接合T0、T1。写入电路W0、W1分别耦合到M0、M1的漏极,而这些漏极也可以包含差分读出放大器174的输入。电源晶体管(pFET)S0和S1分别地使其栅极耦合到V偏差,并且使其源极耦合到VS_0和VS_1。S0和S1的漏极被耦合到M0和M1的源极,并且通过选择晶体管S2(在这里为pFET)而交叉耦合,所述选择晶体管S2的栅极由Diff_Sel_b信号所控制。VS_0、VS_1、Diff_Sel_b和V_偏差是在线路上传送的信号,所述所有线路被共享在存储器元件的二维阵列的行存储器元件之中。通过设定VS_0和VS_1到Vdd、将具有V-偏差的偏压施加到电源晶体管S0和S1、发出Diff_Sel_b以耦合存储器190的左和右侧,并且使用差分读出放大器174读取存储器,来完成读取。为了写入存储器,设定VS_0和VS_1到Vdd、以V_偏差施加偏压、解发Diff_Sel_b以隔离存储器190的左和右侧,并且启动写入电路W0、W1之一或两个以写入存储器的内容。本实施例使用存储器(S0、S1)内的电流源用以更快操作,可以同时写入存储器的两侧(即,浮栅FG_0和FG_1两者),并且对于图30的实施例仅使用一个额外的晶体管(S2)。

图32中说明了图31实施例的一个变体。在图32实施例中,浮栅注入晶体管包括控制栅极(并没有明确展示实施例中不要求的,但是对于任何存储器其总为一个选择)。控制栅极终端C0、C1分别地耦合到电源晶体管S0、S1的源极,且分别地示意性表示为电容器194、196。以这种方式,将控制栅极连接到VS_x信号线路有助于有效布线,因为VS_x担任控制栅极输入(对Cx),和用于电流源的电源(Sx)两者(x适当地表示0或1)。将VS_x设定为低不仅会切断存储器内的电流源,还会将浮栅FG_x拉到较低电压,以减少写干扰。注意,并不要求控制栅极信号与VS_x信号结合,且可能修改本文描述的存储器的其它版本以运用这个特征。其它方面,存储器192以图31的存储器190的相同方式操作。

在图33中说明了图31实施例的另一种变体。在图33的实施例中,VS_x信号不清楚,并且存在施加到节点200的代替标注为VS的信号,所述节点200连接到电源晶体管S0、S1源极。本实施例节省第二VS线路的布线,但是抑制了和图34一起图32的技术的使用。这是因为一旦VS_0和VS_1合并为一个信号VS,如图33,就无法独立控制图34的两个控制电容器。其它发面,存储器198以图31的存储器190相同方式操作。

多位存储

一种在诸如本文所描述的那些差分存储器结构中存储多个位的信息的方式是在存储器的一侧上写入参考并且在所述存储器的另一侧存储许多级之一。通过添加各种偏移到读出系统,并且确定要求多少偏移以使读出改变状态,可以收回存储的多位值。这是一个二位系统的实例:

1.将0.5值写入到A侧;

2.将下列{1,0.75,0.25,0}中任何一个写入B侧;

3.在读出期间,通过偏移{0,+/-3/8}来比较A侧和B侧;

4.根据第一次比较结果,将确定所存储的值为{1,0.75}之一或为{0.25,0}之一。在这个二位的情况中,第二次比较的偏移将列表缩窄到一个值。通常,通过不同偏移来继续进行比较,直到确定出所述值为止。每次比较产生一个位的信息。

为了施加偏移,可以将电流添加到存储器或可以使用电容性耦合的控制输入节点,以直接地移动浮栅电压。

在另一个实例中,将对存储器结构的两侧写入不同值,对其进行一些运算(诸如减法),接着取得结果并且将其与某些固定的参考集合相比较。

边界读取

在最终客户送货之前的品质控制处理通常要求存储器能够适当地存储并且可靠地收回所需要的值。因而,用于检验所述限界并且通过其所述存储器可以读取存储值的方法是很有价值的。在这个揭示案中所述的存储器元件在设计和进行所述检验时展出某些有趣的挑战。问题在于在这里呈现的多数存储器所用的差分读出机制是如此的牢固,使得即使非常小的差分浮栅电压也将可以产生正确操作。目标是对于最好的保持性和真正牢固设计能够确保相当大的差分浮栅电压。根据第一种基本方法,在图34中说明了存储器128′。除了明确要求控制栅极之外,存储器128′在大多数方面与图25的存储器128相同。为了检测边界,使用下列程序:

在存储器中存储零......

1.如果存储器中存储零,那么FG_0电压应所述低于FG_1电压;

2.向control_gate_0的节点C0施加电压,所述电压比施加到control_gate_1的节点C1的电压高出某想要的很小量;

3.由于电容性耦合,FG_0的电压相对于FG_1的而增加,所以更难正确地读出存储器的内容;和

4.如果在这些条件下存储器仍然正确地读出,那么FG_0和FG_1之间的电压边界是如所要的。

在存储器中存储一......

1.如果在存储器中存储1那么FG_0电压应所述大于FG_1电压;

2.向control_gate_0的节点C0施加电压,所述电压比施加到节点control_gate_1的节点C1的电压小某想要的很小量;

3.由于电容性耦合,FG_1电压相对于FG_0而增加,所以更难正确地读出存储器的内容;和

4.如果在这些条件下存储器仍然正确地读出,那么FG_0和FG_1之间的电压边界是如所要的。

这项技术可用于本文所述其它版本的存储器。另外,可以接受一个特定的测试协议,为在芯片上或阵列中的存储器元件提供控制栅极用以执行上文所述的测试,而无需对所有的提供控制栅极,并且对一些或所有控制栅极供应的存储器元件的测试可以认为是在不存在对芯片上的所有存储器元件的个别测试时足够验证特定芯片。同样注意本质上并不要求“控制栅极”,仅低泄漏电容器,每个具有一个耦合到(或为)浮栅的终端。要求电容器是彼此独立的,使得可以独立地操纵浮栅。

现转向图35,其说明了替代边界读取方法。在大多数方面存储器128″类似于图25的存储器128。差别是提供了对读出放大器输入(节点136、138)增加/减少偏移电流的机制。根据图35中所说明的实施例,提供了边界电流源(或槽)电路202。开关204和206是独立可控制的,以将电路202耦合到节点136或节点138(在这里有时又称作“读出节点”,因为其耦合到差分读出放大器143的输入)。将电路202所提供的电流设定或设计用于存储器元件的适当电流边界。如果随着电流从读出放大器电路143的输入增加/减少,存储器仍然正确地读出,那么存在适当边界。如果不是,即,存储器元件输出改变状态,那么接着存在不当边界和潜在缺陷。例如,这可以通过下列程序而完成:

1.在存储器128″中存储0,并且V(FG_0)小于V(FG_1)。这意味着穿过M0的源极-漏极电流I0大于穿过M1的源极-漏极电流I1。为了使存储器元件具有适当的电流边界,I0应所述比I1大一个预定边界。

2.闭合开关204以从节点136处“窃取”预定量的电流。这将减少从节点136流入差分读出放大器143的电流。

3.如果读出放大器的状态没有改变,那么存在适当的电流边界。如果确实有改变,那么限界为不当的并且存在潜在缺陷。

或者:

1.存储器128″中存储0,并且V(FG_0)大于V(FG_1)。这意味着穿过M0的源极-漏极电流I0小于穿过M1的源极-漏极电流I1。为了使存储器元件具有适当的电流边界,I0应所述比I1小一个预定边界。

2.闭合开关206以从节点138“窃取”预定量的电流。这将减少从节点138流入差分读出放大器143的电流。

3.如果读出放大器的状态没有改变,那么存在适当的电流边界。如果确实有改变,那么边界是不当的并且存在潜在缺陷。

降低写干扰

现转向图36,其展示用于0.25微米制程装置的写干扰对栅极到漏极电压曲线图。当栅极处于相对高电压而漏极处于相对低电压时,就会出现写干扰。标记为“A”的数据表示在横轴上展示的栅极到漏极的电压的范围内的在竖轴上所展示的以安培计的热电子栅极电流(写入电流)。标记为“B”的数据集合表示带对带穿隧引入的栅极电流(写干扰)。写干扰与在其它存储器元件的写入操作期间的关闭状态下的存储器元件的漏极处的带对带穿隧电流有关。写干扰可导致数据讹误,因此需要将其最小化。如可以观察到,较低的栅极到漏极电压导致较低的写干扰电流,并且写入电流与写干扰电流之间的差别的幅度将随着降低的电压而显著增加。数据集合A表示井电压Vwell原来是3.3伏特,栅极电压Vg原来是2.2伏特而源极电压Vs原来是3.3伏特的数据。数据集合B表示Vwell=3.3伏特、Vg=2.2伏特和Vs=1.5伏特的数据。如从图36可以观察到,在0.25微米制程中,在5.25伏特处的写入电流比写干扰电流高六个阶的幅度。随着制程大小继续缩小,估计这个边界在0.13微米制程里将缩小到4大约阶的幅度。降低栅极漏极将把所述结果转移到图左侧,因而将写干扰电流降低到写入电流的很小部分。

现转向图37,其展示了非常类似图25的存储器128的存储器208。这个存储器包括分别耦合到FG0与FG1的电容器210、212,其分别地包括节点C0和C1。例如,这些可以是控制栅极。

为了降低栅极-漏极电压,可以使用下列程序:

(control_gate_x指的是control_gate_0和control_gate_1;Cx指的是C0和C1)

1.对于选择行(所写入行),将节点Cx的control_gate_x设定为高;

2.对未选择行(未被写入行),将节点Cx的control_gate_x设定为低;和

3.电容器将未选择行中的的浮栅耦合到较低电压,因而,降低其栅极-漏极电压,依次,降低其带对带穿隧电流,进而降低写干扰。

注意这个概念现在可以适用于本文所描述的各种存储器构造,而不限于仅使用在诸如图37的特定存储器中。

NVM阵列

图38、39和40为说明可以根据本发明实施例制造的NVM阵列的实例的电示意图。现转向图38,其展示了图32中所描述的存储器阵列。在本实例中,VS_0和VS_1导体充当电容器输入,根据本发明的图21和22的设计以pFET来建构穿隧结合,并且特定行内的所有穿隧接合通过导体连接在一起(例如V_tunnel<1>)。将分页定义为一组共享通用的擦除信号并且因此可以同时擦除的存储器元件。这个实例具有两个分页。分页0在阵列底部含有四个位,而分页1在阵列顶部含有两个位。可以通过将不同数目的行的穿隧结合耦合到一起来构造所述分页的数量和尺寸。

现转向图39,其展示了图25中所描绘的存储器阵列。因38的为在本实施例中每列仅要求一个电流源,所以可以提供较少的导体布线,与图相比显著降低了电路的复杂度。这种设计的缺陷在于通用电流源导体上相对大的电容导致较慢的读取时间。然而,对于整个存储器列共享单一电流源具有好处,因为在阵列中其可以较大并且其数量可以较少,提供了较好的内部匹配。

现转向图40,其展示了图34中描绘的存储器阵列。根据本发明的这个实施例,如上文所论述的,每列存在一个电流源,并且使用电容器(控制栅极或其它)提供边界读取能力并且减少写干扰。

重要的是要注意,图38、39和40中并不包含本文呈现的存储器阵列构造的广泛集合。所述实例清楚地说明,所属领域的技术人员可以根据本文呈现的存储器来设计实际上任何尺寸的功能性存储器阵列。

现转向图44,其说明了诸如在各个图中标注为“W0”和“W1”的样品负极性电荷泵写入电路。将输出连接到读出节点之一。如果需要,那么二极管D1可以是二极管连接的pFET。电容器C1可以是MOSCAP或任何其它适当的电容器。在本实施例里,栅极G1可以是与门,并且当发出“ENABLE”和“CLOCK”时,电路使存储器被写入。所属领域的技术人员现在将认识到可以使用任何数量的不同电路来完成相同的基本功能。

现转向图45,其说明了一个样品现有技术读出放大器电路。本实施例使用nFET T1、T2、T3和T4。读出输入S+和S-接收来自差分存储器的分别读出节点的电流I+和I-。放大器输出是在节点V+和V-。如果I+>I-,那么V+>V-;如果I+<I-,那么V+<V-。所属领域的技术人员现在将认识可以构建任何数量的替代电路(包括那些以pFET而不是nFET制造的)以达到相同的基本功能。

外部注入

虽然不常见,但是根据本发明所构建的NVM用放置在浮栅上的某位准的电荷(和相对高的栅极电压)的制作复原。所述构想是将施加的电压以外部方式连接到存储器的漏极和/或源极,以便使其经受IHEI和/或带对带穿隧。这适用于下列情况,其中存储器用将其栅极设为“关”,使得内部电荷泵因为在注入装置中不存在漏极-源极电流而不能引起大量的IHEI的制作制程而得以复原。

现转向图41,一种方式是在负电压下切换到存储器的漏极。可以使用开关通过针来选择性设定漏极电压(称为V_External_Inject)。通过外部施加的电压,可以将漏极设定到非常低的电压(在0.18μm制程中为大约-5到-4伏特),这将引起带对带穿隧。

根据图41,通过一对开关222、224将每列的读出放大器和写入电路220耦合到标注V_external_inject的外部电压源,这将降低相对于浮栅的注入晶体管的漏极的电压,而从浮栅上的漏极引入带对带穿隧以“分开(unstick)”存储器。这是以下列程序建构的:

1.向V_External_Inject线路施加相对低的电压。

2.闭合开关222、224,以将V_External_Inject耦合到存储器的浮栅pFET的漏极(这可以按列接列的基准,或如果需要同时按阵列宽度来完成)。

3.当位“分开(unstick)”时等待。

4.打开开关222、224来终止处理。

5.通过差分读出放大器来测量位电流,以检验适当操作。

根据图42中说明的实施例,pFET可以用作开关222、224。在这种情况下,将开关222和224建构为pFET,并使其源极耦合到存储器读出线路226、228。需要另一个外部施加的信号:External_Inject_Gate。这个信号必须比V_External_Inject低至少一个Vt,同样考虑对pFET的体效应,因为其井电压与其源极电压并不匹配。这需要打开开关222、224。井本身(由External_Inject_en_b驱动)应从0V(启动外部注入模式)切换到Vdd(关闭外部注入模式)。需要这项切换以降低pFET中的pn接合上的电压。否则可能发生故障。根据本发明的一个实施例,将External_Inject_Gate设定为大约-5伏特,将V_External_Inject设定为大约-3伏特,并且将External_Inject_en_b设定为大约0伏特。

如所属领域的技术人员将认识到,可用其它方式达到相同目的。例如,将IHEI晶体管上的“源极”电压设定成非常高同时使其漏极保持低(接地或更低)可具有相同的最终结果,但是不是很容易建构。注意在正常操作期间,“源极”侧在这里可实际上是晶体管的“漏极”侧。

现转向图45,其展示了图44中说明的构想的更特定的建构。在这个版本中,将开关222和224建构为pFET,使其源极耦合到存储器读出线路226、228。将其井耦合到标注External_Inject_en_b的线路,将其栅极耦合到标注External_Inject_Gate的线路,并且使其漏极耦合到标注V_External_inject的线路。在一个实例中,将External_Inject_Gate线路设定成大约-5伏特,将V_External_inject线路设定成大约-3伏特,并且将External_Inject_en_b线路设定成大约0伏特。

穿隧接合布局

本发明中期待的大多数阵列在许多存储器元件之中共享穿隧接合。一些穿隧接合要求其本身的n井从支持其余存储器的n井分离。因为n井与n井的间隔由于制造的约束而倾向于相对较大,所以使穿隧接合n井交错可以提供有效布局。当使用这个方案时,存储器分页尺寸是两个存储器元件行的数倍。图43中说明了根据本发明一个实施例的穿隧接合布局的实例。这个实例展示了用于4列、3行、2分页的存储器阵列的n井。线路230-276是浮栅,如所说明的,其使主存储器n井278、280与对应的穿隧接合n井282、284耦合。

总结

在NVM应用中,pFET浮栅晶体管具有优于nFET的若干优点:

1.p通道浮栅MOSFET可以以比用于n通道浮栅MOSFET的典型的电流小的通道电流,将电子注入到其浮栅上。从而,基于pFET存储器的电荷泵(晶片上通常要求的以便提供超过用于擦除和写入操作的Vdd的电压的电路)通常消耗比那些为nFET存储器设计的能量少的能量。

2.pFET中的IHEI主要产生通道热电子,然而nFET中的等效机制(通道热电子注入或CHEI)产生通道热电子洞。因为热电子对栅极氧化物的损害远小于热电子洞,所以与nFET相比,pFET具有减少的氧化物磨损和更好的编程/擦除循环持久性。

3.离出具有p+掺杂栅极的浮栅pFET的位垒高度会大约是4.2eV(参看图2),比较而言用于具有n+掺杂栅极的nFET大约是3.04eV。从而,nFET中的泄漏电流比pFET中的小,因此,具有相同氧化物厚度的pFET浮栅存储器的数据保持性特征好于nFET浮栅存储器的。结果,pFET存储器可使用较薄的栅极氧化物,诸如在标准双栅极氧化物CMOS制程中所看到的70(通过3.3V I/O装置)。相比较之下,基于nFET浮栅晶体管的存储器需要额外制程步骤以制作较厚的栅极氧化物(最小厚度一般为80)。

在NVM应用中,差分存储器具有优于单端存储器的若干优点:

1.差分存储器的逻辑状态是由两个浮栅上的电荷差值所确定的。当“0”浮栅上的电子比“1”浮栅的电子多时,读出电流主要通过具有“1”栅极的晶体管而穿过,并且反过来也是如此。从而,虽然相对于n井电压两个浮栅带负电,但是仍有可能区别逻辑1与逻辑0状态。这个特性意味着任一侧都不具有无法被随后开启和注入的如此高栅极电压。

2.电荷泄漏机制倾向于引起“1”和“0”浮栅上的电荷沿相同方向泄漏(即,双方使电荷泄漏到其栅极上,或沿共同方向离出其栅极)。差分存储器具有共模抑止,意思是其对浮栅之间的电压差而不是对其电压绝对值敏感。从而,共模电荷泄漏并不会影响存储的逻辑状态。因此,差分存储器的保持用区分性优于单端存储器。

3.读取操作是使用区别差分存储器的两个半部之间较具有导电性的路径的原理。读取存储器时,只要差分读出放大器具有可以确定电流走哪条路径来穿过存储器的足够敏感度,就可使用任意小的尾端电流。从而,本文描述的存储器允许低能量存储器电路。

4.因为差分存储器的两个半部通常会在晶片上紧密靠近,所以其与晶体管特征适当匹配。例如,两个邻近的浮栅晶体管的栅极氧化物厚度比两个间隔很远的晶体管的更紧密匹配。结果,差分存储器设计对于可以影响单端存储器的读取精确度的晶体管变化不是很敏感。

5.差分存储器是自参考式,意思是存储器一侧是另一侧的参考。从而,差分存储器排除了对单端存储器中典型的对晶片上或外的电流或电压参考电路的精确度的需要。这项自参考特性可以保持,无论存储器中的每个元件是否是差分的(如图3),或是多个存储器元件是否共享单一半存储器元件(如图15)。

6.由于差分存储器是自参考式,所以其具有优异的共模抑止。共模抑止为差分存储器提供比单端存储器更好的对电源和温度波动的抗扰性。

7.差分NVM元件具有类似于CMOS设计中所熟知的SRAM元件的差分输出。从而,差分NVM元件可以使用在SRAM设计中常见的(为所属领域的技术人员所熟知,并且为了避免使本揭示内容过于复杂在此不还描述)的超快差分读出放大器和位线路预充电技术。结果是与单端存储器元件相比,差分NVM元件允许更快的读出同时能量消耗较低。

总之,基于pFET浮栅晶体管的差分存储器具有许多优于单端存储器、nFET存储器和差分nFET存储器的优点。其在逻辑CMOS中提供低能耗、高速度和高可靠性的NVM。

虽然已展示并描述了本发明实施例和应用,但是得益于本揭示内容的所属领域的技术人员将容易了解多于上文提到的许多修改都是可能的而不会脱离本文的发明概念。

例如,请注意,虽然本发明的观点可以实施在单一井、单一多制程中并且将与低电压制程(例如,<=3伏特)一起运作,但是本发明并不受其限制,而且本发明可实施在支持多个多晶硅层、多个井和/或较高(或较低)电压装置的制程中。

此外,本文使用的n井概念不仅仅涵盖常规n井装置,而且还涵盖增加装置的可靠栅极-漏极和漏极-源极电压的NLDD(N型稍微掺杂漏极)装置和其它稍微掺杂或隔离的结构,使得其实际上在这个方面可以像常规n井装置一样运作。其还可以以相同的薄膜结构建构在基板上的薄膜中。

在本发明的一个实施例中,可整体地或部分地使用电流槽装置用作上文所述的电流源装置的替代物。

在本发明的另一个实施例中,如上文所论述的选择晶体管S0、S1、S2等如果需要通常可以以nFET而不是pFET建构。

最后,因为可谨慎地并且精确地写入浮栅上的电荷,所以可以使用与较高清晰度读出电路耦合的、现有技术中已知的这些结构,来存储每个存储器元件的多个数位。通过本文所揭示的存储器,例如使用图15的存储器将直接存储四个不同位准的电荷。可以存在分别地存储、和

的三个参考半对FG0_A、FG0_B和FG0_C以代替存储电荷值的单一参考半对FG0。在读出期间,差分读出放大器依次地比较存储在一个浮栅上的值,如FG1,依次是FG0_A、FG0_B和FG0_C。如果存储在FG1上的值小于FG0_A上的,那么FG1存储零。如果FG1上的值大于FG0_A但是小于FG0_B,那么FG1存储一。如果FG1上的值大于FG0_B但是小于FG0_C,那么FG1存储二。如果FG1上的值大于FG0_C,那么FG1存储三。通过存储四个可辨别的电荷值,每个半元件持有两个位的信息。这种方法可清楚地扩展到每个存储器存储三个或更多位,仅受写入、保持和读取处理精确度的限制。因此,本发明仅限制于上述权利要求书精神。

Claims (83)

1.一种差分非挥发性浮栅存储器,其包含:

一个具有一个第一浮栅的第一pFET浮栅晶体管;

一个具有一个第二浮栅的第二pFET浮栅晶体管;和

一个经耦合以接收来自所述第一pFET浮栅晶体管和所述第二pFET浮栅晶体管的电流的差分读出放大器。

2.根据权利要求1所述的存储器,其还包含:

一个经耦合以从所述第一浮栅除去电子的第一穿隧接合;和

一个经耦合以从所述第二浮栅除去电子的第二穿隧接合。

3.根据权利要求1所述的存储器,其还包含:

用于从所述第一浮栅除去电子的构件;和

用于从所述第二浮栅除去电子的构件。

4.根据权利要求1所述的存储器,还包含:

一个用于将光耦合到所述第一和第二浮栅的视窗。

5.一种差分浮栅非挥发性存储器,其包含:

一个用于存储电荷的第一构件;

一个用于存储电荷的第二构件;

一个用于将电荷添加到所述第一构件的第三构件;

一个用于将电荷添加到所述第二构件的第四构件;

一个用于从所述第一构件除去电荷的第五构件;

一个用于从所述第二构件除去电荷的第六构件;和

一个耦合到所述第一和第二构件的第七构件,其用于读出所述第一构件和所述第二构件中的哪一个存储较大量的电荷。

6.根据权利要求1所述的存储器,其还包含:

一个与所述第一pFET浮栅晶体管串联耦合的第一选择开关;和

一个与所述第二pFET浮栅晶体管串联耦合的第二选择开关,所述第一和第二选择开关由施加到其的信号所控制,以确定所述第一浮栅和所述第二浮栅中的哪一个可以在一定时间内经受电子注入。

7.根据权利要求2所述的存储器,其还包含:

一个与所述第一pFET浮栅晶体管串联耦合的第一选择开关;和

一个与所述第二pFET浮栅晶体管串联耦合的第二选择开关,所述第一

和第二开关由施加到其的信号所控制,以确定所述第一浮栅和所述第二浮栅中的哪一个可以在一定时间经受电子注入。

8.根据权利要求5所述的存储器,还包含:

一个与所述第三构件串联耦合的第八构件,所述第八构件用于控制所述第三构件的操作;和

一个与所述第四构件串联耦合的第九构件,所述第九构件用于控制所述第四构件的操作。

9.一种差分浮栅非挥发性存储器,其包含:

一个具有一个第一浮栅的第一pFET浮栅晶体管;

一个具有一个第二浮栅的第二pFET浮栅晶体管;

一个耦合到所述第一浮栅的一个第一晶体管的第一栅极;

一个耦合到所述第二浮栅的一个第二晶体管的第二栅极;和

一个经耦合以使电流从一个并联的单一节点通过所述第一和所述第二晶体管传递到一个差分读出装置的偏流源极,所述第一浮栅和所述第二浮栅上的电荷通过所述各自第一和第二晶体管控制电流的所述流动。

10.根据权利要求9所述的存储器,其中所述第一和所述第二晶体管为pFET。

11.根据权利要求9所述的存储器,其还包含一个经耦合以从所述第一浮栅除去电子的第一穿隧接合,和一个经耦合以从所述第二浮栅除去电子的第二穿隧接合。

12.根据权利要求9所述的存储器,其中所述第一和第二晶体管为nFET。

13.根据权利要求9所述的存储器,其还包含一个与所述第一pFET浮栅晶体管串联耦合的第一选择开关,和一个与所述第二pFET浮栅晶体管串联耦合的第二选择开关。

14.根据权利要求13所述的存储器,其中所述第一选择开关和所述第二选择开关为pFET晶体管。

15.根据权利要求9所述的存储器,其还包含一个与所述第一晶体管串联耦合的第一启动开关,和一个与所述第二晶体管串联耦合的第二启动开关,所述启动开关控制电流流动到所述差分读出装置。

16.根据权利要求1所述的存储器,其还包含:

一个电容性耦合到所述第一浮栅的第一控制输入节点;和

一个电容性耦合到所述第二浮栅的第二控制输入节点。

17.根据权利要求16所述的存储器,其还包含:

一个经耦合以从所述第一浮栅除去电子的第一穿隧接合;和

一个经耦合以从所述第二浮栅除去电子的第二穿隧接合。

18.根据权利要求9所述的存储器,其还包含:

一个电容性耦合到所述第一浮栅的第一控制输入节点;和

一个电容性耦合到所述第二浮栅的第二控制输入节点。

19.根据权利要求18所述的存储器,其还包含:

一个经耦合以从所述第一浮栅除去电子的第一穿隧接合;和

一个经耦合以从所述第二浮栅除去电子的第二穿隧接合。

20.一种用于将信息存储在半导体装置中的方法,所述半导体装置具有一个第一浮栅pFET和一个第二浮栅pFET,所述方法包含:

将电荷放置在所述第一浮栅pFET的一个浮栅上;

将电荷放置在所述第二浮栅pFET的一个浮栅上;

从所述第一浮栅pFET的所述浮栅除去电荷;

从所述第二浮栅pFET的所述浮栅除去电荷;和

测量在所述第一和第二浮栅pFET的所述浮栅上的电荷。

21.一种用于将信息存储在半导体装置中的方法,所述半导体装置具有一个有第一浮栅的第一浮栅pFET和一个有一个第二浮栅的第二浮栅pFET,

所述方法包含:

(1)测量在所述第一浮栅上的电荷;和

(2)测量在所述第二浮栅上的电荷。

22.根据权利要求21所述的方法,其中同时执行步骤(1)和(2)。

23.根据权利要求21所述的方法,其中在步骤(2)之前执行步骤(1)。

24.根据权利要求20所述的方法,其中所述测量是由一个差分读出放大器来执行。

25.根据权利要求21所述的方法,其中步骤(1)和(2)是由一个差分读出放大器来执行。

26.一种用于将多位信息存储在一个半导体装置中的方法,所述半导体装置具有一个第一浮栅和一个第二浮栅,每一个所述浮栅耦合到一个对应第一和第二浮栅pFET的所述栅极,所述方法包含:

将一个具有多个位准之一的第一电荷放置在所述第一浮栅上;

将一个具有多个位准之一的第二电荷放置在所述第二浮栅上;

测量在所述第一浮栅上的所述第一电荷,以确定在其上存储了哪一个位准的电荷;

测量在所述第二浮栅上的所述第二电荷,以确定在其上存储了哪一个位准的电荷;和

基于所述测量第一电荷和所述测量第二电荷,来确定一个多位输出。

27.一种用于将多位信息存储在半导体装置中的方法,所述半导体装置具有一个有一个第一浮栅的第一浮栅pFET,和具有一个有第二浮栅的第二浮栅pFET,所述方法包含:

将一个第一参考电荷放置在所述第一浮栅上;

将一个具有多个预定位准之一的第二电荷放置在所述第二浮栅上;和首先比较存储在所述第一浮栅pFET上的所述电荷和存储在所述第二浮栅pFET上的所述电荷。

28.一种差分浮栅非挥发性存储器,其包含:

一个具有一个第一浮栅的第一pFET浮栅晶体管;

多个第二pFET浮栅晶体管,各自具有一个对应的单独浮栅,并且通过每一个晶体管至少一个选择开关而使其漏极和源极共同耦合;和一个差分读出放大器,其经耦合以接收来自所述第一pFET浮栅晶体管和所述第二pFET浮栅晶体管中的经选择的一个的漏极电流。

29.一种差分浮栅非挥发性存储器,其包含:

一个具有一个第一浮栅并且耦合到一个偏差节点的第一pFET浮栅晶体管;

多个第二pFET浮栅晶体管,各自具有一个对应的单独浮栅和至少一序列选择开关,并且使其源极共同耦合到所述偏差节点,并且使其漏极共同耦合到一个漏极节点;和

一个差分读出放大器,其耦合到所述漏极节点且耦合到所述第一pFET浮栅晶体管的一个漏极,一个选择信号选择所述多个第二pFET浮栅晶体管中的一个。

30.根据权利要求1所述的存储器,其还包含:

一个第一选择晶体管,其经耦合以在一个第一节点与所述第一pFET浮栅晶体管的一个源极之间选择性导电;和

一个第二选择晶体管,其经耦合以在所述第一节点与所述第二pFET浮栅晶体管的一个源极之间选择性导电。

31.根据权利要求30所述的存储器,其还包含:

一个经耦合以在一个电流源与所述第一节点之间选择性导电的行选择晶体管。

32.根据权利要求30所述的存储器,其还包含:

一个经耦合以从所述第一浮栅除去电子的第一穿隧接合;和

一个经耦合以从所述第二浮栅除去电子的第二穿隧接合。

33.根据权利要求1所述的存储器,其还包含:

一个第一选择晶体管,其经耦合以在所述第一pFET浮栅晶体管的一个漏极与一个第一读出节点之间选择性导电;和

一个第二选择晶体管,其经耦合以在所述第二pFET浮栅晶体管的一个漏极与一个第二读出节点之间选择性导电。

34.根据权利要求33所述的存储器,其还包含:

一个耦合到所述第一pFET浮栅晶体管的一个源极和耦合到所述第二pFET浮栅晶体管的一个源极的第一节点。

35.根据权利要求34所述的存储器,其还包含:

一个耦合到所述第一节点电流源。

36.根据权利要求35所述的存储器,其还包含:

一个经耦合以在所述电流源与所述第一节点之间选择性导电的行选择晶体管。

37.根据权利要求36所述的存储器,其还包含:

一个经耦合以从所述第一浮栅除去电子的第一穿隧接合;和

一个经耦合以从所述第二浮栅除去电子的第二穿隧接合。

38.根据权利要求1所述的存储器,其还包含:

一个耦合到所述第一pFET浮栅晶体管的一个源极和耦合到所述第二pFET浮栅晶体管的一个源极的第一节点;

一个耦合到所述第一pFET浮栅晶体管的一个漏极的第二节点;

一个耦合到所述第二pFET浮栅晶体管的一个漏极的第三节点;

一个在一个第四节点与所述第二节点之间耦合的第一偏差晶体管;

一个在一个第五节点与所述第三节点之间耦合的第二偏差晶体管。

39.根据权利要求38所述的存储器,其中所述第一和第二偏差晶体管为nFET。

40.一种差分非挥发性浮栅存储器,其包含:

一个具有一个第一浮栅的第一pFET浮栅晶体管;

一个具有一个第二浮栅的第二pFET浮栅晶体管;

一个与所述第一pFET浮栅晶体管串联耦合的第一选择开关;

一个与所述第二pFET浮栅晶体管串联耦合的第二选择开关,所述第一和第二选择开关由施加到其的信号来控制

一个第一pFET读取晶体管;

一个第二pFET读取晶体管;

耦合到一个共同节点的所述第一pFET读取晶体管的一个源极和所述第二pFET读取晶体管的一个源极;

一个耦合到所述第一浮栅的所述第一pFET读取晶体管的栅极;

一个耦合到所述第二浮栅的所述第二pFET读取晶体管的栅极;和

一个差分读出放大器,其经耦合以接收来自所述第一pFET读取晶体管和所述第二pFET读取晶体管的电流。

41.根据权利要求40所述的存储器,其还包含:

一个经耦合以从所述第一浮栅除去电子的第一穿隧接合;和

一个经耦合以从所述第二浮栅除去电子的第二穿隧接合。

42.根据权利要求40所述的存储器,其还包含:

一个第三选择晶体管,其经安置以选择性地允许在第一pFET读取晶体管的所述漏极与所述差分读出放大器之间导电;和

一个第四选择晶体管,其经安置以选择性地允许在第二pFET读取晶体管的所述漏极与所述差分读出放大器之间导电。

43.根据权利要求42所述的存储器,其还包含:

一个经耦合以从所述第一浮栅除去电子的第一穿隧接合;和

一个经耦合以从所述第二浮栅除去电子的第二穿隧接合。

44.一种差分非挥发性浮栅存储器,其包含:

一个具有一个源极、漏极和浮栅的第一pFET浮栅晶体管;

一个具有一个源极、漏极和浮栅的第二pFET浮栅晶体管;

一个具有一个源极、漏极和浮栅的第一选择晶体管,所述第一选择晶体管与所述第一pFET浮栅晶体管串联耦合以选择性地中断在所述第一pFET浮栅晶体管中的源极-漏极电流;

一个具有一个源极、漏极和浮栅的第二选择晶体管,所述第二选择晶体管与所述第二pFET浮栅晶体管串联耦合以选择性地中断在所述第二pFET浮栅晶体管中的源极-漏极电流;和

一个耦合到一个第一节点的行选择信号源,所述第一节点耦合到所述第一和第二选择晶体管的所述栅极。

45.根据权利要求44所述的存储器,其还包含:

一个经耦合以从所述第一浮栅晶体管的所述浮栅除去电子的第一穿隧接合;和

一个经耦合以从所述第二浮栅晶体管的所述浮栅除去电子的第二穿隧接合。

46.根据权利要求45所述的存储器,其还包含:

一个经耦合以将信息写入所述第一浮栅晶体管的所述浮栅上的第一写入电路。

47.根据权利要求46所述的存储器,还包含:

一个经耦合以将信息写入所述第二浮栅晶体管的所述浮栅上的第二写入电路。

48.根据权利要求46所述的存储器,其还包含:

一个差分读出电路,其经耦合以读取存储在所述第一和第二pFET浮栅晶体管的所述浮栅上的信息的所述值。

49.根据权利要求47所述的存储器,其还包含:

一个差分读出电路,其经耦合以读取存储在所述第一和第二pFET浮栅晶体管的所述浮栅上的信息的所述值。

50.根据权利要求49所述的存储器,其还包含:

一个耦合到所述第一和第二选择晶体管的所述源极的电流源。

51.根据权利要求49所述的存储器,其还包含:

一个通过一个开关而耦合到所述第一和第二选择晶体管的所述源极的电流源。

52.根据权利要求51所述的存储器,其中所述开关由所述行选择信号所控制。

53.根据权利要求44所述的存储器,其还包含:

一个经耦合以向所述第一pFET浮栅晶体管提供电流的第一电流源;和

一个经耦合以向所述第二pFET浮栅晶体管提供电流的第二电流源。

54.根据权利要求53所述的存储器,其还包含:

一个经耦合以选择性地将所述第一和所述第二电流源的输出彼此耦合的选择开关。

55.一种差分非挥发性浮栅存储器,其包含:

一个具有一个源极、漏极和浮栅的第一pFET浮栅晶体管;

一个具有一个源极、漏极和浮栅的第二pFET浮栅晶体管;

一个具有一个源极、漏极和浮栅的第一选择晶体管,所述第一选择晶体管与所述第一pFET浮栅晶体管串联耦合以选择性地中断在所述第一pFET浮栅晶体管中的源极-漏极电流;

一个具有一个源极、漏极和浮栅的第二选择晶体管,所述第二选择晶体管与所述第二pFET浮栅晶体管串联耦合以选择性地中断在所述第二pFET浮栅晶体管中的源极-漏极电流;

一个耦合到所述第一和第二选择晶体管的栅极的行选择信号源;

一个经耦合以向所述第一pFET浮栅晶体管提供电流的第一电流源节点;和

一个经耦合以向所述第二pFET浮栅晶体管提供电流的第二电流源节点。

56.根据权利要求55所述的存储器,其还包含:

一个与所述第一pFET浮栅晶体管相关的第一电容性耦合控制节点;

一个与所述第二pFET浮栅晶体管相关的第二电容性耦合控制节点;

耦合到所述第一电流源节点的所述第一控制节点;和

耦合到所述第二电流源节点的所述第二控制节点。

57.一种用于检测一个存储在一个差分非挥发性浮栅存储器中的值边界的方法,所述存储器具有各自具有一个源极、漏极、浮栅和一个电容性耦合到所述浮栅的控制节点的一个第一和一个第二pFET浮栅晶体管,所述方法包含:

通过将一个第一量电荷存储在所述第一pFET浮栅晶体管的所述浮栅上,和将一个第二量电荷存储在所述第二pFET浮栅晶体管的所述浮栅上,而将一个值存储在所述差分存储器中;

向两个pFET浮栅晶体管中的至少一个的所述控制节点施加一个预定电压;

读取所述存储器;和

比较所述读取的所述结果与所述已知存储值。

58.一种用于检测一个存储在一个差分非挥发性浮栅存储器中的边界的方法,所述存储器具有各自具有一个源极、漏极、浮栅和一个电容性耦合到所述浮栅的控制节点的一个第一和一个第二pFET浮栅晶体管,所述方法包含:

通过将一个第一量电荷存储在所述第一pFET浮栅晶体管的所述浮栅上,和将一个第二量电荷存储在所述第二pFET浮栅晶体管的所述浮栅上,而将一个值存储在所述存储器中;

第一次读取所述存储器;

向所述两个pFET浮栅晶体管的至少一个的所述控制节点施加一个预定电压;

第二次读取所述存储器;和

比较所述第一读取和所述第二读取的结果。

59.根据权利要求57所述的方法,其还包含:

如果所述读取的结果和所述已知存储值相同,那么确定所述存储器为良好。

60.根据权利要求58所述的方法,其还包含:

如果所述第一读取和所述第二读取的结果相同的,那么确定所述存储器为良好。

61.根据权利要求57所述的方法,其还包含:

如果所述读取结果和所述已知存储值不同,那么确定所述存储器为不良的。

62.根据权利要求58所述的方法,其还包含:

如果所述第一读取和所述第二读取结果是不同的,那么确定所述存储器为不良的。

63.一种用于检测一个存储在一个差分非挥发性浮栅存储器中的值边界的方法,所述存储器具有各自具有一个源极、漏极和一个浮栅的一个第一和一个第二pFET浮栅晶体管,所述方法包含:

通过将一个第一量电荷存储在所述第一pFET浮栅晶体管的所述浮栅上,并将一个第二量电荷存储在所述第二pFET浮栅晶体管的所述浮栅上,而将一个值存储在所述存储器中;

以一个具有一对输入的差分电流读出电路来第一次读取所述存储器;

向所述一对输入的的至少一个输入添加一个可能为正或负的预定电流;

第二次读取所述存储器;和

比较所述第一读取和所述第二次读取的结果。

64.一种用于检测一个存储在一个差分非挥发性浮栅存储器中的值边界的方法,所述存储器具有各自具有一个源极、漏极和一个浮栅的一个第一和一个第二pFET浮栅晶体管,所述方法包含:

通过将一个第一量电荷存储在所述第一pFET浮栅晶体管的所述浮栅上,并将一个第二量电荷存储在所述第二pFET浮栅晶体管的所述浮栅上,而将一个值存储在所述存储器中;

向所述一对输入的至少一个输入添加一个可能为正或负的预定电流;

读取所述存储器;和

比较所述读取的结果和所述已知存储值。

65.根据权利要求63所述的方法,其还包含:

如果所述第一与第二读取结果相同,那么确定所述存储器为良好。

66.根据权利要求64所述的方法,其还包含:

如果所述读取结果和所述已知存储值相同,那么确定所述存储器为良好。

67.根据权利要求63所述的方法,其还包含:

如果所述第一读取和所述第二读取结果不同,那么确定所述存储器为不良。

68.根据权利要求64所述的方法,其还包含:

如果所述读取结果和所述已知存储值不同,那么确定所述存储器为不良。

69.一种用于降低安置在一个分成多行的相同存储器元件的阵列中的差分非挥发性浮栅存储器中的写干扰的方法,每个存储器具有各自具有一个源极、漏极、浮栅和电容性耦合到其浮栅的控制栅极的一个第一和一个第二pFET浮栅晶体管,所述方法包含:

选择一个行,在其中写入一个存储器;

向并非所述经选择的行的行中的元件的所述控制栅极施加一个相对低的电压信号;

向所述经选择的行中的所述元件存储器的所述控制栅极施加一个相对高的电压信号;和

将一个值写入所述经选择的行中的存储器中。

70.一种用于选择性地引导电子转移到一个差分非挥发性浮栅极存储器的所述浮栅上的方法,所述存储器具有各自具有一个源极、漏极、和浮栅的一个第一和一个第二pFET浮栅晶体管,所述方法包含:向每一个所述第一和第二pFET浮栅晶体管的所述源极施加一个第一电压;

向一个外部注入导体施加一个小于所述第一电压的具有一个相对大幅度的第二电压;和

选择性地将每个所述第一和所述第二pFET浮栅晶体管的所述漏极切换成与所述导体电接触,而向其施加所述第二电压,以在每个所述第一和所述第二pFET浮栅晶体管上产生一个相对大的漏极到栅极电压。

71.根据权利要求70所述的方法,其中所述选择性切换是通过一个pFET晶体管所执行。

72.一种用于选择性地引导电子转移到一个差分非挥发性浮栅存储器的浮栅上的电路,所述电路包含:

一个具有保持在第一电压的第一浮栅、一个第一漏极和一个第一源极的第一pFET;

一个具有一个第二浮栅、一个第二漏极和一个第二源极的第二pFET;

一个载有一个外部注入信号的第一节点,所述外部注入信号相对于所述第一电压为负;

一个经耦合以在所述第一节点和所述第一漏极之间选择性导电的第一开关;和

一个经耦合以在所述第一节点和所述第二漏极之间选择性地导电的第二开关。

73.根据权利要求72所述的电路,其中:

所述第一开关是一个具有一个第三栅极、第三漏极、第三源极和一个第一井连接的pFET;

所述第二开关是一个具有一个第四栅极、第四漏极、第四源极和一个第二井连接的pFET;并且还包含:

一个载有一个外部注入选择信号的第二节点,所述第二节点耦合到所述第三栅极和所述第四栅极。

74.根据权利要求72所述的电路,其还包含:

一个载有所述相同相位的一个如所述外部注入信号的信号的第三节点,所述第三节点耦合到所述第一井连接并耦合到所述第二井连接。

75.一种用于选择性地引导电子转移到一个差分非挥发性浮栅极存储器的所述浮栅上的电路,所述电路包含:

一个具有一个第一浮栅、一个第一漏极和一个第一源极的第一pFET;

一个具有一个第二浮栅、一个第二漏极和一个第二源极的第二pFET;

用于在所述第一和所述第二pFET上产生一个相对大的漏极到栅极电压,以进而引导电子转移到所述第一和所述第二浮栅上的构件。

76.根据权利要求27所述的方法,其中:

所述初始比较是通过比较所述第一浮栅pFET的一个源极-漏极电流和所述第二浮栅pFET的一个源极-漏极电流而执行的;和

所述初始比较包括将所述第一浮栅pFET的所述源极-漏极电流与所述第二浮栅pFET的所述源极-漏极电流的至少一个与一个第一固定电流结合。

77.根据权利要求76所述的方法,还包含:

随后比较所述第一浮栅pFET的所述源极-漏极电流和所述第二浮栅pFET的所述源极-漏极电流,其中所述随后地比较包括在所述随后比较步骤期间,将所述第一浮栅pFET的所述源极-漏极电流与所述第二浮栅pFET的所述源极-漏极电流的至少一个与一个第二固定电流结合。

78.一种差分非挥发性浮栅存储器,其包含:

一个具有一个源极、漏极和第一浮栅的第一pFET浮栅晶体管;

一个具有一个源极、漏极和第二浮栅的第二pFET浮栅晶体管;

一个经耦合以向所述第一pFET浮栅晶体管提供电流的第一电流源;

一个经耦合以向所述第二pFET浮栅晶体管提供电流的第二电流源;和

一个经耦合以将所述第一和所述第二电流源的输出选择性地彼此耦合的选择开关。

79.根据权利要求78所述的存储器,其中所述第一电流源和所述第二电流源为pFET。

80.根据权利要求79所述的存储器,其还包含:

一个与所述第一pFET浮栅晶体管相关的第一电容性耦合控制节点;和

一个与所述第二pFET浮栅晶体管相关的第二电容性耦合控制节点。

81.根据权利要求80所述的存储器,其中所述第一控制节点被耦合到所述第一电流源的所述源极,并且所述第二控制节点被耦合到所述第二电流源的所述源极。

82.根据权利要求81所述的存储器,其还包含:

一个经耦合以从所述第一浮栅除去电子的第一穿隧接合;和

一个经耦合以从所述第二浮栅除去电子的第二穿隧接合。

83.根据权利要求80所述的存储器,其中所述第一控制节点被耦合到所述第一电流源的所述漏极,并且所述第二控制节点被耦合到所述第二电流源的所述漏极。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/190,337 | 2002-07-05 | ||

| US10/190,337 US20040004861A1 (en) | 2002-07-05 | 2002-07-05 | Differential EEPROM using pFET floating gate transistors |

| US10/437,262 US6950342B2 (en) | 2002-07-05 | 2003-05-12 | Differential floating gate nonvolatile memories |

| US10/437,262 | 2003-05-12 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN1679110A true CN1679110A (zh) | 2005-10-05 |

Family

ID=29999854

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN03820492.4A Pending CN1679110A (zh) | 2002-07-05 | 2003-07-03 | 差分浮栅非挥发性存储器 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20040004861A1 (zh) |

| EP (1) | EP1527454A1 (zh) |

| JP (1) | JP2005532654A (zh) |

| CN (1) | CN1679110A (zh) |

| AU (1) | AU2003261122A1 (zh) |

| WO (1) | WO2004006262A2 (zh) |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101610028B (zh) * | 2008-03-26 | 2012-04-18 | 英飞凌科技股份有限公司 | 能抑制扰动的电荷泵 |

| CN103137201A (zh) * | 2013-03-21 | 2013-06-05 | 苏州宽温电子科技有限公司 | 一种标准逻辑工艺兼容的差分架构nvm存储器单元 |

| CN103366821A (zh) * | 2013-06-26 | 2013-10-23 | 苏州宽温电子科技有限公司 | 一种基于串联晶体管型的改进的差分架构otp存储单元 |

| CN103456359A (zh) * | 2013-09-03 | 2013-12-18 | 苏州宽温电子科技有限公司 | 基于串联晶体管型的改进的差分架构Nor flash存储单元 |

| CN103745750A (zh) * | 2013-12-25 | 2014-04-23 | 苏州宽温电子科技有限公司 | 一种基于熔丝特性的改进的差分架构otp存储单元 |

| CN104112476A (zh) * | 2014-07-22 | 2014-10-22 | 中国人民解放军国防科学技术大学 | 兼容标准cmos工艺的超低功耗伪差分结构非易失性存储器 |

| CN106531214A (zh) * | 2015-09-09 | 2017-03-22 | 爱思开海力士有限公司 | 非易失性存储器件及其编程方法 |

| CN107833587A (zh) * | 2016-09-15 | 2018-03-23 | 格罗方德半导体公司 | 用于可编程存储器阵列的字线电压产生器 |

| CN110021606A (zh) * | 2018-01-10 | 2019-07-16 | 力旺电子股份有限公司 | 单层多晶硅非挥发性内存单元 |

| CN111052238A (zh) * | 2017-08-31 | 2020-04-21 | 美光科技公司 | 断电响应 |

Families Citing this family (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6965142B2 (en) * | 1995-03-07 | 2005-11-15 | Impinj, Inc. | Floating-gate semiconductor structures |

| US6664909B1 (en) | 2001-08-13 | 2003-12-16 | Impinj, Inc. | Method and apparatus for trimming high-resolution digital-to-analog converter |

| US20040206999A1 (en) * | 2002-05-09 | 2004-10-21 | Impinj, Inc., A Delaware Corporation | Metal dielectric semiconductor floating gate variable capacitor |

| US6977527B1 (en) | 2002-06-13 | 2005-12-20 | Impinj, Inc. | Method and apparatus for suppressing spurious values in a differential output current |

| US7221596B2 (en) * | 2002-07-05 | 2007-05-22 | Impinj, Inc. | pFET nonvolatile memory |

| US6950342B2 (en) * | 2002-07-05 | 2005-09-27 | Impinj, Inc. | Differential floating gate nonvolatile memories |

| US20050030827A1 (en) * | 2002-09-16 | 2005-02-10 | Impinj, Inc., A Delaware Corporation | PMOS memory cell |

| US7212446B2 (en) * | 2002-09-16 | 2007-05-01 | Impinj, Inc. | Counteracting overtunneling in nonvolatile memory cells using charge extraction control |

| US7149118B2 (en) * | 2002-09-16 | 2006-12-12 | Impinj, Inc. | Method and apparatus for programming single-poly pFET-based nonvolatile memory cells |

| EP1552530A2 (en) * | 2002-10-08 | 2005-07-13 | Impinj Inc. | Use of analog-valued floating-gate transistors to match the electrical characteristics of interleaved and pipelined |

| US7187237B1 (en) | 2002-10-08 | 2007-03-06 | Impinj, Inc. | Use of analog-valued floating-gate transistors for parallel and serial signal processing |

| US7145370B2 (en) * | 2003-09-05 | 2006-12-05 | Impinj, Inc. | High-voltage switches in single-well CMOS processes |

| KR101264761B1 (ko) * | 2004-02-10 | 2013-05-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 비휘발성 메모리와 그것을 내장하는 ic 카드, id 카드 및 id 태그 |

| US7242614B2 (en) | 2004-03-30 | 2007-07-10 | Impinj, Inc. | Rewriteable electronic fuses |

| US7388420B2 (en) * | 2004-03-30 | 2008-06-17 | Impinj, Inc. | Rewriteable electronic fuses |

| US7177182B2 (en) * | 2004-03-30 | 2007-02-13 | Impinj, Inc. | Rewriteable electronic fuses |

| US7283390B2 (en) | 2004-04-21 | 2007-10-16 | Impinj, Inc. | Hybrid non-volatile memory |

| US8111558B2 (en) | 2004-05-05 | 2012-02-07 | Synopsys, Inc. | pFET nonvolatile memory |

| US7772063B2 (en) * | 2004-08-11 | 2010-08-10 | Identifi Technologies, Inc. | Reduced-step CMOS processes for low-cost radio frequency identification devices |

| US7257033B2 (en) | 2005-03-17 | 2007-08-14 | Impinj, Inc. | Inverter non-volatile memory cell and array system |

| US7715236B2 (en) * | 2005-03-30 | 2010-05-11 | Virage Logic Corporation | Fault tolerant non volatile memories and methods |

| US7679957B2 (en) * | 2005-03-31 | 2010-03-16 | Virage Logic Corporation | Redundant non-volatile memory cell |

| US7563400B2 (en) * | 2005-04-12 | 2009-07-21 | Advanced Cardiovascular Systems, Inc. | Method of stent mounting to form a balloon catheter having improved retention of a drug delivery stent |

| US8122307B1 (en) | 2006-08-15 | 2012-02-21 | Synopsys, Inc. | One time programmable memory test structures and methods |

| US7719896B1 (en) | 2007-04-24 | 2010-05-18 | Virage Logic Corporation | Configurable single bit/dual bits memory |

| US7920423B1 (en) | 2007-07-31 | 2011-04-05 | Synopsys, Inc. | Non volatile memory circuit with tailored reliability |

| JP2009239161A (ja) * | 2008-03-28 | 2009-10-15 | Genusion Inc | 不揮発性半導体記憶装置及びその使用方法 |

| US7894261B1 (en) | 2008-05-22 | 2011-02-22 | Synopsys, Inc. | PFET nonvolatile memory |

| US8032804B2 (en) * | 2009-01-12 | 2011-10-04 | Micron Technology, Inc. | Systems and methods for monitoring a memory system |

| US9601203B2 (en) * | 2012-06-09 | 2017-03-21 | Synopsys, Inc. | Floating gate non-volatile memory bit cell |

| CN104112475B (zh) * | 2014-07-21 | 2017-02-15 | 中国人民解放军国防科学技术大学 | 一种伪差分读取非易失存储器结构 |

| CN104112472B (zh) * | 2014-07-22 | 2017-05-03 | 中国人民解放军国防科学技术大学 | 兼容标准cmos工艺的超低功耗差分结构非易失性存储器 |

| CN106531210B (zh) * | 2016-10-11 | 2019-11-05 | 苏州宽温电子科技有限公司 | 一种改善p型nvm存储器nbti效应的差分架构存储单元 |

| US11537871B2 (en) * | 2018-04-25 | 2022-12-27 | Fujitsu Limited | Deep neural network training for application program generation |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5912842A (en) * | 1995-11-14 | 1999-06-15 | Programmable Microelectronics Corp. | Nonvolatile PMOS two transistor memory cell and array |

| US5761121A (en) * | 1996-10-31 | 1998-06-02 | Programmable Microelectronics Corporation | PMOS single-poly non-volatile memory structure |

| US6329240B1 (en) * | 1999-10-07 | 2001-12-11 | Monolithic System Technology, Inc. | Non-volatile memory cell and methods of fabricating and operating same |

| US6639835B2 (en) * | 2000-02-29 | 2003-10-28 | Micron Technology, Inc. | Static NVRAM with ultra thin tunnel oxides |

-

2002

- 2002-07-05 US US10/190,337 patent/US20040004861A1/en not_active Abandoned

-

2003

- 2003-07-03 CN CN03820492.4A patent/CN1679110A/zh active Pending

- 2003-07-03 AU AU2003261122A patent/AU2003261122A1/en not_active Abandoned

- 2003-07-03 JP JP2004519985A patent/JP2005532654A/ja active Pending

- 2003-07-03 EP EP03763311A patent/EP1527454A1/en not_active Withdrawn

- 2003-07-03 WO PCT/US2003/021239 patent/WO2004006262A2/en active Search and Examination

Cited By (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101610028B (zh) * | 2008-03-26 | 2012-04-18 | 英飞凌科技股份有限公司 | 能抑制扰动的电荷泵 |

| CN103137201A (zh) * | 2013-03-21 | 2013-06-05 | 苏州宽温电子科技有限公司 | 一种标准逻辑工艺兼容的差分架构nvm存储器单元 |

| CN103366821A (zh) * | 2013-06-26 | 2013-10-23 | 苏州宽温电子科技有限公司 | 一种基于串联晶体管型的改进的差分架构otp存储单元 |

| CN103456359A (zh) * | 2013-09-03 | 2013-12-18 | 苏州宽温电子科技有限公司 | 基于串联晶体管型的改进的差分架构Nor flash存储单元 |

| CN103745750A (zh) * | 2013-12-25 | 2014-04-23 | 苏州宽温电子科技有限公司 | 一种基于熔丝特性的改进的差分架构otp存储单元 |

| CN104112476A (zh) * | 2014-07-22 | 2014-10-22 | 中国人民解放军国防科学技术大学 | 兼容标准cmos工艺的超低功耗伪差分结构非易失性存储器 |

| CN106531214A (zh) * | 2015-09-09 | 2017-03-22 | 爱思开海力士有限公司 | 非易失性存储器件及其编程方法 |

| CN106531214B (zh) * | 2015-09-09 | 2020-08-18 | 爱思开海力士有限公司 | 非易失性存储器件及其编程方法 |

| CN107833587A (zh) * | 2016-09-15 | 2018-03-23 | 格罗方德半导体公司 | 用于可编程存储器阵列的字线电压产生器 |

| CN107833587B (zh) * | 2016-09-15 | 2021-03-23 | 格芯(美国)集成电路科技有限公司 | 用于可编程存储器阵列的字线电压产生器 |

| CN111052238A (zh) * | 2017-08-31 | 2020-04-21 | 美光科技公司 | 断电响应 |

| CN111052238B (zh) * | 2017-08-31 | 2024-04-02 | 美光科技公司 | 断电响应 |

| CN110021606A (zh) * | 2018-01-10 | 2019-07-16 | 力旺电子股份有限公司 | 单层多晶硅非挥发性内存单元 |

| CN110021606B (zh) * | 2018-01-10 | 2022-02-22 | 力旺电子股份有限公司 | 单层多晶硅非挥发性内存单元 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1527454A1 (en) | 2005-05-04 |

| AU2003261122A1 (en) | 2004-01-23 |

| JP2005532654A (ja) | 2005-10-27 |

| WO2004006262A2 (en) | 2004-01-15 |

| US20040004861A1 (en) | 2004-01-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1679110A (zh) | 差分浮栅非挥发性存储器 | |

| CN1143313C (zh) | 闪速存储器阵列 | |

| JP4427382B2 (ja) | 不揮発性半導体記憶装置 | |

| US7423910B2 (en) | Semiconductor device including MOS transistors having floating gate and control gate | |

| US7499327B2 (en) | NAND flash memory device having page buffer adapted to discharge bit line voltage during erase operation | |

| CN1269137C (zh) | 半导体存储器件 | |

| CN1249518A (zh) | 非易失性半导体存储器件 | |

| US20050052918A1 (en) | Semiconductor device having a byte-erasable eeprom memory | |

| CN101640067B (zh) | 用于减少穿通泄漏的存储器单元与阵列操作方法 | |

| CN1477644A (zh) | 非易失性半导体存储器及其操作方法 | |

| CN1967879A (zh) | 非挥发性存储器及其制造方法与操作方法 | |

| US7313029B2 (en) | Method for erasing flash memories and related system thereof | |

| CN1701383A (zh) | 位线串扰误差得到减少的非易失性存储器及方法 | |

| CN1462038A (zh) | 非易失存储器及其驱动方法 | |

| US20100149873A1 (en) | Push-pull fpga cell | |

| US9183934B2 (en) | Split block semiconductor memory device | |

| JP2005522884A (ja) | 半導体メモリ・デバイス | |

| US8363475B2 (en) | Non-volatile memory unit cell with improved sensing margin and reliability | |

| US7099191B2 (en) | Channel erase type nonvolatile semiconductor memory device and electronic card and electronic apparatus using the device | |

| JP2007088216A (ja) | 半導体装置とその駆動方法 | |

| CN1832037A (zh) | 非易失存储器和其驱动方法 | |

| CN1306616C (zh) | 包括每个有浮动栅和控制栅极的mos晶体管的半导体存储器 | |

| CN1779859A (zh) | 页面缓存器和包括页面缓存器的非易失性半导体存储器 | |

| TWI660354B (zh) | 非揮發性半導體記憶裝置 | |

| US7061805B2 (en) | P-channel NAND flash memory and operating method thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |