US5561771A - System for transmitting data between systems using selected subsets of plural interconnecting bus lines and including selection of a compatible transmission speed - Google Patents

System for transmitting data between systems using selected subsets of plural interconnecting bus lines and including selection of a compatible transmission speed Download PDFInfo

- Publication number

- US5561771A US5561771A US08/514,500 US51450095A US5561771A US 5561771 A US5561771 A US 5561771A US 51450095 A US51450095 A US 51450095A US 5561771 A US5561771 A US 5561771A

- Authority

- US

- United States

- Prior art keywords

- bus

- data

- node

- nodes

- transmitting

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

- H04L12/40006—Architecture of a communication node

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

- H04L12/4013—Management of data rate on the bus

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

- H04L12/40169—Flexible bus arrangements

- H04L12/40176—Flexible bus arrangements involving redundancy

- H04L12/40182—Flexible bus arrangements involving redundancy by using a plurality of communication lines

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

- H04L12/407—Bus networks with decentralised control

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L9/00—Cryptographic mechanisms or cryptographic arrangements for secret or secure communications; Network security protocols

- H04L9/40—Network security protocols

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/22—Parsing or analysis of headers

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L69/00—Network arrangements, protocols or services independent of the application payload and not provided for in the other groups of this subclass

- H04L69/24—Negotiation of communication capabilities

Definitions

- the invention relates generally to data packet communications systems, and more particularly to a method and apparatus for transmitting data on a wide, high speed data bus.

- the hardware costs of the bus transmitter/receiver circuitries include not only the particular drivers connected to the bus, but the memories, logic gates, etc. which also need to operate more quickly to properly use the faster bus.

- memory access requirements increase in direct proportion to the bus speed.

- the added cost of faster memory is especially burdensome.

- Other objects of the invention are a method and apparatus having high reliability, simplicity of structure, and redundancy in circuit use.

- the invention thus relates to a method and apparatus for transmitting data between nodes connected to a communications bus where the bus width is at least equal to the number of bits in a data word to be transmitted on the bus.

- the method features the steps of connecting each node to the communications bus over at least one subset of bus lines, the combination of the subsets of bus lines including the entire bus.

- the method further features determining, at a transmitting node, those bus subsets over which the transmitting node can communicate with an intended destination node, and sending each data word to the destination node as a sequence of subwords over a bus subset selected from those determined bus subsets.

- the method in a particular embodiment, further features appending, as a header to the data words, a sequence of destination node identification symbols, and appending at the end of the sequence of data words, error checking information data for checking, at the destination node, the accuracy of the received data words.

- the method features sending, from the destination node, and during a data transmission, a flow control signal for informing or warning the transmitting source node of an overflow error condition occurring at the destination node.

- the method can further feature selecting, at the transmitting node, a speed at which to send the data words and ensuring that all header information is sent at a slow bus speed which can be read by all nodes connected to the selected bus subset.

- the error checking information data can also be sent at the slow bus speed, to provide the destination node with the time required to check the error checking information data to ensure accuracy of transmission.

- the apparatus of the invention relates to transmitting data between nodes connected to a communications bus, the bus having a bus width at least equal to the data words to be transmitted.

- the apparatus features circuitry for connecting each node to the communications bus over at least one subset of bus lines, hereafter called a sub-bus, a combination of the sub-buses covering, collectively, the entire communications bus.

- the apparatus further features circuitry for determining, at a transmitting node, those sub-buses over which the transmitting node can communicate with an intended destination node, and further, circuitry for sending each data word as a time sequence of subwords over a sub-bus selected from those determined acceptable sub-buses.

- the apparatus further features circuitry for appending a header to the beginning of the sequence of data words, the header including destination node identification symbols, and circuitry for appending at the end of the sequence of data words for a packet, an error checking information data for enabling the destination node to check the accuracy of the received data words.

- Circuitry also can be provided for sending from the destination node, during a data transmission, an overflow warning signal for informing the transmitting node of for example, an overflow error condition at the destination node.

- the apparatus can further feature circuitry which selects a speed at which to send the data words but, however, which sends all header information, and preferably the error checking information data, at a slow bus speed which can be read by all nodes connected to the sub-bus.

- the slower speed enables the destination node to perform error checking in real time since the error checking method is a substantially time consuming process.

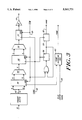

- FIG. 1 is a block diagram of transmitter circuitry in accordance with a preferred embodiment of the invention

- FIG. 1A is a diagram of a data packet

- FIG. 1B is a representation of the lines of a sub-bus in accordance with the invention.

- FIG. 1C is a representation of a slot mask in accordance with the invention.

- FIG. 2 is a state diagram for the transmitter node in accordance with the invention.

- FIG. 3 is a detailed diagram of the transmitter data path circuitry

- FIG. 4 is a state diagram of the receiver node in accordance with a preferred embodiment of the invention.

- FIG. 5 is a circuit configuration for a receiver input data path in accordance with a preferred embodiment of the invention.

- FIG. 6 is a timing diagram for data transmission on the sub-bus.

- FIG. 7 is a timing diagram illustrating a particular bus arbitration strategy in accordance with invention.

- a transmitter/receiver apparatus 10 passes data between a memory bus 12 and a wide bus 14 which can be, for example, a standard wide bus, thirty-two data bits in width, such as a computer internal backbone.

- the bus has, also, a plurality of control lines.

- a transmitter section 20 and a receiver section 21 of each node are connected to one such memory bus or its equivalent.

- Also connected to the memory bus are a CPU 50 and a memory storage element 52.

- the transmitter section 20 of the apparatus has a transmitter dequeue circuitry 22 which receives data to be transmitted over bus 14 from the memory bus 12.

- the data includes destination data and information data to be used at the destination node or nodes.

- the transmitter dequeue circuitry makes the destination data available to a bus selection apparatus 24 which selects which of a plurality of sub-buses (26a, 26b, . . . 26n) of bus 14 will be employed in connection with the transmission of this data.

- the data is delivered to a connected single packet DMA transmission circuitry (28a, 28b, . . . 28n) for each selected sub-bus and which operates at a speed selected by a speed selection circuitry 30.

- the output of the single packet DMA circuitry is passed to a connected driver (32a, 32b, . . . 32n) for transmission to the respective sub-bus.

- Each network node connected to bus 14, is connected to one or more of the sub-buses 26.

- Each receiving (destination) node examines each of the packets available to it, over each of the sub-buses to which it is connected, using a single packet DMA receiver circuitry (40a, 40b, . . . 40n).

- Each receiver circuitry 40 receives the data packet from the sub-bus through a respective receiver driver (42a, 42b . . . 42n).

- An output of the packet DMA receiver circuitries is delivered to a receiver dequeue/enqueue circuitry 46 and data packets can be stored in selected buffers as described in more detail below.

- bus 14 is a 32-bit wide bus which is divided into four 8-bit wide sub-buses.

- Each sub-bus has both data lines 43a and control lines 43b (FIG. 1B).

- the bus 14 can operate, over its entire width, at, for example, 100 megabits per second, and correspondingly, each sub-bus operates at 25 megabits per second. Accordingly, since each node will transmit data to a specific destination node on only one sub-bus in accordance with the invention, the node operates at the slower speed of 25 megabits per second.

- the sub-buses need not operate in a synchronized manner.

- the transmit dequeue circuitry 22 dequeues a packet provided from the CPU or, under the control of the CPU, from memory, and makes the destination address data available to the bus selection circuitry 24 over lines 60.

- the destination data is made available as a "slot mask" 61, at the bus selection circuitry 24.

- the slot mask (FIG. 1C) is a two byte word, in the illustrated embodiment, wherein a "one" bit represents a destination ("slot") address for the packet.

- a packet can have multiple destinations, in which case the slot mask has multiple bits set, each bit (of the two byte mask in the illustrated embodiment) representing a different destination.

- the slot mask is compared to existence maps in a slot existence map (a data map array) circuitry 62.

- the slot existence map indicates, for each destination node, which sub-buses can be used for the transfer of data between nodes.

- the slot mask provides a bit position for each of the nodes connected to bus 14 (FIG. 1C); and for each sub-bus, the existence of a set bit in the existence map for that sub-bus indicates a receiver connection of that node to the sub-bus, while the absence of a set bit indicates the absence of an interface connection, for that destination node, to the sub-bus.

- the bus selection circuitry also sends the packet destination slot mask to the speed selection circuitry 30.

- the speed selection circuitry 30 examines a stored speed map 64 to determine the maximum data rate at which the packet data can be sent to the selected destination(s). Thereafter, once the speed and the sub-bus have been determined, the information data is made available to the selected transmitter single packet DMA circuitry(s) and the data are sent over the sub-bus(es) by that transmit DMA circuitry(s) through its associated driver(s) 32 when control of the bus(es) has been made available to the associated transmit DMA (as described below). Thereafter the process is repeated for each successive packet to be transmitted.

- the CPU can designate a specific sub-bus to be employed in the transmission process thus bypassing the sub-bus selection circuitry 24 of the transmitter section.

- each receiver single packet DMA circuitry 40 monitors all packets on its connected sub-bus. Whenever a packet is found to include the predetermined receiver slot number, specified by the destination slot mask in the packet header, a dequeue request is issued by the receiver circuitry 40 to the receiver dequeue/enqueue circuitry 46. The receiver dequeue/enqueue logic circuitry 46 then obtains a buffer, which is available from a pool of free buffers provided by the CPU, and the address of the buffer is sent to the requesting receiver DMA circuitry 40. The receiver DMA circuitry then DMA's the received packet directly into the designated buffer of memory.

- the buffer is made available to the receiver dequeue/enqueue circuitry 46 and is placed in a receiver queue at the CPU. If an error is detected, the receiver dequeue/enqueue circuitry places the allocated buffer back in the so-called "free" pool and the resulting data is effectively lost, and in not made available to the CPU.

- the operating system protocol handles a request for retransmittal of the packet.

- the maximum speed at which the information can be sent over the sub-bus is the highest speed at which all receivers can receive and properly process the information.

- the transmitter sends an error check code which is processed by each of those receivers which were selected as destinations for the data.

- the transmitter since the error checking process is extremely complex and accordingly slow (at the receiver processing level), the transmitter slows the transmission rate to a low speed transmission which provides each receiver with adequate time to perform the necessary error checking process without an undue storage requirement at the receiving node.

- the transmitter requires four clock cycles of the bus to send a thirty-two bit wide word.

- the transmitter when it initiates operation, thus resides in state 100, in which it is IDLE.

- the transmitter sets a bus request; enters state 102 at which it checks to see that the BUS GRANT signal (a sub-bus control line) is not asserted and that the FRAME signal (a sub-bus control line) also is not asserted (refer to FIGS. 6 and 7 for timing diagrams of the bus operation and bus arbitration according to a preferred embodiment of the invention).

- the transmitter then proceeds to a no operation (NOP) state 104. Thereafter the BUS REQ signal is asserted and thereafter the BUS GRANT is asserted.

- the FRAME signal is set in state 106 if the FLOW control signal over lines 109 (FIG. 3) (a warning bus control signal connected to all nodes) is not asserted, and the first, upper byte of the first word to be sent is transmitted at state 108. If the FLOW control signal remains not asserted, a second upper byte of the word is transmitted at state 110, a third byte at state 112, and a fourth and last byte of the thirty-two bit word is transmitted at state 114.

- the transmitter cycles back to send the beginning of the next thirty-two bit word of the packet at state 108. If the FLOW signal is not asserted and the packet data transmission is complete (DONE is asserted), the transmitter begins to send the first byte of the error correction code as indicated at state 116. Thereafter the successive bytes of the thirty-two bit error correction code are sent at states 118, 120, and 122. Finally, the FRAME signal is cleared (reset) at state 124 and the transmitter returns to its IDLE state 100.

- a typical transmitter structure receives the data over data lines 142 and synchronous with a clock signal over a sub-bus control line 140.

- the data passes through a thirty-two bit latch 144 which latches the data at each fourth clock time so long as the FLOW signal is not enabled.

- the output of latch 144 is input to a multiplexer 146 which, in response to the clock signals, passes one or the other of the high and low order sixteen bits of the stored thirty-two bit data word.

- the sixteen bit output of multiplexor 146 is held in a latch 148, controlled in the same manner as latch 144, and the two eight-bit outputs of latch 148 (high and low) are sequentially made available through multiplexer 150 to a third latch 152.

- the output of the third latch is made available to a sub-bus over a line 154 through a driver 32.

- Timing for the transmitter data path is generated through the EXCLUSIVE-OR gate 156, and bistable flip flops 158. So long as the FLOW signal is not enabled, this circuitry divides by two with an output level change on line 160 every clock cycle, and shifted by one-half of a clock cycle to allow setting of the output data at the output of latch 152.

- the transmitter circuitry also includes a FRAME signal generation logic 162, responsive to the clock signal 140 and an initialization signal over a line 164 from the CPU for generating the FRAME control signal.

- the receiver state diagram describes the operation of a receiver such as that illustrated schematically in FIG. 5.

- the start or initiation of operation begins at a FLUSH state 170.

- the receiver changes to a state 172 waiting there for the leading edge of the next FRAME signal.

- the receiver receives the first eight-bit byte from the channel over the sub-bus at state 174.

- the receiver advances to a next state 176, 178, and either 180 or 170, as it reads each successive byte.

- the receiver After state 178, upon the next leading of the timing signal, the receiver either returns to the FLUSH state 170 which indicates that the packet slot bit was not set for that receiver and the packet should be ignored, or the receiver steps to state 180 because it recognizes that it is a destination for the incoming packet.

- state 180 the receiver receives the entire packet and the end of the packet is indicated by the trailing edge of the FRAME signal, at which time, the receiver returns its normal IDLE state, state 172.

- a typical receiver data path provides for receiving eight bit wide data over lines 190.

- the eight bit data bytes pass through latches 192, 194 and 196 so that as each additional eight bits is received, the full thirty-two bit word is built up and is eventually stored in the latch 196 from which it is stored in a fifo buffer 198.

- the timing information is generated from the clock signal placed on the clock control line of the sub-bus by the transmitting node. Thus a level change occurs synchronously with the incoming data bytes and at the rate of the data byte transmission. At the first leading edge of the timing signal the first byte of a data word is stored in latch 192.

- latch 192 Upon the occurrence of the next leading edge of the timing signal on line 202, latch 192 again loads data into its register. This is the third byte of data in a four byte word.

- latch 196 Upon the occurrence of the next trailing edge, latch 196 will operate, loading the two bytes of data from latch 194 into its lower half, and the upper two bytes of data from the output of latch 192 and the data lines 190 into its upper half. The full word is then made available to the receiver fifo buffer 198.

- circuitry associated with flipflop 200 which is enabled by the FRAME signal, is well known as a divide-by-two register. Accordingly, its operation in causing latch 196 to load only on every other trailing edge is well known to those of ordinary skill in the art.

- the logic of the receiver FIFO buffer 198 asserts the FLOW signal to prevent the FIFO buffer from overflowing in the event that the receiver FIFO buffer 198 is getting too full .

- an error (interrupt) line (not shown) is asserted if a CRC error occurs.

- a slot recognition circuit 222 is responsive to the output of latch 194, the timing signal, and the FRAME signal for recognizing, by a signal over a line 224 that the incoming packet is intended for this node.

- the timing of the control signals available over the sub-bus was described generally in connection with the hardware of the transmitter and receiver circuitries.

- a transmitter Once a transmitter has obtained access to the bus, it asserts the FRAME signal over line 206 which then "alerts" each of the connected receivers that a new data packet is forthcoming.

- the timing signals applied at a slow rate with regard to the header, are applied to the clock control line 160 of the bus and provides the timing for the received signal over line 202.

- the initial data (the header) is provided at a relatively slow rate

- the intermediate data information is provided at a fast rate

- the error control, (the CRC checksum in the illustrated embodiment) is provided at a slow rate.

- the timing signal, line 302 corresponds to the clock rate as described above. If, at any time, the receiver falls behind, the receiver asserts the FLOW line 304 which causes the transmitter to stop transmission. If the FLOW line is asserted for less than a predetermined time, (corresponding to the receiver "catching up"), the receiver can negate the FLOW assertion and the transmitter will then continue to transmit data. (If the transmitter detects a FLOW assertion for more than this minimum period of time, the transmitter will ignore the FLOW signal and may thus overrun the receiver input FIFO buffer 198. If the receiver detects this buffer state, an overflow error occurs at the receiver.)

- the bus arbitration strategy for the illustrated embodiment of the invention provides that a transmitter, which has information to transmit, asserts a BUS REQ signal 310 to a bus arbitration circuitry (not shown).

- a bus arbitration circuitry (not shown).

- Each node is connected directly to the arbitration circuitry in the illustrated embodiment, by two signal lines, a BUS REQ line and a BUS GRANT line.

- the bus arbitration circuitry examines the BUS REQ lines from all nodes and selects one requesting node at random, in this illustrated embodiment, and asserts a BUS GRANT line 314 to that node.

- the BUS GRANT signal will enable the transmitter to raise the FRAME signal 320 (after that control signal is lowered by the presently transmitting node, as illustrated in FIG.

- the BUS REQ signal is cleared by the transmitting node (as illustrated at 108 in FIG. 2), and accordingly the BUS GRANT signal to the node is also cleared to its unasserted state. A next BUS REQ signal is then acknowledged by the arbitration circuitry.

- a data transfer mechanism is used wherein the data bus is divided into a plurality of independent sub-buses and each sub-bus operates "on its own” at all times.

- Each sub-bus can act to "cover” for a failed sub-bus thus enabling, if the node has the appropriate connection, reliable communications to be achieved even when part of the bus channel is inoperative.

- all buses operate, and the memory access time requirements are minimized, enabling less expensive memory to be employed even though the full bus operates at a substantially higher transfer rate.

Abstract

A method and apparatus for transmitting data between nodes connected to a communications bus, preferably a computer backbone, divides a full bus width into a plurality of sub-buses. Each sub-bus can be independently operated, and each node on the network can connect to one or more of the sub-buses. The apparatus provides, at a transmitting node, a determination of which sub-buses are available to transmit a data packet to one or more receiving nodes. The data words are divided into sub-words, thereby reducing the memory access time requirements and saving memory costs. In accordance with a particular embodiment, the header, at the beginning of the data packet, and the error check control, provided at the end of the data packet, are sent at a slower speed than the data information portion of the packet. The data information portion of the packet is sent at the highest speed compatible with the receiving node or nodes. In case one sub-bus fails, a node can transmit data over the other sub-buses available to it.

Description

This is a continuation of application Ser. No. 08/161,208, now U.S. Pat. No. 5,442,750, filed Dec. 2, 1993, which is a continuation of application Ser. No. 07/771,743, now abandoned, filed Oct. 4, 1991.

The invention relates generally to data packet communications systems, and more particularly to a method and apparatus for transmitting data on a wide, high speed data bus.

As the available data transmission speed of networks increases, the hardware connecting to those networks must similarly increase in speed. Thus, hardware connected to a 16 megabit per second bus runs substantially more slowly than that hardware connected to a 100 megabit per second bus. Since the slower hardware is less expensive than the faster hardware, a hidden, and not insubstantial cost of increasing bus throughput is the price of the processing hardware to which it is connected.

The hardware costs of the bus transmitter/receiver circuitries include not only the particular drivers connected to the bus, but the memories, logic gates, etc. which also need to operate more quickly to properly use the faster bus. In particular, memory access requirements increase in direct proportion to the bus speed. The added cost of faster memory is especially burdensome.

The typical response to increased bus throughput, however, has and continues to be faster hardware. That faster hardware includes also faster control logic and processors and increases the cost of the entire network connection circuitry. To date, no alternative has been available to control network board costs while still operating a higher speed bus at its full capacity.

It is therefore an object of the invention to provide alternative circuit configurations for using high speed buses while controlling connection costs and memory costs. Other objects of the invention are a method and apparatus having high reliability, simplicity of structure, and redundancy in circuit use.

The invention thus relates to a method and apparatus for transmitting data between nodes connected to a communications bus where the bus width is at least equal to the number of bits in a data word to be transmitted on the bus. The method features the steps of connecting each node to the communications bus over at least one subset of bus lines, the combination of the subsets of bus lines including the entire bus. The method further features determining, at a transmitting node, those bus subsets over which the transmitting node can communicate with an intended destination node, and sending each data word to the destination node as a sequence of subwords over a bus subset selected from those determined bus subsets.

The method, in a particular embodiment, further features appending, as a header to the data words, a sequence of destination node identification symbols, and appending at the end of the sequence of data words, error checking information data for checking, at the destination node, the accuracy of the received data words.

In another aspect, the method features sending, from the destination node, and during a data transmission, a flow control signal for informing or warning the transmitting source node of an overflow error condition occurring at the destination node. The method can further feature selecting, at the transmitting node, a speed at which to send the data words and ensuring that all header information is sent at a slow bus speed which can be read by all nodes connected to the selected bus subset. In addition, the error checking information data can also be sent at the slow bus speed, to provide the destination node with the time required to check the error checking information data to ensure accuracy of transmission.

The apparatus of the invention relates to transmitting data between nodes connected to a communications bus, the bus having a bus width at least equal to the data words to be transmitted. The apparatus features circuitry for connecting each node to the communications bus over at least one subset of bus lines, hereafter called a sub-bus, a combination of the sub-buses covering, collectively, the entire communications bus. The apparatus further features circuitry for determining, at a transmitting node, those sub-buses over which the transmitting node can communicate with an intended destination node, and further, circuitry for sending each data word as a time sequence of subwords over a sub-bus selected from those determined acceptable sub-buses.

In preferred embodiments of the invention, the apparatus further features circuitry for appending a header to the beginning of the sequence of data words, the header including destination node identification symbols, and circuitry for appending at the end of the sequence of data words for a packet, an error checking information data for enabling the destination node to check the accuracy of the received data words. Circuitry also can be provided for sending from the destination node, during a data transmission, an overflow warning signal for informing the transmitting node of for example, an overflow error condition at the destination node.

The apparatus can further feature circuitry which selects a speed at which to send the data words but, however, which sends all header information, and preferably the error checking information data, at a slow bus speed which can be read by all nodes connected to the sub-bus. With regard to the error checking information data, the slower speed enables the destination node to perform error checking in real time since the error checking method is a substantially time consuming process.

Other objects, features, and advantages of the invention will be apparent from the following description, taken together with the drawings, in which:

FIG. 1 is a block diagram of transmitter circuitry in accordance with a preferred embodiment of the invention;

FIG. 1A is a diagram of a data packet;

FIG. 1B is a representation of the lines of a sub-bus in accordance with the invention;

FIG. 1C is a representation of a slot mask in accordance with the invention;

FIG. 2 is a state diagram for the transmitter node in accordance with the invention;

FIG. 3 is a detailed diagram of the transmitter data path circuitry;

FIG. 4 is a state diagram of the receiver node in accordance with a preferred embodiment of the invention;

FIG. 5 is a circuit configuration for a receiver input data path in accordance with a preferred embodiment of the invention;

FIG. 6 is a timing diagram for data transmission on the sub-bus; and

FIG. 7 is a timing diagram illustrating a particular bus arbitration strategy in accordance with invention.

Referring to FIG. 1, in accordance with the invention, a transmitter/receiver apparatus 10 passes data between a memory bus 12 and a wide bus 14 which can be, for example, a standard wide bus, thirty-two data bits in width, such as a computer internal backbone. Preferably, the bus has, also, a plurality of control lines. A transmitter section 20 and a receiver section 21 of each node are connected to one such memory bus or its equivalent. Also connected to the memory bus are a CPU 50 and a memory storage element 52.

The transmitter section 20 of the apparatus has a transmitter dequeue circuitry 22 which receives data to be transmitted over bus 14 from the memory bus 12. The data includes destination data and information data to be used at the destination node or nodes. The transmitter dequeue circuitry makes the destination data available to a bus selection apparatus 24 which selects which of a plurality of sub-buses (26a, 26b, . . . 26n) of bus 14 will be employed in connection with the transmission of this data. Once the selection has been made, the data is delivered to a connected single packet DMA transmission circuitry (28a, 28b, . . . 28n) for each selected sub-bus and which operates at a speed selected by a speed selection circuitry 30. The output of the single packet DMA circuitry is passed to a connected driver (32a, 32b, . . . 32n) for transmission to the respective sub-bus.

Information is transmitted over the sub-bus 26 in a data packet 33; and each packet has a header 33a, which includes destination node identification information and other protocol information if necessary, a data portion 33b and an error checking portion 33c (FIG. 1A). Each network node, connected to bus 14, is connected to one or more of the sub-buses 26. Each receiving (destination) node examines each of the packets available to it, over each of the sub-buses to which it is connected, using a single packet DMA receiver circuitry (40a, 40b, . . . 40n). Each receiver circuitry 40 receives the data packet from the sub-bus through a respective receiver driver (42a, 42b . . . 42n). An output of the packet DMA receiver circuitries is delivered to a receiver dequeue/enqueue circuitry 46 and data packets can be stored in selected buffers as described in more detail below.

The sub-buses (26a, 26b . . . 26n) together include all of the lines of bus 14. In a typical example, bus 14 is a 32-bit wide bus which is divided into four 8-bit wide sub-buses. Each sub-bus has both data lines 43a and control lines 43b (FIG. 1B). The bus 14 can operate, over its entire width, at, for example, 100 megabits per second, and correspondingly, each sub-bus operates at 25 megabits per second. Accordingly, since each node will transmit data to a specific destination node on only one sub-bus in accordance with the invention, the node operates at the slower speed of 25 megabits per second. Thus, for example, where there are memory accesses across a 32-bit word, there need only be one memory access along bus 12 for each four "subword" transmissions along an eight wide bit sub-bus 26 of bus 14. Accordingly, only one memory access is required for each group of subwords and the memory access circuitry for each node need operate at only a fraction of the speed at which a node transmitting across the entire width of bus 14, each clock cycle, would be required to operate. At the same time, however, the operation of a plurality of nodes, on the different sub-buses of bus 14, enables the bus 14 to operate efficiently at its full capacity. In this manner, the cost of memory at each node can be substantially reduced because the access time required of each memory can be greater than that otherwise associated with and required by the full bus 14. On the other hand, when all sub-buses are operating, the data transmission rate on bus 14 appears to be at the full capacity of bus 14.

In a preferred embodiment of the invention, the sub-buses need not operate in a synchronized manner. However, in accordance with the described embodiment of the invention, there are also provided three control lines for each sub-bus, to be described below, to further enhance operation of the bus system.

Considering the circuitry of FIG. 1 in more detail, the transmit dequeue circuitry 22 dequeues a packet provided from the CPU or, under the control of the CPU, from memory, and makes the destination address data available to the bus selection circuitry 24 over lines 60. The destination data is made available as a "slot mask" 61, at the bus selection circuitry 24. The slot mask (FIG. 1C) is a two byte word, in the illustrated embodiment, wherein a "one" bit represents a destination ("slot") address for the packet. A packet can have multiple destinations, in which case the slot mask has multiple bits set, each bit (of the two byte mask in the illustrated embodiment) representing a different destination. The slot mask is compared to existence maps in a slot existence map (a data map array) circuitry 62. The slot existence map indicates, for each destination node, which sub-buses can be used for the transfer of data between nodes.

Thus, the slot mask provides a bit position for each of the nodes connected to bus 14 (FIG. 1C); and for each sub-bus, the existence of a set bit in the existence map for that sub-bus indicates a receiver connection of that node to the sub-bus, while the absence of a set bit indicates the absence of an interface connection, for that destination node, to the sub-bus. As a result of the comparison, there are typically one or more sub-buses which can be used to transmit a data packet to the selected destination(s). From the set of available sub-buses provided by existence map circuitry 62, the bus selection circuitry 24 selects one sub-bus, at random in the illustrated embodiment, as the transmission carrier.

The bus selection circuitry also sends the packet destination slot mask to the speed selection circuitry 30. The speed selection circuitry 30 examines a stored speed map 64 to determine the maximum data rate at which the packet data can be sent to the selected destination(s). Thereafter, once the speed and the sub-bus have been determined, the information data is made available to the selected transmitter single packet DMA circuitry(s) and the data are sent over the sub-bus(es) by that transmit DMA circuitry(s) through its associated driver(s) 32 when control of the bus(es) has been made available to the associated transmit DMA (as described below). Thereafter the process is repeated for each successive packet to be transmitted.

In a particularly preferred embodiment of the invention, the CPU can designate a specific sub-bus to be employed in the transmission process thus bypassing the sub-bus selection circuitry 24 of the transmitter section.

At the receiver, each receiver single packet DMA circuitry 40 monitors all packets on its connected sub-bus. Whenever a packet is found to include the predetermined receiver slot number, specified by the destination slot mask in the packet header, a dequeue request is issued by the receiver circuitry 40 to the receiver dequeue/enqueue circuitry 46. The receiver dequeue/enqueue logic circuitry 46 then obtains a buffer, which is available from a pool of free buffers provided by the CPU, and the address of the buffer is sent to the requesting receiver DMA circuitry 40. The receiver DMA circuitry then DMA's the received packet directly into the designated buffer of memory. If the packet is received error-free, the buffer is made available to the receiver dequeue/enqueue circuitry 46 and is placed in a receiver queue at the CPU. If an error is detected, the receiver dequeue/enqueue circuitry places the allocated buffer back in the so-called "free" pool and the resulting data is effectively lost, and in not made available to the CPU. The operating system protocol handles a request for retransmittal of the packet.

In the operation of the circuitry of FIG. 1, several protocol rules are preferably observed for increasing the operational efficiency and hence throughput of the circuitry. First, all transmissions start at the highest speed at which all nodes connected to a sub-bus will correctly process the received information. Thus, all header information is transmitted at a speed which enables each node connected to the sub-bus to determine whether it is the intended destination of the packet. Once the header information has been transmitted, the transmission speed can be increased if and only if all destination nodes can read, as indicated by the speed selection circuitry 30, information transmitted at the higher rate. In the event that more than one destination node is specified, that is, if the header information indicates a plurality of receivers are receiving a packet (as noted above, this can be easily implemented by setting the appropriate slot bits in the slot masks for the plural nodes), then the maximum speed at which the information can be sent over the sub-bus is the highest speed at which all receivers can receive and properly process the information.

Once the data containing body of the packet has been transmitted, the transmitter, in the illustrated embodiment, sends an error check code which is processed by each of those receivers which were selected as destinations for the data. In the illustrated embodiment, since the error checking process is extremely complex and accordingly slow (at the receiver processing level), the transmitter slows the transmission rate to a low speed transmission which provides each receiver with adequate time to perform the necessary error checking process without an undue storage requirement at the receiving node.

Referring to the transmitter state diagram of FIG. 2, for an embodiment in which bus 14 is thirty-two bits wide with twelve control lines, and each sub-bus is eight bits wide with three control lines, the transmitter requires four clock cycles of the bus to send a thirty-two bit wide word. The transmitter, when it initiates operation, thus resides in state 100, in which it is IDLE. Upon the beginning of a packet transmission, the transmitter sets a bus request; enters state 102 at which it checks to see that the BUS GRANT signal (a sub-bus control line) is not asserted and that the FRAME signal (a sub-bus control line) also is not asserted (refer to FIGS. 6 and 7 for timing diagrams of the bus operation and bus arbitration according to a preferred embodiment of the invention).

The transmitter then proceeds to a no operation (NOP) state 104. Thereafter the BUS REQ signal is asserted and thereafter the BUS GRANT is asserted. The FRAME signal is set in state 106 if the FLOW control signal over lines 109 (FIG. 3) (a warning bus control signal connected to all nodes) is not asserted, and the first, upper byte of the first word to be sent is transmitted at state 108. If the FLOW control signal remains not asserted, a second upper byte of the word is transmitted at state 110, a third byte at state 112, and a fourth and last byte of the thirty-two bit word is transmitted at state 114. Thereafter, if the FLOW control signal is still not asserted and the data packet is not complete as indicated by a "NOT DONE" signal on an internal control line 115, the transmitter cycles back to send the beginning of the next thirty-two bit word of the packet at state 108. If the FLOW signal is not asserted and the packet data transmission is complete (DONE is asserted), the transmitter begins to send the first byte of the error correction code as indicated at state 116. Thereafter the successive bytes of the thirty-two bit error correction code are sent at states 118, 120, and 122. Finally, the FRAME signal is cleared (reset) at state 124 and the transmitter returns to its IDLE state 100.

Referring to FIG. 3, a typical transmitter structure receives the data over data lines 142 and synchronous with a clock signal over a sub-bus control line 140. The data passes through a thirty-two bit latch 144 which latches the data at each fourth clock time so long as the FLOW signal is not enabled. The output of latch 144 is input to a multiplexer 146 which, in response to the clock signals, passes one or the other of the high and low order sixteen bits of the stored thirty-two bit data word. The sixteen bit output of multiplexor 146 is held in a latch 148, controlled in the same manner as latch 144, and the two eight-bit outputs of latch 148 (high and low) are sequentially made available through multiplexer 150 to a third latch 152. The output of the third latch is made available to a sub-bus over a line 154 through a driver 32.

Timing for the transmitter data path is generated through the EXCLUSIVE-OR gate 156, and bistable flip flops 158. So long as the FLOW signal is not enabled, this circuitry divides by two with an output level change on line 160 every clock cycle, and shifted by one-half of a clock cycle to allow setting of the output data at the output of latch 152. The transmitter circuitry also includes a FRAME signal generation logic 162, responsive to the clock signal 140 and an initialization signal over a line 164 from the CPU for generating the FRAME control signal.

Referring now to FIG. 4, the receiver state diagram describes the operation of a receiver such as that illustrated schematically in FIG. 5. At the receiver, the start or initiation of operation begins at a FLUSH state 170. On the trailing edge of the FRAME signal, the receiver changes to a state 172 waiting there for the leading edge of the next FRAME signal. When the leading edge of the FRAME signal occurs (indicating the beginning of the next data packet), the receiver receives the first eight-bit byte from the channel over the sub-bus at state 174. For each successive level change of the timing signal, the receiver advances to a next state 176, 178, and either 180 or 170, as it reads each successive byte. After state 178, upon the next leading of the timing signal, the receiver either returns to the FLUSH state 170 which indicates that the packet slot bit was not set for that receiver and the packet should be ignored, or the receiver steps to state 180 because it recognizes that it is a destination for the incoming packet. At state 180, the receiver receives the entire packet and the end of the packet is indicated by the trailing edge of the FRAME signal, at which time, the receiver returns its normal IDLE state, state 172.

Referring to FIG. 5, a typical receiver data path provides for receiving eight bit wide data over lines 190. The eight bit data bytes pass through latches 192, 194 and 196 so that as each additional eight bits is received, the full thirty-two bit word is built up and is eventually stored in the latch 196 from which it is stored in a fifo buffer 198. The timing information is generated from the clock signal placed on the clock control line of the sub-bus by the transmitting node. Thus a level change occurs synchronously with the incoming data bytes and at the rate of the data byte transmission. At the first leading edge of the timing signal the first byte of a data word is stored in latch 192. At the following trailing edge of the timing pulse, that first byte of data is stored in the lower order eight bits of latch 194, and the second byte of data, available from lines 190, is stored in the upper eight bits of latch 194. Latch 196 does not operate because the enabling load signal from a flipflop 200 is not yet available. (Flipflop 200 in effect acts like a divide-by-two counter and accordingly enables a trailing edge of the timing signal only for every other trailing edge, corresponding to every fourth incoming data byte).

Upon the occurrence of the next leading edge of the timing signal on line 202, latch 192 again loads data into its register. This is the third byte of data in a four byte word. Upon the occurrence of the next trailing edge, latch 196 will operate, loading the two bytes of data from latch 194 into its lower half, and the upper two bytes of data from the output of latch 192 and the data lines 190 into its upper half. The full word is then made available to the receiver fifo buffer 198.

The operation of the circuitry associated with flipflop 200, which is enabled by the FRAME signal, is well known as a divide-by-two register. Accordingly, its operation in causing latch 196 to load only on every other trailing edge is well known to those of ordinary skill in the art.

In addition, the logic of the receiver FIFO buffer 198, asserts the FLOW signal to prevent the FIFO buffer from overflowing in the event that the receiver FIFO buffer 198 is getting too full . Separately, an error (interrupt) line (not shown) is asserted if a CRC error occurs. A slot recognition circuit 222 is responsive to the output of latch 194, the timing signal, and the FRAME signal for recognizing, by a signal over a line 224 that the incoming packet is intended for this node.

Referring now to FIGS. 6 and 7, the timing of the control signals available over the sub-bus was described generally in connection with the hardware of the transmitter and receiver circuitries. Once a transmitter has obtained access to the bus, it asserts the FRAME signal over line 206 which then "alerts" each of the connected receivers that a new data packet is forthcoming. The timing signals, applied at a slow rate with regard to the header, are applied to the clock control line 160 of the bus and provides the timing for the received signal over line 202. As shown on the data line 300 of FIG. 6, the initial data (the header) is provided at a relatively slow rate, the intermediate data information is provided at a fast rate, and the error control, (the CRC checksum in the illustrated embodiment) is provided at a slow rate. The timing signal, line 302, corresponds to the clock rate as described above. If, at any time, the receiver falls behind, the receiver asserts the FLOW line 304 which causes the transmitter to stop transmission. If the FLOW line is asserted for less than a predetermined time, (corresponding to the receiver "catching up"), the receiver can negate the FLOW assertion and the transmitter will then continue to transmit data. (If the transmitter detects a FLOW assertion for more than this minimum period of time, the transmitter will ignore the FLOW signal and may thus overrun the receiver input FIFO buffer 198. If the receiver detects this buffer state, an overflow error occurs at the receiver.)

Referring now to FIG. 7, the bus arbitration strategy for the illustrated embodiment of the invention provides that a transmitter, which has information to transmit, asserts a BUS REQ signal 310 to a bus arbitration circuitry (not shown). Each node is connected directly to the arbitration circuitry in the illustrated embodiment, by two signal lines, a BUS REQ line and a BUS GRANT line. During an ongoing packet transmission, the bus arbitration circuitry examines the BUS REQ lines from all nodes and selects one requesting node at random, in this illustrated embodiment, and asserts a BUS GRANT line 314 to that node. The BUS GRANT signal will enable the transmitter to raise the FRAME signal 320 (after that control signal is lowered by the presently transmitting node, as illustrated in FIG. 7) and proceed to transmit data. During transmission, the BUS REQ signal is cleared by the transmitting node (as illustrated at 108 in FIG. 2), and accordingly the BUS GRANT signal to the node is also cleared to its unasserted state. A next BUS REQ signal is then acknowledged by the arbitration circuitry.

In accordance with this particular embodiment of the invention, a data transfer mechanism is used wherein the data bus is divided into a plurality of independent sub-buses and each sub-bus operates "on its own" at all times. Each sub-bus, however, can act to "cover" for a failed sub-bus thus enabling, if the node has the appropriate connection, reliable communications to be achieved even when part of the bus channel is inoperative. Normally, however, all buses operate, and the memory access time requirements are minimized, enabling less expensive memory to be employed even though the full bus operates at a substantially higher transfer rate.

Additions, subtractions, deletions, and other modifications of the invention will be apparent to those practiced in the art, and are within the scope of the following claims.

Claims (25)

1. A method for transmitting data between a plurality of nodes of a communications network, each node having a maximum speed for receiving data words, said plurality of nodes connected on a communication bus having a bus width at least equal to a data word within a data packet, and comprising a plurality of bus subsets of bus lines connecting the plurality of nodes, the plurality of bus subsets in aggregate comprising the communication bus, the method comprising the steps of

determining, at a transmitting node, at least one of said plurality of bus subsets over which the transmitting node can communicate with an intended destination node receiving said data,

selecting, at the transmitting node, a speed at which to send said data words, within a range of the maximum speeds which said nodes can receive data words, based on a highest maximum speed at which only nodes acceptably determined to communicate with said transmitting node can receive said data words,

sending each data word within said data packet as a sequence of multibit subwords over said at least one of said plurality of bus subsets selected from said plurality of bus subsets acceptably determined to communicate with said transmitting node.

2. The method of claim 1 further comprising the steps of

appending as a header to said data words, a sequence of destination node identification symbols, and

appending, at the end of said sequence of data words error checking information data, said destination node, using the error information data to determine that said data words are received without error.

3. The method of claim 2 further comprising the step of

sending said error checking information data at a bus speed slower than the highest maximum speed at which the data words are sent, said error checking information readable by all nodes connected to the selected bus subset.

4. The method of claim 2 further comprising the steps of

forming a multibyte word for inclusion in said header, each node connected to a bus subset corresponding to a selected bit of said multibyte word, and

setting, at the transmitter, at least one bit of said multibyte word, for designating destination nodes for receiving a data packet to be transmitted.

5. The method of claim 1 further comprising the step of

said destination node, sending over a bus subset control line, during a data transmission of said data packet, a warning signal for informing the transmitting node of an overflow condition at the destination node.

6. The method of claim 1 further comprising the step of

sending all header information at a bus speed slower than the highest maximum speed at which the data words are sent, said header information readable by all nodes connected to a selected bus subset.

7. The method of claim 1 further comprising the steps of

stopping transmission of said data packet upon receipt of said warning signal, and

restarting transmission of said stopped data packet when said warning signal is removed from an overflow control line within a predetermined period of time.

8. The method of claim 1 wherein said sending step further comprises the step of

randomly selecting, from those acceptably determined bus subsets, the bus subset to be used for transmitting said data.

9. The method of claim 1 wherein

each node transmits data to said intended destination node over at least two subsets of said bus lines.

10. The method of claim 1 wherein said transmitting node communicates with a plurality of destination nodes over the selected bus subset.

11. The method of claim 1 wherein said transmitting node communicates with a plurality of destination nodes, each communication over different bus subsets.

12. The method of claim 1 wherein one of said plurality of bus subsets is substituted for an inoperative one of said plurality of bus subsets.

13. The method of claim 1 further comprising the step of

said transmitting node, prior to data transmission, sending over a bus subset control line, a bus request signal to bus arbitration circuitry and,

said transmitting node, upon receiving a bus grant signal from said bus arbitration circuitry and an indication that the bus subset is not busy, transmitting said data to said intended destination node.

14. The method of claim 1 further comprising the steps of

at initialization of the communications network, determining, at a transmitting node, the plurality of nodes connected to said communication bus,

determining and storing the maximum speeds which each of said plurality of nodes can receive said data words.

15. Apparatus for transmitting data between a plurality of nodes of a communications network, each node having a maximum speed for receiving data words, said plurality of nodes connected on a communication bus, said bus having a bus width at least equal to a data word within a data packet, comprising

a plurality of bus subsets of bus lines in aggregate comprising the communication bus,

means for determining, at a transmitting node, at least one of said plurality of bus subsets over which the transmitting node can communicate with an intended destination node receiving said data,

means for selecting, at the transmitting node, a speed at which to send said data words, within a range of the maximum speeds which said nodes can receive data words, based on a highest maximum speed at which only nodes acceptably determined to communicate with said transmitting node can receive said data words, and

means for sending each data word within said data packet as a sequence of multibit subwords over said at least one of said bus subset selected from said plurality of bus subsets acceptably determined to communicate with said transmitting node.

16. The apparatus of claim 15 further comprising

means for appending as a header to said data words, a sequence of destination node identification symbols, and

means for appending, at the end of said sequence of data words, error checking information data, a destination node, using the error information data to determine that said data words are received without error.

17. The apparatus of claim 16 further comprising

means for forming a multibyte word for inclusion in said header, each node connected to a bus subset corresponding to a selected bit of said multibyte word, and

means for setting, at the transmitter, at least one bit of said multibyte word, for designating destination nodes for receiving a data packet to be transmitted.

18. The apparatus of claim 16 wherein said sending means further comprises

means for randomly selecting, from those acceptable determined bus subsets, the bus subset to be used for transmitting said data.

19. The apparatus of claim 15 further comprising

means for sending, from the destination node during a data transmission of said data packet, a warning signal for informing the transmitting node of an overflow condition at the destination node.

20. The apparatus of claim 19 further comprising

means for stopping transmission of said data packet upon receipt of said warning signal, and

means for restarting transmission of said stopped data packet when said warning signal is removed from an overflow control line within a predetermined period of time.

21. The apparatus of claim 15 further comprising

means for sending all header information at a bus speed slower than the highest maximum speed at which the data words are sent, said header information readable by all nodes connected to the bus subset.

22. The apparatus of claim 21 further comprising

means for sending said error checking information data at said bus speed slower than the highest maximum speed at which the data words are sent said error checking information readable by all nodes connected to the selected bus subset.

23. The apparatus of claim 15 wherein said determining means comprises

means for selecting at least two subsets of said bus lines to communicate with said intended destination node.

24. The apparatus of claim 15 further comprising

means for sending, prior to data transmission, a bus request signal to bus arbitration circuitry over a bus subset control line, and

means for transmitting said data to said intended destination node upon receiving a bus grant signal from said bus arbitration circuitry and an indication that the bus subset is not busy.

25. The apparatus of claim 15 further comprising

means for determining, at initialization of the communications network, the plurality of nodes connected to said communication bus,

means for determining and storing the maximum speeds which each of said plurality of nodes can receive said data words.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US08/514,500 US5561771A (en) | 1991-10-04 | 1995-08-11 | System for transmitting data between systems using selected subsets of plural interconnecting bus lines and including selection of a compatible transmission speed |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US77174391A | 1991-10-04 | 1991-10-04 | |

| US08/161,208 US5442750A (en) | 1991-10-04 | 1993-12-02 | System for transmitting data between systems using selected subsets of plural interconnecting bus lines and including selection of a compatible transmission speed |

| US08/514,500 US5561771A (en) | 1991-10-04 | 1995-08-11 | System for transmitting data between systems using selected subsets of plural interconnecting bus lines and including selection of a compatible transmission speed |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US08/161,208 Continuation US5442750A (en) | 1991-10-04 | 1993-12-02 | System for transmitting data between systems using selected subsets of plural interconnecting bus lines and including selection of a compatible transmission speed |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| US5561771A true US5561771A (en) | 1996-10-01 |

Family

ID=25092836

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US08/161,208 Expired - Lifetime US5442750A (en) | 1991-10-04 | 1993-12-02 | System for transmitting data between systems using selected subsets of plural interconnecting bus lines and including selection of a compatible transmission speed |

| US08/514,500 Expired - Fee Related US5561771A (en) | 1991-10-04 | 1995-08-11 | System for transmitting data between systems using selected subsets of plural interconnecting bus lines and including selection of a compatible transmission speed |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US08/161,208 Expired - Lifetime US5442750A (en) | 1991-10-04 | 1993-12-02 | System for transmitting data between systems using selected subsets of plural interconnecting bus lines and including selection of a compatible transmission speed |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US5442750A (en) |

| EP (1) | EP0606299B1 (en) |

| JP (1) | JP3340738B2 (en) |

| AU (1) | AU2656892A (en) |

| DE (1) | DE69233194T2 (en) |

| WO (1) | WO1993007569A1 (en) |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5675735A (en) * | 1994-06-29 | 1997-10-07 | Digital Equipment Corporation | Method and apparatus for interconnecting network devices in a networking hub |

| US5734843A (en) * | 1995-06-07 | 1998-03-31 | Advanced Micro Devices Inc. | Reverse data channel as a bandwidth modulator |

| US5812798A (en) * | 1996-01-26 | 1998-09-22 | Motorola, Inc. | Data processing system for accessing an external device and method therefore |

| US5938731A (en) * | 1997-06-23 | 1999-08-17 | International Business Machines Corporation | Exchanging synchronous data link control (SDLC) frames to adjust speed of data transfer between a client and server |

| US5959998A (en) * | 1996-04-09 | 1999-09-28 | Fujitsu Limited | Channel selection method for an ISDN line and an ISDN switching system therefor |

| EP1176778A1 (en) * | 2000-07-29 | 2002-01-30 | Micronas GmbH | Data transmission method |

| US6453351B1 (en) * | 1993-09-13 | 2002-09-17 | Hitachi, Ltd. | Traffic control method and network control system |

| US6728810B1 (en) * | 1999-05-27 | 2004-04-27 | Kabushiki Kaisha Toshiba | Data processing apparatus and bus control method therefor |

| US7573916B1 (en) * | 1999-06-25 | 2009-08-11 | Cisco Technology, Inc. | Multi-function high-speed network interface |

| US8601178B2 (en) * | 2006-06-13 | 2013-12-03 | International Business Machines Corporation | Dynamic stabilization for a stream processing system |

Families Citing this family (31)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5396654A (en) * | 1992-09-04 | 1995-03-07 | Motorola Inc. | Data transfer method and apparatus having dual frequency operation |

| FR2706650B1 (en) * | 1993-06-11 | 1995-08-04 | Renault | Method for decoding the header of a communication message. |

| US5509006A (en) * | 1994-04-18 | 1996-04-16 | Cisco Systems Incorporated | Apparatus and method for switching packets using tree memory |

| US5519704A (en) * | 1994-04-21 | 1996-05-21 | Cisco Systems, Inc. | Reliable transport protocol for internetwork routing |

| GB9408321D0 (en) * | 1994-04-27 | 1994-06-15 | Philips Electronics Uk Ltd | Selective call system and a secondary station for use therein |

| US5684956A (en) * | 1994-11-14 | 1997-11-04 | Billings; Roger E. | Data transmission system with parallel packet delivery |

| US6226687B1 (en) * | 1996-09-05 | 2001-05-01 | Nortel Networks Limited | Method and apparatus for maintaining an order of data packets |

| US6047113A (en) * | 1996-12-10 | 2000-04-04 | International Business Machines Corporation | Network adapters for multi-speed transmissions |

| AU757557B2 (en) | 1997-11-13 | 2003-02-27 | Intellectual Ventures I Llc | File transfer system |

| US6430196B1 (en) | 1998-05-01 | 2002-08-06 | Cisco Technology, Inc. | Transmitting delay sensitive information over IP over frame relay |

| US6917982B1 (en) * | 1998-12-19 | 2005-07-12 | International Business Machines Corporation | Method and system for controlling package-oriented network traffic |

| US6771642B1 (en) | 1999-01-08 | 2004-08-03 | Cisco Technology, Inc. | Method and apparatus for scheduling packets in a packet switch |

| GB2351884B (en) | 1999-04-10 | 2002-07-31 | Peter Strong | Data transmission method |

| DE19948099A1 (en) * | 1999-10-06 | 2001-04-19 | Infineon Technologies Ag | Processor system, in particular a processor system for communication devices |

| US6718282B1 (en) | 1999-10-20 | 2004-04-06 | Cisco Technology, Inc. | Fault tolerant client-server environment |

| US6816910B1 (en) * | 2000-02-17 | 2004-11-09 | Netzentry, Inc. | Method and apparatus for limiting network connection resources |

| JP4436960B2 (en) * | 2000-05-16 | 2010-03-24 | 日本電気株式会社 | Packet communication system and mobile communication system |

| US6850980B1 (en) | 2000-06-16 | 2005-02-01 | Cisco Technology, Inc. | Content routing service protocol |

| WO2003009533A1 (en) * | 2001-07-11 | 2003-01-30 | Fujitsu Limited | Interface device and method of control thereof |

| US7331060B1 (en) | 2001-09-10 | 2008-02-12 | Xangati, Inc. | Dynamic DoS flooding protection |

| US20050152397A1 (en) * | 2001-09-27 | 2005-07-14 | Junfeng Bai | Communication system and techniques for transmission from source to destination |

| US7218610B2 (en) | 2001-09-27 | 2007-05-15 | Eg Technology, Inc. | Communication system and techniques for transmission from source to destination |

| CA2487384C (en) * | 2002-05-24 | 2009-12-22 | Baker Hughes Incorporated | A method and apparatus for high speed data dumping and communication for a downhole tool |

| US7620986B1 (en) | 2004-06-14 | 2009-11-17 | Xangati, Inc. | Defenses against software attacks in distributed computing environments |

| CN101366181B (en) * | 2005-09-15 | 2012-08-08 | 美国亚德诺半导体公司 | High speed transmission system |

| US8199641B1 (en) | 2007-07-25 | 2012-06-12 | Xangati, Inc. | Parallel distributed network monitoring |

| US8639797B1 (en) | 2007-08-03 | 2014-01-28 | Xangati, Inc. | Network monitoring of behavior probability density |

| US8693319B2 (en) * | 2008-09-25 | 2014-04-08 | Intel Corporation | Scheme for avoiding deadlock in multi-ring interconnect, with additional application to congestion control |

| EP2427977A4 (en) * | 2009-05-06 | 2012-12-26 | Hewlett Packard Development Co | Bus-based scalable optical fabrics |

| US10992555B2 (en) | 2009-05-29 | 2021-04-27 | Virtual Instruments Worldwide, Inc. | Recording, replay, and sharing of live network monitoring views |

| US8625427B1 (en) | 2009-09-03 | 2014-01-07 | Brocade Communications Systems, Inc. | Multi-path switching with edge-to-edge flow control |

Citations (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4228496A (en) * | 1976-09-07 | 1980-10-14 | Tandem Computers Incorporated | Multiprocessor system |

| US4340775A (en) * | 1980-10-29 | 1982-07-20 | Siemens Corporation | Apparatus and method for controlling a modular telecommunication system |

| US4539637A (en) * | 1982-08-26 | 1985-09-03 | At&T Bell Laboratories | Method and apparatus for handling interprocessor calls in a multiprocessor system |

| US4577312A (en) * | 1984-07-05 | 1986-03-18 | At&T Bell Laboratories | Arrangement for wideband transmission via a switched network |

| US4584679A (en) * | 1983-01-21 | 1986-04-22 | E-Systems, Inc. | Tack-on acknowledgement in computer networks |

| US4598400A (en) * | 1983-05-31 | 1986-07-01 | Thinking Machines Corporation | Method and apparatus for routing message packets |

| US4703475A (en) * | 1985-12-04 | 1987-10-27 | American Telephone And Telegraph Company At&T Bell Laboratories | Data communication method and apparatus using multiple physical data links |

| US4805169A (en) * | 1985-03-01 | 1989-02-14 | Hollandse Signaalapparaten B.V. | Local area network operating on the multiple bus system |

| US4885738A (en) * | 1985-12-31 | 1989-12-05 | American Telephone And Telegraph Company, At&T Bell Laboratories | Method of and apparatus for establishing a wideband communication facility through a switched communications network having narrow bandwidth time division multiplexed channels |

| US4918689A (en) * | 1985-10-10 | 1990-04-17 | Bell Communications Research, Inc. | Asynchronous communication system |

| US4933838A (en) * | 1987-06-03 | 1990-06-12 | The Boeing Company | Segmentable parallel bus for multiprocessor computer systems |

| US5083260A (en) * | 1988-02-29 | 1992-01-21 | Pfu Limited | Bus arbitration system for concurrent use of a system bus by more than one device |

| US5109490A (en) * | 1989-01-13 | 1992-04-28 | International Business Machines Corporation | Data transfer using bus address lines |

| US5301303A (en) * | 1990-04-23 | 1994-04-05 | Chipcom Corporation | Communication system concentrator configurable to different access methods |

| US5497370A (en) * | 1988-11-16 | 1996-03-05 | Hitachi, Ltd. | Network system |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63276155A (en) * | 1987-05-07 | 1988-11-14 | Fujitsu Ltd | Bus multiple control system |

| JPH0242556A (en) * | 1988-08-03 | 1990-02-13 | Mitsubishi Electric Corp | Bus control system |

-

1992

- 1992-09-22 EP EP92920345A patent/EP0606299B1/en not_active Expired - Lifetime

- 1992-09-22 JP JP50692993A patent/JP3340738B2/en not_active Expired - Fee Related

- 1992-09-22 DE DE69233194T patent/DE69233194T2/en not_active Expired - Fee Related

- 1992-09-22 AU AU26568/92A patent/AU2656892A/en not_active Abandoned

- 1992-09-22 WO PCT/US1992/007941 patent/WO1993007569A1/en active IP Right Grant

-

1993

- 1993-12-02 US US08/161,208 patent/US5442750A/en not_active Expired - Lifetime

-

1995

- 1995-08-11 US US08/514,500 patent/US5561771A/en not_active Expired - Fee Related

Patent Citations (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4228496A (en) * | 1976-09-07 | 1980-10-14 | Tandem Computers Incorporated | Multiprocessor system |

| US4340775A (en) * | 1980-10-29 | 1982-07-20 | Siemens Corporation | Apparatus and method for controlling a modular telecommunication system |

| US4539637A (en) * | 1982-08-26 | 1985-09-03 | At&T Bell Laboratories | Method and apparatus for handling interprocessor calls in a multiprocessor system |

| US4584679A (en) * | 1983-01-21 | 1986-04-22 | E-Systems, Inc. | Tack-on acknowledgement in computer networks |

| US4598400A (en) * | 1983-05-31 | 1986-07-01 | Thinking Machines Corporation | Method and apparatus for routing message packets |

| US4577312A (en) * | 1984-07-05 | 1986-03-18 | At&T Bell Laboratories | Arrangement for wideband transmission via a switched network |

| US4805169A (en) * | 1985-03-01 | 1989-02-14 | Hollandse Signaalapparaten B.V. | Local area network operating on the multiple bus system |

| US4918689A (en) * | 1985-10-10 | 1990-04-17 | Bell Communications Research, Inc. | Asynchronous communication system |

| US4703475A (en) * | 1985-12-04 | 1987-10-27 | American Telephone And Telegraph Company At&T Bell Laboratories | Data communication method and apparatus using multiple physical data links |

| US4885738A (en) * | 1985-12-31 | 1989-12-05 | American Telephone And Telegraph Company, At&T Bell Laboratories | Method of and apparatus for establishing a wideband communication facility through a switched communications network having narrow bandwidth time division multiplexed channels |

| US4933838A (en) * | 1987-06-03 | 1990-06-12 | The Boeing Company | Segmentable parallel bus for multiprocessor computer systems |

| US5083260A (en) * | 1988-02-29 | 1992-01-21 | Pfu Limited | Bus arbitration system for concurrent use of a system bus by more than one device |

| US5497370A (en) * | 1988-11-16 | 1996-03-05 | Hitachi, Ltd. | Network system |

| US5109490A (en) * | 1989-01-13 | 1992-04-28 | International Business Machines Corporation | Data transfer using bus address lines |

| US5301303A (en) * | 1990-04-23 | 1994-04-05 | Chipcom Corporation | Communication system concentrator configurable to different access methods |

Cited By (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6453351B1 (en) * | 1993-09-13 | 2002-09-17 | Hitachi, Ltd. | Traffic control method and network control system |

| US5675735A (en) * | 1994-06-29 | 1997-10-07 | Digital Equipment Corporation | Method and apparatus for interconnecting network devices in a networking hub |

| US5809253A (en) * | 1994-06-29 | 1998-09-15 | Cabletron Systems, Inc. | Method and apparatus for interconnecting network devices in a networking hub |

| US5923851A (en) * | 1994-06-29 | 1999-07-13 | Cabletron Systems, Inc. | Method and apparatus for interconnecting network devices in a networking hub |

| US5734843A (en) * | 1995-06-07 | 1998-03-31 | Advanced Micro Devices Inc. | Reverse data channel as a bandwidth modulator |

| US5812798A (en) * | 1996-01-26 | 1998-09-22 | Motorola, Inc. | Data processing system for accessing an external device and method therefore |

| US5959998A (en) * | 1996-04-09 | 1999-09-28 | Fujitsu Limited | Channel selection method for an ISDN line and an ISDN switching system therefor |

| US5938731A (en) * | 1997-06-23 | 1999-08-17 | International Business Machines Corporation | Exchanging synchronous data link control (SDLC) frames to adjust speed of data transfer between a client and server |

| US6728810B1 (en) * | 1999-05-27 | 2004-04-27 | Kabushiki Kaisha Toshiba | Data processing apparatus and bus control method therefor |

| US7573916B1 (en) * | 1999-06-25 | 2009-08-11 | Cisco Technology, Inc. | Multi-function high-speed network interface |

| EP1176778A1 (en) * | 2000-07-29 | 2002-01-30 | Micronas GmbH | Data transmission method |

| US20020150077A1 (en) * | 2000-07-29 | 2002-10-17 | Miodrag Temerinac | Data transmission method |

| US8601178B2 (en) * | 2006-06-13 | 2013-12-03 | International Business Machines Corporation | Dynamic stabilization for a stream processing system |

Also Published As

| Publication number | Publication date |

|---|---|

| DE69233194T2 (en) | 2004-06-09 |

| DE69233194D1 (en) | 2003-10-16 |

| EP0606299A1 (en) | 1994-07-20 |

| JPH06511338A (en) | 1994-12-15 |

| US5442750A (en) | 1995-08-15 |

| AU2656892A (en) | 1993-05-03 |

| WO1993007569A1 (en) | 1993-04-15 |

| JP3340738B2 (en) | 2002-11-05 |

| EP0606299B1 (en) | 2003-09-10 |

| EP0606299A4 (en) | 1996-05-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|